Puente Sur (informática)

El puente sur es uno de los dos chips del conjunto de chips lógico central de la placa base de una computadora personal (PC), siendo el otro el puente norte. El puente sur normalmente implementa las capacidades más lentas de la placa base en una arquitectura de computadora con chipset puente norte/puente sur. En sistemas con chipsets Intel, el puente sur se llama I/O Controller Hub (ICH), mientras que AMD ha llamado a su puente sur Fusion Controller Hub (FCH) desde la introducción de su Unidad de procesamiento acelerado (APU) Fusion mientras traslada las funciones del Northbridge. en la matriz de la CPU, lo que lo hace similar en función al controlador del concentrador de plataforma.

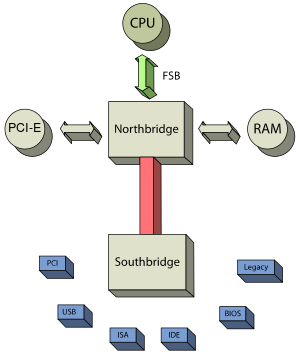

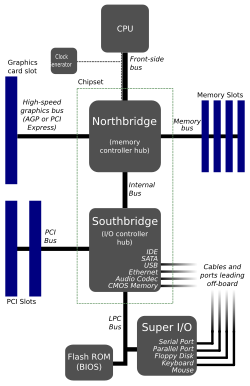

El puente sur generalmente se puede distinguir del puente norte porque no está conectado directamente a la CPU. Más bien, el puente norte une el puente sur a la CPU. Mediante el uso de circuitos de canal integrados del controlador, el puente norte puede vincular directamente señales desde las unidades de E/S a la CPU para control y acceso a los datos.

Estado actual

Debido al impulso de los procesadores de sistema en chip (SoC), los dispositivos modernos tienen cada vez más el puente norte integrado en la propia CPU; ejemplos son los procesadores Sandy Bridge de Intel y Fusion de AMD, ambos lanzados en 2011. El puente sur se volvió redundante y fue reemplazado por la arquitectura Platform Controller Hub (PCH) introducida con el chipset Intel Serie 5 en 2008, mientras AMD hizo lo mismo con el lanzamiento de sus primeras APU en 2011, nombrando al PCH Fusion Controller Hub (FCH), que solo se usó en las APU de AMD hasta 2017, cuando comenzó a usarse en las APU de AMD. Arquitectura Zen dejando caer el nombre FCH. En las plataformas Intel, todas las funciones de Southbridge y las funciones de E/S restantes son administradas por el PCH que está conectado directamente a la CPU a través de la interfaz de medios directa (DMI). El procesador Intel de bajo consumo (Haswell-U y posteriores) y el procesador de consumo ultrabajo (Haswell-Y y posteriores) también integraron un PCH en el paquete. Basado en su diseño Chiplet, los procesadores AMD Ryzen también integraron algunas funciones de puente sur, como algunas interfaces USB y algunas interfaces SATA/NVMe.

Descripción general

Un chipset Southbridge manejaba muchas de las funciones de E/S de una computadora, como USB, audio, el BIOS del sistema, el bus ISA o el bus LPC, el bus PCI/PCIe de baja velocidad, el controlador de interrupciones IOAPIC, el almacenamiento SATA, el almacenamiento PATA histórico y el almacenamiento NVMe. Son posibles diferentes combinaciones de chips Southbridge y Northbridge, pero estos dos tipos de chips deben diseñarse para funcionar juntos; No existe un estándar en toda la industria para la interoperabilidad entre diferentes diseños de conjuntos de chips lógicos centrales. En la década de 1990 y principios de la de 2000, la interfaz entre un puente norte y un puente sur era el bus PCI. A partir de 2023, las principales interfaces puente utilizadas son Ultra Path Interconnect (Intel) y PCI Express (AMD).

Etimología

El nombre se deriva de la representación de la arquitectura en forma de mapa y se describió como tal por primera vez con la introducción de la arquitectura de bus local PCI en 1991. En Intel, los autores de la especificación PCI consideraban el bus local PCI como estar en el centro mismo de la arquitectura de la plataforma de PC (es decir, en el ecuador).

El puente norte se extiende hacia el norte de la red troncal del bus PCI para admitir CPU, memoria/caché y otras capacidades críticas para el rendimiento. Del mismo modo, el puente sur se extiende hacia el sur de la red troncal del bus PCI y conecta capacidades de E/S menos críticas para el rendimiento, como la interfaz de disco, audio, etc.

La CPU está ubicada en la parte superior del mapa, hacia el norte. La CPU está conectada al chipset a través de un puente rápido (el puente norte) ubicado al norte de otros dispositivos del sistema como se muestra. El puente norte está conectado al resto del chipset a través de un puente lento (el puente sur) ubicado al sur de otros dispositivos del sistema como se muestra.

Aunque la arquitectura actual de la plataforma de PC ha reemplazado la red troncal del bus PCI con redes troncales de E/S más rápidas, la convención de nomenclatura del puente permanece.

Funcionalidad

La funcionalidad que se encuentra en un puente sur contemporáneo incluye:

- Autobús PCI. Un puente sur también puede incluir soporte para PCI-X.

- Interfaces PCI Express de baja velocidad (PCIe) generalmente para Ethernet y NVMe.

- Autobús ISA o puente LPC. Las ranuras ISA ya no se proporcionan en placas madre más recientes. El puente LPC proporciona una ruta de datos y control al super I/O (el accesorio normal para el teclado PS/2 y el ratón, puerto paralelo, puerto serie, puerto IR y controlador de disquete).

- Bus SPI. El bus SPI es un simple bus serie utilizado principalmente para el firmware (por ejemplo, BIOS/UEFI) acceso de almacenamiento flash.

- Controlador SMBus.

- Controlador DMA. El controlador 8237 DMA permite que los dispositivos ISA o LPC tengan acceso directo a la memoria principal sin necesidad de ayuda de la CPU.

- PIC y I/O APIC.

- Interfaz de almacenamiento masivo como SATA, M.2 y PATA histórica. Esto normalmente permite el accesorio de discos duros o SSD.

- Reloj en tiempo real.

- Temporizador de intervalo programable.

- Temporizador de eventos de alta precisión.

- Controlador ACPI o controlador APM.

- Memoria BIOS no volátil. El sistema CMOS (Recuerdo de configuración de BIOS), asistido por energía suplementaria de batería, crea un área de almacenamiento no volátil limitado para los datos de configuración de BIOS.

- Intel HD Audio o AC'97 interfaz de sonido.

- Interfaz USB.

Opcionalmente, un puente sur también incluye soporte (chip discreto incorporado o integrado en el puente sur) para Ethernet, Wi-Fi, RAID, Thunderbolt y administración fuera de banda.

Contenido relacionado

Tarjeta perforada

CPython

Arquitectura Harvard