Arquitectura Harvard

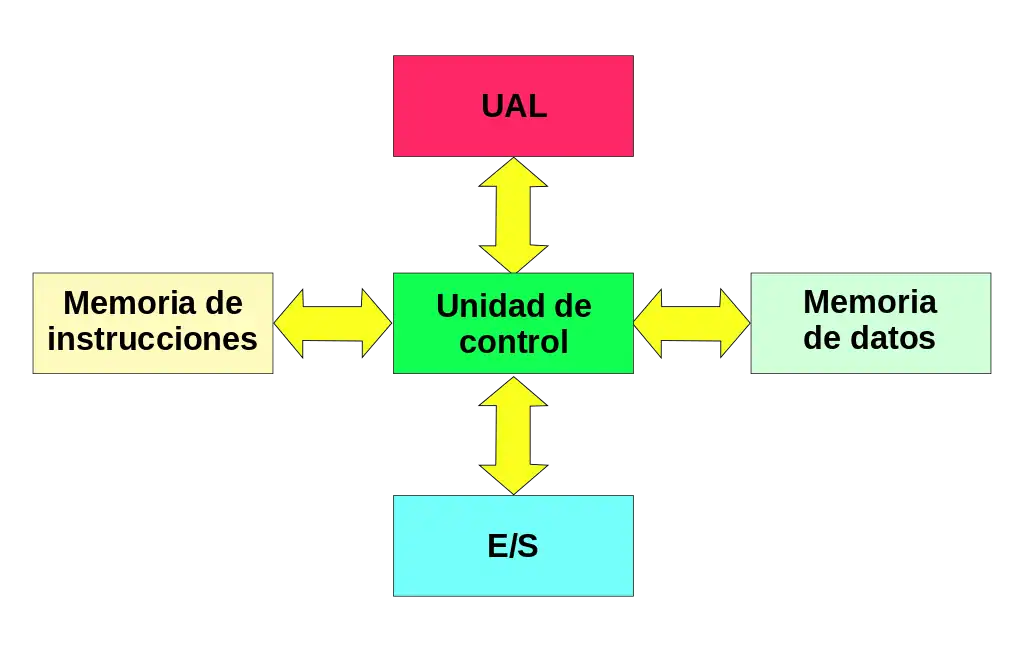

La Arquitectura Harvard es un modelo de arquitectura informática que separa físicamente la memoria de código de programa de la memoria de almacenamiento de datos. Cada una de estas memorias se conecta por separado al procesador, y tiene su propio bus de datos, lo cual permite una mayor eficiencia del procesamiento de datos. Este modelo de arquitectura se contrapone al modelo de von Neumann, que no distingue físicamente la memoria y procesamiento del código y de los datos, lo cual genera cuellos de botella en el acceso a la memoria.

Su nombre, se debe a la computadora Harvard Mark I, basada en relés, que diferenciaba físicamente el almacenamiento de instrucciones, en una cinta perforada de 24 bits, del almacenamiento de datos, en contadores electromecánicos. Esta separación mejoró significativamente la velocidad de procesamiento de la Mark I. Antes, las primeras computadoras tenían tanto los datos, como las instrucciones, dentro de la misma unidad central de procesamiento, requiriendo que los programas fuesen cargados manualmente por un operador, ya que la máquina no podía reiniciar su estado de procesamiento.

En la actualidad, aunque la mayoría de los sistemas a simple vista parecieran seguir el modelo de von Neumann al almacenar código y datos en una misma memoria principal por razones de eficiencia, internamente adoptan una estrategia similar a la arquitectura Harvard. Utilizan memorias caché separadas para instrucciones y datos, con vías de acceso independientes al procesador. Esta modificación se conoce como Arquitectura Harvard Modificada, y permite acceder a los contenidos de la memoria de instrucciones como si fueran datos, aumentando la flexibilidad del sistema.

Aunque tradicionalmente la arquitectura Harvard se asocia con la separación en dos espacios de direcciones para código y datos, existen variantes más complejas que incorporan tres o más espacios, aunque son menos comunes.

La Arquitectura Harvard se usa en la mayoría de sistemas especializados, como dispositivos móviles, sistemas integrados, microcontroladores. Es el componente principal de los DSP (procesamiento de señales digitales), normalmente para productos de transformación de audio y vídeo. También se usa en muchos microcontroladores pequeños utilizados en aplicaciones electrónicas, como los procesadores ARM (del inglés Advanced RISC Machine) que son la base de muchos fabricantes.

HSD

Arquitectura de Harvard Modificada

La Arquitectura de Harvard Modificada es una variante de la Arquitectura de Harvard que permite que el contenido de la memoria de programa sea accesado como si fuera memoria de datos. Esta es la principal diferencia entre las dos arquitecturas. Casi todos los computadores personales modernos poseen Arquitectura de Harvard Modificada.

Ejemplos de la Arquitectura de Harvard Modificada:

- Acceso de lectura - los valores de datos iniciales pueden ser copiados de la memoria de instrucciones a la memoria de datos cuando un programa se inicia.

- Acceso de escritura - la capacidad de reprogramar es generalmente requerida; muy pocos computadores son meramente memoria solo de lectura (ROM) basados. Por ejemplo: un microcontrolador, típicamente, tiene la capacidad de escribir en la memoria flash, que se usa para mantener sus instrucciones.

Detalles de la memoria

En una arquitectura Harvard, no hay necesidad de hacer que las dos memorias compartan características. En particular, el ancho de palabra, el tiempo, la tecnología de implementación y la estructura de direcciones de memoria pueden diferir. En algunos sistemas, las instrucciones para tareas preprogramadas se pueden almacenar en la memoria de solo lectura, mientras que la memoria de datos generalmente requiere memoria de lectura y escritura. En algunos sistemas, hay mucha más memoria de instrucciones que memoria de datos, por lo que las direcciones de instrucciones son más anchas que las direcciones de datos.

Diferencias con la Arquitectura de von Neumann

En un sistema con una arquitectura de von Neumann pura, las instrucciones y los datos se almacenan en la misma memoria, por lo que las instrucciones se obtienen a través de la misma ruta de datos utilizada para obtener los datos. Esto significa que una CPU no puede leer simultáneamente una instrucción y leer o escribir datos desde o hacia la memoria. En una computadora que utiliza la arquitectura Harvard, la CPU puede leer una instrucción y realizar un acceso a la memoria de datos al mismo tiempo, incluso sin caché. Por lo tanto, una computadora con arquitectura Harvard puede ser más rápida para una complejidad de circuito determinada porque las búsquedas de instrucciones y el acceso a datos no compiten por una sola ruta de memoria.

Además, una máquina con arquitectura Harvard tiene códigos distintos y espacios de dirección de datos: la dirección de instrucción cero no es lo mismo que la dirección de datos cero. La dirección de instrucción cero podría identificar un valor de veinticuatro bits, mientras que la dirección de datos cero podría indicar un byte de ocho bits que no forma parte de ese valor de veinticuatro bits.

Diferencias con la Arquitectura Harvard Modificada

Una máquina con arquitectura Harvard modificada es muy parecida a una máquina con arquitectura Harvard, pero relaja la separación estricta entre instrucciones y datos, al mismo tiempo que permite que la CPU acceda simultáneamente a dos (o más) buses de memoria. La modificación más común incluye cachés de datos e instrucciones separadas respaldadas por un espacio de direcciones común. Si bien la CPU se ejecuta desde la memoria caché, actúa como una máquina Harvard pura. Al acceder a la memoria de respaldo, actúa como una máquina de von Neumann (donde el código se puede mover como si fueran datos, lo cual es una técnica poderosa). Esta modificación está muy extendida en los procesadores modernos, como la arquitectura ARM, Power ISA y los procesadores x86. A veces se le llama vagamente arquitectura de Harvard, pasando por alto el hecho de que en realidad está "modificada".

Otra modificación proporciona un camino entre la memoria de instrucciones (como ROM o memoria flash) y la CPU para permitir que las palabras de la memoria de instrucciones se traten como datos de solo lectura. Esta técnica se utiliza en algunos microcontroladores, incluido el Atmel AVR. Esto permite acceder a datos constantes, como cadenas de texto o tablas de funciones, sin tener que copiarlos primero en la memoria de datos, preservando la memoria de datos escasa (y que consume mucha energía) para las variables de lectura/escritura. Se proporcionan instrucciones especiales en lenguaje de máquina para leer datos de la memoria de instrucciones, o se puede acceder a la memoria de instrucciones mediante una interfaz periférica. (Esto es distinto de las instrucciones que en sí mismas incorporan datos constantes, aunque para las constantes individuales los dos mecanismos pueden sustituirse entre sí).

Velocidad de procesamiento

En los últimos años, la velocidad de la CPU ha crecido muchas veces en comparación con la velocidad de acceso a la memoria principal. Se debe tener cuidado para reducir la cantidad de veces que se accede a la memoria principal para mantener el rendimiento. Si, por ejemplo, cada instrucción que se ejecuta en la CPU requiere acceso a la memoria, la computadora no gana nada con el aumento de la velocidad de la CPU, un problema conocido como límite de memoria.

Es posible crear una memoria extremadamente rápida, pero esto solo es práctico para pequeñas cantidades de memoria por razones de costo, energía y enrutamiento de la señal. La solución es proporcionar una pequeña cantidad de memoria muy rápida conocida como caché de CPU que contiene los datos a los que se accedió recientemente. Siempre que los datos que necesita la CPU estén en la memoria caché, el rendimiento es mucho mayor que cuando la CPU tiene que obtener los datos de la memoria principal. Sin embargo, por otro lado, aún puede estar limitado a almacenar programas o datos repetitivos y aún tiene una limitación de tamaño de almacenamiento y otros problemas potenciales asociados con él.

Diferencias entre diseño interno y externo

Los diseños modernos de chips de CPU de alto rendimiento incorporan aspectos de la arquitectura Harvard y von Neumann. En particular, la "caché dividida" La versión modificada de la arquitectura de Harvard es muy común. La memoria caché de la CPU se divide en una caché de instrucciones y una caché de datos. La arquitectura Harvard se utiliza cuando la CPU accede a la memoria caché. Sin embargo, en el caso de una pérdida de caché, los datos se recuperan de la memoria principal, que no está formalmente dividida en secciones separadas de instrucciones y datos, aunque es posible que tenga controladores de memoria separados que se usen para el acceso simultáneo a RAM, ROM y (NOR).) memoria flash.

Por lo tanto, mientras que una arquitectura de von Neumann es visible en algunos contextos, como cuando los datos y el código pasan por el mismo controlador de memoria, la implementación del hardware obtiene la eficiencia de la arquitectura de Harvard para los accesos a la memoria caché y al menos algunos accesos a la memoria principal.

Además, las CPU a menudo tienen búferes de escritura que permiten que las CPU continúen después de escribir en regiones no almacenadas en caché. La naturaleza de von Neumann de la memoria es entonces visible cuando la CPU escribe las instrucciones como datos y el software debe garantizar que los cachés (datos e instrucciones) y el búfer de escritura estén sincronizados antes de intentar ejecutar esas instrucciones recién escritas.

Usos modernos de la Arquitectura Harvard

La principal ventaja de la arquitectura pura de Harvard (acceso simultáneo a más de un sistema de memoria) se ha reducido mediante procesadores Harvard modificados que utilizan sistemas modernos de caché de CPU. Las máquinas con arquitectura Harvard relativamente pura se utilizan principalmente en aplicaciones en las que las ventajas y desventajas, como el ahorro de costos y energía al omitir cachés, superan las penalizaciones de programación al presentar espacios de dirección de datos y códigos distintos.

- Los procesadores de señales digitales (DSPs) generalmente ejecutan pequeños algoritmos de procesamiento de audio o vídeo altamente optimizados. Evitan caches porque su comportamiento debe ser extremadamente reproducible. Las dificultades para hacer frente a múltiples espacios de dirección son de interés secundario para la velocidad de ejecución. En consecuencia, algunos DSP cuentan con múltiples memorias de datos en distintos espacios de dirección para facilitar el procesamiento SIMD y VLIW. Los procesadores TMS320 C55x de Texas Instruments, por ejemplo, cuentan con múltiples autobuses de datos paralelos (dos escriben, tres leen) y un bus de instrucción.

- Los microcontroladores se caracterizan por tener pequeñas cantidades de memoria del programa (recuperación de pestañas) y datos (SRAM), y aprovechar la arquitectura de Harvard para acelerar el procesamiento por instrucción simultánea y acceso a datos. El almacenamiento separado significa que el programa y los recuerdos de datos pueden tener diferentes anchos de bit, por ejemplo utilizando instrucciones de 16 bits y datos de 8 bits. También significan que la instrucción prefetch se puede realizar en paralelo con otras actividades. Ejemplos son el PIC de Microchip Technology, Inc. y el AVR de Atmel Corp (ahora parte de Microchip Technology).

Incluso en estos casos, es común emplear instrucciones especiales para acceder a la memoria del programa como si fueran datos para tablas de solo lectura o para reprogramación; esos procesadores son procesadores de arquitectura Harvard modificados.

Historia de la Arquitectura Harvard

Las raíces de la arquitectura Harvard se originan en la Universidad de Harvard con el proyecto del computador Harvard Mark I que fue creado entre 1937 a 1944, durante la Segunda Guerra Mundial, ideado por Howard Aiken con el apoyo de IBM y de la marina norteamericana fue considerado el primer proyecto de computadora. Utilizaba muchas válvulas, las operaciones internas eran controladas por relés y los cálculos eran realizados mecánicamente. Integraba conceptos de computadoras digitales y analógicas, pues tenía sistema electrónico y mecánico en la misma máquina.

H. Aiken, el investigador que desarrolló Mark I, construyó otras versiones de este computador. A pesar de haberse originado del Mark I, la arquitectura Harvard solo fue nuevamente impulsada a partir de la década de los 70 con la creación de circuitos integrados por diversas empresas del segmento como Signetics, que creó el dispositivo 8x300, intel con el 8048, General Instruments para uso como interfaz controladora de periféricos (PIC) que fue diseñada para compensar el débil bus de I/O de su CPU CP1600 de 16 bits.

La división de microelectrónica fue, luego, transformada en Arizona Microchip Technology (alrededor de 1985), con los PICs como su producto principal etc...

Antes de eso, la arquitectura Harvard había sido solo una curiosidad científica desde su invención por la Universidad de Harvard.

En una competencia creada por el Departamento de Defensa de los Estados Unidos que puso a Princeton contra Harvard, Princeton ganó la competencia porque el tiempo medio entre fallos (MTBF) de su arquitectura de memoria más simple era mucho mejor, aunque más lenta que la propuesta de Harvard. Con el desarrollo de los transistores y de los circuitos integrados, la arquitectura Harvard finalmente fue reconocida. Microchip hizo mejoras en la arquitectura original, y actualizó los bloques funcionales del proyecto original con avances modernos que están en compás con los procesos arquitectónicos existentes y habilitados por el bajo costo de los semiconductores.

Contenido relacionado

Tarjeta perforada

Carácter (informática)

Proceso (informática)