Motorola 68000

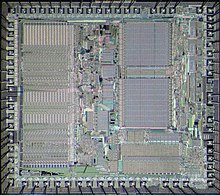

El Motorola 68000 (a veces abreviado como Motorola 68k o m68k y normalmente se pronuncia "sesenta y ocho mil") es un microprocesador de computadora con conjunto de instrucciones complejas (CISC) de 16/32 bits, introducido en 1979 por Motorola Semiconductor Products Sector.

El diseño implementa un conjunto de instrucciones de 32 bits, con registros de 32 bits y un bus de datos interno de 16 bits. El bus de direcciones es de 24 bits y no utiliza la segmentación de la memoria, lo que facilitó la programación. Internamente, utiliza una unidad lógica aritmética (ALU) de datos de 16 bits y dos ALU más de 16 bits que se utilizan principalmente para direcciones, y tiene un bus de datos externo de 16 bits. Por esta razón, Motorola lo denominó procesador de 16/32 bits.

Como uno de los primeros procesadores ampliamente disponibles con un conjunto de instrucciones de 32 bits, un gran espacio de direcciones no segmentado y una velocidad relativamente alta para la época, el 68k fue un diseño popular durante la década de 1980. Fue ampliamente utilizado en una nueva generación de computadoras personales con interfaces gráficas de usuario, incluidas Macintosh 128K, Amiga, Atari ST y X68000. La consola Sega Genesis/Mega Drive de 1988 funciona con un 68000.

Los procesadores posteriores de la serie Motorola 68000, comenzando con el Motorola 68020, usan ALU completas de 32 bits y tienen buses completos de dirección y datos de 32 bits. El 68k original es generalmente compatible con el software hacia adelante con el resto de la línea a pesar de estar limitado a un bus externo de 16 bits de ancho.

Después de 44 años en producción, la arquitectura 68000 todavía está en uso.

Desarrollo

6800

El primer microprocesador de gran producción de Motorola fue el 6800, presentado a principios de 1974 y disponible en grandes cantidades a fines de ese año. La empresa se fijó la meta de vender 25.000 unidades para septiembre de 1976, meta que cumplieron. Aunque era un diseño capaz, fue eclipsado por diseños más poderosos, como el Zilog Z80, y diseños menos costosos, como el MOS Technology 6502. A fines de 1976, el libro de ventas era plano y la división solo se salvó por un proyecto General Motors que se convirtió en una gran línea de productos para el control de motores y otras tareas.

Pasar a 16 bits

Cuando se introdujo el 6800, había llegado al mercado una pequeña cantidad de diseños de 16 bits. Estos generalmente se modelaron en plataformas de minicomputadoras como Data General Nova o PDP-8. Según los procesos de fabricación de semiconductores de la época, a menudo se trataba de soluciones de chips múltiples como el National Semiconductor IMP-16 o el PACE de un solo chip que tenía problemas con la velocidad.

Con las perspectivas de venta del 6800 atenuable, pero aún con flujo de caja de las ventas de control del motor, a fines de 1976 Colin Crook, Gerente de operaciones, comenzó a considerar cómo obtener ventas futuras con éxito. Sabían que Intel estaba trabajando en una extensión de 16 bits de su serie 8080, que emergería como Intel 8086, y habían escuchado rumores de un Zilog Z80 de 16 bits, que se convirtió en Z8000. Estos utilizarían nuevas técnicas de diseño que eliminarían los problemas observados en los sistemas anteriores de 16 bits.

Motorola sabía que si lanzaban un producto similar al 8086, dentro del 10 % de sus capacidades, Intel los mataría en el mercado. Para competir, se fijaron el objetivo de ser dos veces más potentes al mismo costo, o la mitad del costo con el mismo rendimiento. Crook decidió que atacarían la gama alta del mercado con el procesador más potente del mercado. Otro de 16 bits no serviría, su diseño tendría que ser más grande, y eso significaba tener algunas características de 32 bits. Crook se había decidido por este enfoque a fines de 1976.

MACSS

Crook formó el proyecto Motorola Advanced Computer System on Silicon (MACSS) para construir el diseño y contrató a Tom Gunter para que fuera su arquitecto principal. Gunter comenzó a formar su equipo en enero de 1977. El objetivo de rendimiento se fijó en 1 millón de instrucciones por segundo (MIPS). Querían que el diseño no solo recuperara a los proveedores de microcomputadoras como Apple Computer y Tandy, sino también a las compañías de minicomputadoras como NCR y AT&T.

El equipo decidió abandonar un intento de compatibilidad con versiones anteriores del 6800, ya que consideraban que los diseños de 8 bits eran demasiado limitados para ser la base de nuevos diseños. El nuevo sistema fue influenciado por el PDP-11, el diseño de minicomputadora más popular de la época. En ese momento, un concepto clave en minis era el concepto de un conjunto de instrucciones ortogonales, en el que cada operación podía funcionar en cualquier tipo de datos. Para introducir los datos correctos en las unidades internas, MACSS hizo un uso extensivo del microcódigo, esencialmente pequeños programas en memoria de solo lectura que recopilaban los datos requeridos, realizaban las operaciones y escribían los resultados. MACSS fue uno de los primeros en utilizar esta técnica en un microprocesador.

Había una gran cantidad de hardware de soporte para el 6800 que seguiría siendo útil, como UART y sistemas de interfaz similares. Por esta razón, el nuevo diseño mantuvo un modo de compatibilidad de protocolo de bus para los dispositivos periféricos 6800 existentes.

Un chip con 32 pines de datos y 32 pines de direccionamiento requeriría 64 pines, más más para alimentación y otras funciones. En ese momento, los paquetes duales en línea (DIP) de 64 pines eran "grandes y costosos" sistemas y "simplemente terrible", lo que lo convierte en el más grande que podrían considerar. Para que encajara, Crook seleccionó un diseño híbrido, con una arquitectura de conjunto de instrucciones (ISA) de 32 bits pero implementándola con componentes de 16 bits, como la unidad lógica aritmética (ALU). La interfaz externa se redujo a 16 pines de datos y 24 para direcciones, lo que permitió que todo encajara en un paquete de 64 pines. Esto se conoció como la "Cucaracha de Texas".

Las técnicas de diseño de Motorola eran menos avanzadas que las de la competencia y sus líneas de fabricación estaban desactualizadas y tenían bajos rendimientos. En 1978, la empresa inició un programa de intercambio de tecnología con Hitachi, mejorando drásticamente su producción. Como parte de esto, se construyó una nueva fábrica, MOS-8, utilizando los últimos tamaños de obleas de 5 pulgadas y el proceso HMOS de Intel con un tamaño de función de 3,5 µm. Esto no cambió su lado de diseño. Si bien empresas como Zilog y MOS Technology habían introducido CPU que usaban puertas de silicio y lógica NMOS en modo de agotamiento, Motorola todavía usaba puertas de metal y modo de mejora. No fue hasta 1982 que cambiaron el MACCS a estas técnicas, y no fue hasta mediados o finales de la década de 1980 que Motorola se puso al día en la fabricación general.

Muestreo y producción

Lanzado formalmente en septiembre de 1979, las muestras iniciales se lanzaron en febrero de 1980, con chips de producción disponibles sin receta en noviembre. Los grados de velocidad iniciales son 4, 6 y 8 MHz. Los chips de 10 MHz estuvieron disponibles durante 1981 y los chips de 12,5 MHz en junio de 1982. Los chips de 16,67 MHz "12F" La versión del MC68000, la versión más rápida del chip HMOS original, no se produjo hasta finales de la década de 1980.

A principios de 1981, el 68k estaba logrando múltiples logros de diseño en la gama alta, y Gunter comenzó a acercarse a Apple para ganar su negocio. En ese momento, el 68k se vendió por alrededor de $125 en cantidad. En reuniones con Steve Jobs, Jobs habló sobre el uso de 68k en Apple Lisa, pero afirmó que "el verdadero futuro está en este producto que yo personalmente estoy haciendo". Si quiere este negocio, tiene que comprometerse a venderlo por $15." Motorola respondió ofreciendo venderlo a $55 al principio, luego bajarlo a $35, y así sucesivamente. Jobs estuvo de acuerdo y Macintosh pasó del 6809 al 68k. El precio promedio finalmente llegó a $ 14,76.

Variantes

En 1982, el 68000 recibió una actualización menor de su arquitectura de conjunto de instrucciones (ISA) para admitir memoria virtual y cumplir con los requisitos de virtualización de Popek y Goldberg. El chip actualizado se llama 68010. También agrega un nuevo "modo de bucle" lo que acelera los bucles pequeños y aumenta el rendimiento general en aproximadamente un 10% a las mismas velocidades de reloj. También se produjo en pequeñas cantidades una versión más ampliada, que expone 31 bits del bus de direcciones, como el 68012.

Para admitir sistemas de bajo costo y aplicaciones de control con tamaños de memoria más pequeños, Motorola presentó el MC68008 compatible con 8 bits, también en 1982. Se trata de un 68000 con un bus de datos de 8 bits y una dirección más pequeña (20 bits). autobús. Después de 1982, Motorola dedicó más atención a los proyectos 68020 y 88000.

Segundo abastecimiento

Varias otras empresas fueron fabricantes de segunda fuente del HMOS 68000. Entre ellas, Hitachi (HD68000), que redujo el tamaño de la función a 2,7 µm para su versión de 12,5 MHz, Mostek (MK68000), Rockwell (R68000), Signetics (SCN68000), Thomson/SGS-Thomson (originalmente EF68000 y luego TS68000) y Toshiba (TMP68000). Toshiba también fue un fabricante secundario del CMOS 68HC000 (TMP68HC000).

Las variantes encriptadas del 68000, que son Hitachi FD1089 y FD1094, almacenan claves de descifrado para códigos de operación y datos de códigos de operación en una memoria respaldada por batería y se usaron en ciertos sistemas arcade de Sega, incluido el Sistema 16, para evitar la piratería y los juegos piratas ilegales.

Versiones CMOS

El 68HC000, la primera versión CMOS del 68000, fue diseñado por Hitachi y presentado conjuntamente en 1985. La versión de Motorola se llama MC68HC000, mientras que la de Hitachi es HD68HC000. El 68HC000 ofrece velocidades de 8 a 20 MHz. Excepto por el uso de circuitos CMOS, se comportó de manera idéntica al HMOS MC68000, pero el cambio a CMOS redujo en gran medida su consumo de energía. El HMOS MC68000 original consumía alrededor de 1,35 vatios a una temperatura ambiente de 25 °C, independientemente de la velocidad del reloj, mientras que el MC68HC000 consumía solo 0,13 vatios a 8 MHz y 0,38 vatios a 20 MHz. (A diferencia de los circuitos CMOS, HMOS aún consume energía cuando está inactivo, por lo que el consumo de energía varía poco con la frecuencia del reloj). Apple seleccionó el 68HC000 para usar en Macintosh Portable.

Motorola reemplazó el MC68008 con el MC68HC001 en 1990. Este chip se parece al 68HC000 en la mayoría de los aspectos, pero su bus de datos puede funcionar en modo de 16 u 8 bits, según el valor de un pin de entrada al reiniciar. Así, al igual que el 68008, se puede utilizar en sistemas con memorias de 8 bits más económicas.

La evolución posterior del 68000 se centró en aplicaciones de control integradas más modernas y periféricos en chip. El chip 68EC000 y el núcleo SCM68000 eliminan el bus periférico M6800 y excluyen la instrucción MOVE from SR de los programas de modo de usuario, lo que convierte a 68EC000 y 68SEC000 en las únicas CPU 68000 que no son 100 % compatibles con el código objeto con las CPU 68000 anteriores cuando se ejecuta en modo de usuario. Cuando se ejecuta en Modo Supervisor, no hay diferencia. En 1996, Motorola actualizó el núcleo independiente con circuitos completamente estáticos, consumiendo solo 2 µW en modo de bajo consumo, y lo llamó MC68SEC000.

Motorola cesó la producción de HMOS MC68000, así como de MC68008, MC68010, MC68330 y MC68340 el 1 de junio de 1996, pero su empresa derivada, Freescale Semiconductor, seguía produciendo MC68HC000, MC68HC001, MC68EC000 y MC68SEC000., así como los microcontroladores MC68302 y MC68306 y versiones posteriores de la familia DragonBall. Los descendientes arquitectónicos del 68000, las familias 680x0, CPU32 y Coldfire, también estaban todavía en producción. Más recientemente, con el cierre de la fábrica de Sendai, se descontinuaron todas las piezas 68HC000, 68020, 68030 y 68882, dejando solo el 68SEC000 en producción.

Como núcleo de microcontrolador

Desde que fue reemplazado por "true" Microprocesadores de 32 bits, el 68000 se utiliza como núcleo de muchos microcontroladores. En 1989, Motorola presentó el procesador de comunicaciones MC68302.

Aplicaciones

IBM consideró el 68000 para la PC de IBM pero eligió el Intel 8088 porque el 68000 no estaba listo; Walden C. Rhines escribió que "Motorola, con su tecnología superior, perdió el concurso de diseño más importante de los últimos 50 años". (IBM Instruments vendió brevemente los sistemas informáticos de laboratorio IBM System 9000 basados en 68000). El conjunto de instrucciones 68k es particularmente adecuado para implementar Unix, y el 68000 y sus sucesores se convirtieron en las CPU dominantes para las estaciones de trabajo basadas en Unix, incluidas las estaciones de trabajo Sun y Apollo/ Estaciones de trabajo de dominio.

En 1981, Motorola presentó la placa de computadora educativa Motorola 68000, una computadora de placa única con fines educativos y de capacitación que, además de la propia 68000, contenía memoria, dispositivos de E/S, temporizador programable y área de envoltura de cables para circuitos personalizados.. La placa se mantuvo en uso en las universidades de EE. UU. como una herramienta para aprender a programar en ensamblador hasta principios de la década de 1990.

En su presentación, el 68000 se utilizó por primera vez en sistemas de alto precio, incluidas las microcomputadoras multiusuario como la WICAT 150, las primeras computadoras Alpha Microsystems, Sage II/IV, Tandy 6000/TRS-80 Model 16 y Fortune 32:16; estaciones de trabajo de un solo usuario como los sistemas HP 9000 Series 200 de Hewlett-Packard, los primeros sistemas Apollo/Domain, Sun Microsystems' Sun-1 y el Concepto Corvus; y terminales gráficos como VAXstation 100 de Digital Equipment Corporation y Silicon Graphics' IRIS 1000 y 1200. Los sistemas Unix pasaron rápidamente a las generaciones posteriores más capaces de la línea 68k, que siguió siendo popular en ese mercado durante la década de 1980.

A mediados de la década de 1980, la caída del costo de producción hizo que el 68000 fuera viable para su uso en computadoras personales y domésticas, comenzando con Apple Lisa y Macintosh, y seguido por Commodore Amiga, Atari ST y Sharp X68000.

La microcomputadora Sinclair QL, junto con sus derivados, como la terminal empresarial ICL One Per Desk, fue la utilización de mayor importancia comercial del 68008. Helix Systems (en Missouri, Estados Unidos) diseñó una extensión del SWTPC SS- 50, el SS-64 y sistemas producidos construidos alrededor del procesador 68008.

Si bien la adopción de RISC y x86 desplazó a la serie 68000 como CPU de escritorio/estación de trabajo, el procesador encontró un uso sustancial en aplicaciones integradas. A principios de la década de 1990, se podían comprar cantidades de 68 000 CPU por menos de 30 USD por pieza.

El 68000 también tuvo un gran éxito como controlador integrado. Ya en 1981, las impresoras láser como la Imagen Imprint-10 estaban controladas por placas externas equipadas con la 68000. La primera HP LaserJet, presentada en 1984, venía con una 68000 de 8 MHz incorporada. Otros fabricantes de impresoras adoptaron la 68000, incluyendo Apple con su introducción de LaserWriter en 1985, la primera impresora láser PostScript. El 68000 continuó usándose ampliamente en impresoras durante el resto de la década de 1980, persistiendo hasta bien entrada la década de 1990 en impresoras de gama baja.

El 68000 tuvo éxito en el campo de los sistemas de control industrial. Entre los sistemas que se beneficiaron de tener un 68000 o derivado como microprocesador se encontraban familias de controladores lógicos programables (PLC) fabricados por Allen-Bradley, Texas Instruments y, posteriormente, tras la adquisición de esa división de TI, por Siemens. Los usuarios de tales sistemas no aceptan la obsolescencia del producto al mismo ritmo que los usuarios domésticos, y es muy probable que a pesar de haber sido instalados hace más de 20 años, muchos controladores basados en 68000 continuarán en servicio confiable hasta bien entrado el siglo XXI.

En varios osciloscopios digitales de los años 80, el 68000 se ha utilizado como un procesador de visualización de forma de onda; algunos modelos, incluido el LeCroy 9400/9400A, también usan el 68000 como un procesador matemático de formas de onda (que incluye suma, resta, multiplicación y división de dos formas de onda/referencias/memorias de formas de onda), y algunos osciloscopios digitales que usan el 68000 (incluido el 9400/9400A) también puede realizar funciones de transformada rápida de Fourier en una forma de onda.

Los microcontroladores 683XX, basados en la arquitectura 68000, se utilizan en equipos de redes y telecomunicaciones, decodificadores de televisión, instrumentos médicos y de laboratorio e incluso calculadoras portátiles. El MC68302 y sus derivados se han utilizado en muchos productos de telecomunicaciones de Cisco, 3com, Ascend, Marconi, Cyclades y otros. Los modelos anteriores de Palm PDA y Handspring Visor usaban DragonBall, un derivado del 68000. AlphaSmart usó la familia DragonBall en versiones posteriores de sus procesadores de texto portátiles. Texas Instruments usó el 68000 en sus calculadoras gráficas de gama alta, las series TI-89 y TI-92 y Voyage 200.

Una versión modificada del 68000 formó la base del emulador de hardware IBM XT/370 del procesador System 370.

Videojuegos

Los fabricantes de videojuegos utilizaron el 68000 como la columna vertebral de muchos juegos de arcade y consolas de juegos domésticas: Food Fight de Atari, de 1982, fue uno de los primeros juegos de arcade basados en 68000. Otros incluyeron System 16 de Sega, CP System y CPS-2 de Capcom, y Neo Geo de SNK. A fines de la década de 1980, el 68000 era lo suficientemente económico como para alimentar consolas de juegos domésticas, como la consola Sega Genesis de Sega y también el accesorio de CD de Sega (un sistema de CD de Sega tiene tres CPU, dos de ellos 68000). La consola multiprocesador Atari Jaguar de 1993 usó un 68000 como chip de soporte, aunque algunos desarrolladores lo usaron como procesador principal debido a la familiaridad. La consola Sega Saturn usó el 68000 como coprocesador de sonido. En octubre de 1995, el 68000 se convirtió en una consola de juegos portátil, Genesis Nomad de Sega, como su CPU.

Algunos juegos de arcade (como Steel Gunner y otros basados en Namco System 2) utilizan una configuración de CPU dual 68000, y también existen sistemas con una configuración triple de CPU 68000 (como Galaxy Force y otros basados en Sega Y Board), junto con una configuración de CPU quad 68000, que ha sido utilizada por Jaleco (una 68000 para sonido tiene una velocidad de reloj más baja en comparación con las otras 68000 CPU) para juegos como Gran Carrera y Cisco Heat; otro quinto 68000 (a una velocidad de reloj diferente a las otras 68000 CPU) se usó en el juego de arcade de Jaleco Wild Pilot para el procesamiento de entrada/salida (E/S).

Arquitectura

Bus de direcciones

El 68000 tiene un bus de direcciones externo de 24 bits y dos señales de selección de bytes "reemplazadas" A0. Por lo tanto, estas 24 líneas pueden direccionar 16 MB de memoria física con resolución de bytes. El almacenamiento y el cálculo de direcciones utilizan 32 bits internamente; sin embargo, los 8 bits de dirección de orden superior se ignoran debido a la falta física de pines del dispositivo. Esto le permite ejecutar software escrito para un espacio de direcciones de 32 bits lógicamente plano, mientras accede solo a un espacio de direcciones físicas de 24 bits. La intención de Motorola con el espacio de direcciones interno de 32 bits era la compatibilidad hacia adelante, lo que hacía posible escribir software 68000 que aprovecharía al máximo las implementaciones posteriores de 32 bits del conjunto de instrucciones 68000.

Sin embargo, esto no impidió que los programadores escribieran software incompatible. "24 bits" el software que descartó el byte de dirección superior o lo usó para fines distintos al direccionamiento podría fallar en las implementaciones de 68000 de 32 bits. Por ejemplo, las primeras versiones (anteriores a la 7.0) del Mac OS de Apple usaban el byte alto de punteros maestros de bloque de memoria para contener indicadores como bloqueado y purgable.. Las versiones posteriores del sistema operativo movieron las banderas a una ubicación cercana y Apple comenzó a enviar computadoras que tenían '32 bits limpios'. ROM a partir del lanzamiento de Mac IIci de 1989.

La familia 68000 almacena enteros de varios bytes en la memoria en orden big-endian.

Registros internos

La CPU tiene ocho registros de datos de uso general de 32 bits (D0-D7) y ocho registros de direcciones (A0-A7). El último registro de dirección es el puntero de pila y los ensambladores aceptan la etiqueta SP como equivalente a A7. Este fue un buen número de registros en ese momento en muchos sentidos. Era lo suficientemente pequeño como para permitir que el 68000 respondiera rápidamente a las interrupciones (incluso en el peor de los casos, donde era necesario guardar los 8 registros de datos D0–D7 y los 7 registros de direcciones A0–A6, 15 registros en total) y, sin embargo, lo suficientemente grande como para hacer que la mayoría de los cálculos sean rápidos, ya que se pueden hacer completamente dentro del procesador sin guardar ningún resultado parcial en la memoria. (Tenga en cuenta que una rutina de excepción en el modo supervisor también puede guardar el puntero de pila de usuario A7, lo que daría un total de 8 registros de direcciones. Sin embargo, el diseño del puntero de pila dual (A7 y modo supervisor A7') del 68000 hace que esto normalmente sea innecesario, excepto cuando se realiza un cambio de tarea en un sistema multitarea).

Tener los dos tipos de registros permite realizar una dirección de 32 bits y un cálculo de datos de 16 bits al mismo tiempo. Esto da como resultado un tiempo de ejecución de instrucción reducido, ya que las direcciones y los datos se pueden procesar en paralelo.

Registro de estado

El 68000 tiene un registro de estado de 16 bits. Los 8 bits superiores son el byte del sistema y se privilegia su modificación. Los 8 bits inferiores son el byte de usuario, también conocido como registro de código de condición (CCR), y no se privilegia su modificación. Las operaciones lógicas, aritméticas y de comparación del 68000 modifican los códigos de condición para registrar sus resultados y utilizarlos en saltos condicionales posteriores. Los bits del código de condición son "cero" (Z), "llevar" (C), "desbordamiento" (V), "extender" (X) y "negativo" (NORTE). El "extender" La bandera (X) merece una mención especial, porque está separada de la bandera de acarreo. Esto permite que el bit adicional de las operaciones aritméticas, lógicas y de desplazamiento se separe de la aritmética de multiprecisión de acarreo.

Conjunto de instrucciones

Los diseñadores intentaron que el lenguaje ensamblador fuera ortogonal. Es decir, las instrucciones se dividen en operaciones y modos de dirección, y casi todos los modos de dirección están disponibles para casi todas las instrucciones. Hay 56 instrucciones y un tamaño mínimo de instrucción de 16 bits. Muchas instrucciones y modos de direccionamiento son más largos para incluir más bits de dirección o modo.

Niveles de privilegio

La CPU, y luego toda la familia, implementa dos niveles de privilegio. El modo de usuario da acceso a todo, excepto a las instrucciones privilegiadas, como los controles de nivel de interrupción. El privilegio de supervisor da acceso a todo. Una interrupción siempre se convierte en supervisora. El bit de supervisor se almacena en el registro de estado y es visible para los programas de usuario.

Una ventaja de este sistema es que el nivel de supervisor tiene un puntero de pila separado. Esto permite que un sistema multitarea use pilas muy pequeñas para las tareas, porque los diseñadores no tienen que asignar la memoria necesaria para contener los marcos de pila de una acumulación máxima de interrupciones.

Interrupciones

La CPU reconoce siete niveles de interrupción. Los niveles 1 a 5 tienen prioridad estricta. Es decir, una interrupción con un número más alto siempre puede interrumpir una interrupción con un número más bajo. En el registro de estado, una instrucción privilegiada permite establecer el nivel mínimo de interrupción actual, bloqueando las interrupciones de menor o igual prioridad. Por ejemplo, si el nivel de interrupción en el registro de estado se establece en 3, los niveles más altos de 4 a 7 pueden causar una excepción. El nivel 7 es una interrupción no enmascarable activada por nivel (NMI). El nivel 1 puede ser interrumpido por cualquier nivel superior. El nivel 0 significa que no hay interrupción. El nivel se almacena en el registro de estado y es visible para los programas de nivel de usuario.

Las interrupciones de hardware se envían a la CPU mediante tres entradas que codifican la prioridad de interrupción pendiente más alta. Por lo general, se requiere un codificador separado para codificar las interrupciones, aunque para los sistemas que no requieren más de tres interrupciones de hardware, es posible conectar las señales de interrupción directamente a las entradas codificadas a costa de una mayor complejidad de software. El controlador de interrupciones puede ser tan simple como un codificador de prioridad 74LS148, o puede ser parte de un chip periférico de integración a gran escala (VLSI) como el periférico multifunción MC68901 (utilizado en la gama de computadoras Atari ST y Sharp X68000), que también proporciona un UART, un temporizador y E/S paralelas.

La "tabla de excepciones" (direcciones de vector de interrupción de la tabla de vectores de interrupción) se fija en las direcciones 0 a 1023, lo que permite 256 vectores de 32 bits. El primer vector (RESET) consta de dos vectores, a saber, la dirección de la pila inicial y la dirección del código inicial. Los vectores 3 a 15 se utilizan para informar varios errores: error de bus, error de dirección, instrucción ilegal, división por cero, vector CHK y CHK2, violación de privilegios (para bloquear la escalada de privilegios) y algunos vectores reservados que se convirtieron en emulador de línea 1010, emulador de línea 1111 y punto de interrupción de hardware. El vector 24 inicia las interrupciones reales: interrupción espuria (sin reconocimiento de hardware) y autovectores de nivel 1 a nivel 7, luego los 16 vectores TRAP, luego algunos vectores más reservados, luego los vectores definidos por el usuario.

Dado que el vector de dirección del código de inicio siempre debe ser válido en el reinicio, los sistemas solían incluir alguna memoria no volátil (por ejemplo, ROM) que comenzaba en la dirección cero para contener los vectores y el código de arranque. Sin embargo, para un sistema de propósito general es deseable que el sistema operativo pueda cambiar los vectores en tiempo de ejecución. Esto a menudo se lograba apuntando los vectores en ROM a una tabla de salto en RAM, o mediante el uso de cambios de banco para permitir que la ROM fuera reemplazada por RAM en tiempo de ejecución.

El 68000 no cumple con los requisitos de virtualización de Popek y Goldberg para la virtualización completa del procesador porque tiene una única instrucción sin privilegios, "MOVE from SR", que permite el acceso de solo lectura del software en modo de usuario a un pequeño cantidad de estado privilegiado. El 68EC000 y el 68SEC000, que son derivados posteriores del 68000, cumplen los requisitos como "MOVE from SR" la instrucción es privilegiada. El mismo cambio se introdujo en las CPU 68010 y posteriores.

El 68000 tampoco puede soportar fácilmente la memoria virtual, lo que requiere la capacidad de capturar y recuperarse de un acceso fallido a la memoria. El 68000 proporciona una excepción de error de bus que se puede usar para atrapar, pero no guarda suficiente estado del procesador para reanudar la instrucción fallida una vez que el sistema operativo ha manejado la excepción. Varias empresas lograron fabricar estaciones de trabajo Unix basadas en 68000 con memoria virtual que funcionaba utilizando dos chips 68000 que se ejecutaban en paralelo en diferentes relojes de fase. Cuando el "principal" 68000 encontró un mal acceso a la memoria, el hardware adicional interrumpiría el "principal" 68000 para evitar que también encuentre el mal acceso a la memoria. Esta rutina de interrupción manejaría las funciones de la memoria virtual y reiniciaría el "principal" 68000 en el estado correcto para continuar la operación correctamente sincronizada cuando el "principal" 68000 devueltos de la interrupción.

Estos problemas se solucionaron en la próxima revisión importante de la arquitectura 68k con el lanzamiento del MC68010. Las excepciones Error de bus y Error de dirección envían una gran cantidad de estado interno a la pila del supervisor para facilitar la recuperación, y el comando "MOVE from SR" la instrucción se hizo privilegiada. Un nuevo "MOVE from CCR" se proporcionan instrucciones para su uso en su lugar mediante el software de modo de usuario; un sistema operativo puede atrapar y emular el modo de usuario "MOVER desde SR" instrucciones si lo desea.

Detalles del conjunto de instrucciones

Los modos de direccionamiento estándar son:

- Registro directo

- registro de datos, por ejemplo "D0"

- registro de direcciones, por ejemplo "A0"

- Registro indirecto

- Dirección sencilla, por ejemplo (A0)

- Dirección con post-incremento, por ejemplo (A0)+

- Address with pre-decrement, e.g. −(A0)

- Address with a 16-bit signed offset, e.g. 16(A0)

- Registro indirecto con registro de índices " offset firmado de 8 bits, por ejemplo 8(A0,D0) o 8(A0,A1)

- Tenga en cuenta que para (A0)+ y −(A0), el valor real de aumento o decremento depende del tamaño del operado: un acceso byte ajusta el registro de la dirección por 1, una palabra por 2, y un largo por 4.

- PC (contrar programa) relativo al desplazamiento

- Reparación relativa de 16 bits firmada, por ejemplo 16(PC). Este modo fue muy útil para el código independiente de posición.

- Relativo con 8 bits firmados con el índice, por ejemplo 8(PC,D2)

- Ubicación de memoria absoluta

- O un número, por ejemplo "$4000", o un nombre simbólico traducido por el ensamblador

- La mayoría de 68000 ensambladores utilizaron el símbolo "$" para el hexadecimal, en lugar de "0x" o un H que sigue.

- Había versiones de 16 y 32 bits de este modo de dirección

- Modo inmediato

- Datos almacenados en la instrucción, por ejemplo "#400"

- Modo inmediato rápido

- 3-bit sin firma (o 8-bit firmado con moveq) con valor almacenado en opcode

- En addq y subq, 0 es el equivalente a 8

- e.g. moveq #0,d0 was quicker than clr.l d0 (though both made D0 equal to 0)

Plus: acceso al registro de estado y, en modelos posteriores, a otros registros especiales.

La mayoría de las instrucciones tienen sufijos de letras y puntos, lo que permite que las operaciones se realicen en bytes de 8 bits (".b"), palabras de 16 bits (".w") y 32 -bit largos (".l").

Al igual que muchas CPU de su época, la sincronización del ciclo de algunas instrucciones variaba según los operandos de origen. Por ejemplo, la instrucción de multiplicación sin signo requiere (38+2n) ciclos de reloj para completarse, donde 'n' es igual al número de bits establecidos en el operando. Para crear una función que tomara un conteo de ciclos fijo, se requería la adición de código adicional después de la instrucción de multiplicación. Esto normalmente consumiría ciclos adicionales por cada bit que no se configuró en el operando de multiplicación original.

La mayoría de las instrucciones son diádicas, es decir, la operación tiene un origen y un destino, y el destino cambia. Las instrucciones notables fueron:

- Aritmetic: ADD, SUB, MULU (insignado multiplica), MULS (firmado multiplica), DIVU, DIVS, NEG (negación adicional), y CMP (una especie de comparación hecha restando los argumentos y estableciendo los bits de estado, pero no guardó el resultado)

- Aritmética decimal codificada por binario: ABCD, NBCD y SBCD

- Lógica: EOR (exclusiva o), Y, NO (lógica no), O (inclusiva o)

- Cambio: (cambios lógicos, es decir, los turnos correctos ponen cero en el bit más significativo) LSL, LSR, (cambios alérgicos, es decir, signo-extienda el bit más significativo) ASR, ASL, (rota por eXtend y no) ROXL, ROXR, ROL, ROR

- Prueba de bits y manipulación en memoria o registro de datos: BSET (set to 1), BCLR (clear to 0), BCHG (invert) y BTST (sin cambio). Todas estas instrucciones prueban primero el bit de destino y establecer (clarar) el bit CCR Z si el bit de destino es 0 (1), respectivamente.

- Control multiprocesador: TAS, test-and-set, realizó una operación de bus indivisible, permitiendo que se utilicen semáforos para sincronizar varios procesadores compartiendo una memoria única

- Flujo de control: JMP (jump), JSR (jump to subroutine), BSR (acceso de dirección relativa a la subrutina), RTS (retorno de la subrutina), RTE (retorno de la excepción, es decir, una interrupción), TRAP (trigger una excepción de software similar a la interrupción del software), CHK (excepción de software condicional)

- Rama: Bcc (donde el "cc" especificó una de las 14 pruebas de los códigos de condición en el registro de estado: igual, mayor que, menos que, carga, y la mayoría de combinaciones e inversiones lógicas, disponibles en el registro de estado). Las otras dos condiciones posibles (siempre verdaderas y siempre falsas) tienen instrucción separada mnemonics, BRA (siempre el cerebro), y BSR (branch to subroutine).

- Decrement-and-branch: DBcc (donde "cc" era como las instrucciones de la rama), que, siempre que la condición era falso, decrementó la palabra baja de un registro D y, si el resultado no era -1 (FFFF), ramificado a un destino. Este uso de −1 en lugar de 0 como el valor de terminación permitió la fácil codificación de bucles que no tenían que hacer nada si el conteo era 0 para empezar, sin necesidad de otro cheque antes de entrar en el bucle. Esto también facilitó la anidación de DBcc.

68EC000

El 68EC000 es una versión de bajo costo del 68000 con un pinout ligeramente diferente, diseñado para aplicaciones de controlador incorporado. El 68EC000 puede tener un bus de datos de 8 bits o de 16 bits, conmutable al reiniciar.

Los procesadores están disponibles en una variedad de velocidades, incluidas configuraciones de 8 y 16 MHz, y producen 2100 y 4376 Dhrystones cada uno. Estos procesadores no tienen unidad de punto flotante y es difícil implementar un coprocesador FPU (MC68881/2) con uno porque la serie EC carece de las instrucciones de coprocesador necesarias.

El 68EC000 se usó como controlador en muchas aplicaciones de audio, incluidos los instrumentos musicales y las tarjetas de sonido de Ensoniq, donde formaba parte del sintetizador MIDI. En las placas de sonido Ensoniq, el controlador proporcionó varias ventajas en comparación con los competidores sin una CPU integrada. El procesador permitió que la placa se configurara para realizar varias tareas de audio, como la síntesis MIDI MPU-401 o la emulación MT-32, sin el uso de un programa residente de terminación y permanencia. Esto mejoró la compatibilidad del software, redujo el uso de la CPU y eliminó el uso de la memoria del sistema host.

El núcleo Motorola 68EC000 se usó más tarde en los procesadores DragonBall basados en m68k de Motorola/Freescale.

También se usó como controlador de sonido en la consola de juegos Sega Saturn y como controlador para las placas controladoras HP JetDirect Ethernet para las impresoras HP LaserJet de mediados de la década de 1990.

Código de ejemplo

El siguiente código ensamblador 68000 es para una subrutina llamada strtolower, que copia una cadena terminada en cero de caracteres de 8 bits en una cadena de destino, convirtiendo todos los caracteres alfabéticos a minúsculas.

00100000

00100000 4E56 0000

00100004 306E 0008

00100008 326E 000C

0010000C 1018

0010000E 0C40 0041

00100012 6500 000E

00100016 0C40 005A

0010001A 6200 0006

0010001E 0640 0020

00100022 12C0

00100024 66E6

00100026 4E5E

00100028 4E75

0010002A

| ; strtolower:; Copiar una cadena ASCII de término nulo, conversión; todos los caracteres alfabéticos al caso inferior.;; Parámetros de entrada:; (SP+0): Dirección de la cadena fuente; (SP+4): Dirección de la cadena de destino org $00100000 ;Comienza a las 00100000strtolower público enlace a6,#0 ; Configurar el marco de la pila movea 8()a6),a0 ;A0 = src, de la pila movea 12()a6),a1 ;A1 = dst, de la pilabucle Muévete. b ()a0)+,♪ ;Load D0 de (src), incr src cmpi #'A ',♪ ; Si D0 "A" blo Copia ;skip cmpi #'Z',♪ ; Si D0 "Z", bhi Copia ;skip addi #'a'-'A ',♪ ;D0 = minúscula (D0)Copia Muévete. b ♪,(a1)+ ;Store D0 to (dst), incr dst bne bucle ;Repetir mientras D0 se dio NUL Unlk a6 ; Restaurar el marco de la pila rts ; Retorno final |

La subrutina establece una trama de llamada utilizando el registro A6 como puntero de trama. Este tipo de convención de llamadas admite código recursivo y reentrante y, por lo general, se usa en lenguajes como C y C++. Luego, la subrutina recupera los parámetros que se le pasaron (src y dst) de la pila. Luego se repite, leyendo un carácter ASCII (un byte) del src cadena, verificando si es un carácter alfabético en mayúsculas y, de ser así, convirtiéndolo en un carácter en minúsculas, de lo contrario, déjelo como está, luego escriba el carácter en el dst cadena. Finalmente, comprueba si el carácter era un carácter nulo; si no, repite el ciclo, de lo contrario, restaura el marco de pila anterior (y el registro A6) y regresa. Tenga en cuenta que los punteros de cadena (registros A0 y A1) se incrementan automáticamente en cada iteración del ciclo.

Por el contrario, el siguiente código es para una función independiente, incluso en la versión más restrictiva de AMS para la serie de calculadoras TI-89, siendo independiente del kernel, sin valores buscados en tablas, archivos o bibliotecas al ejecutar, sin llamadas al sistema, sin procesamiento de excepciones, registros mínimos a utilizar, ni necesidad de guardar ninguno. Es válido para fechas julianas históricas del 1 de marzo al 1 d.C. o para fechas gregorianas. En menos de dos docenas de operaciones, calcula un número de día compatible con ISO 8601 cuando se llama con tres entradas almacenadas en sus UBICACIONES correspondientes:

; ; WDN, una dirección - para almacenar el resultado d0 ; FLAG, 0 o 2 - elegir entre Julian o Gregorian, respectivamente ; DATE, year0mda - fecha sello como palabra binaria Pulbyte envueltobyte en formato ISO básico ; (Año, año ~ AÑO=Fecha por grande-endianness) ;move.l DATE,d0move.l d0,d1; ; Paso de aplicación 1 - La congruencia de Lachmanandi.l #$f00,d0divu #100,d0addi.w #193,d0andi.l #$ff,d0divu #100,d0 ; d0 has the month index i in the upper word (mod 100); ; Paso de aplicación 2 - Encontrar a spqr como el año del salto Juliano anterior al FECHAswap d0andi.l #$ffff,d0add.b d1,d0add.w YEAR,d0subi.l #$300,d1lsr #2,d1swap d1add.w d1,d0 ; spqr/4 + year + i + da; ; (Paso de aplicación 0 - Ajuste gregoriano)mulu FLAG,d1divu #50,d1mulu #25,d1lsr #2,d1add.w d1,d0add.w FLAG,d0 ; (sp32div16) + spqr/4 + year + i + da;divu #7,d0swap d0 ; d0.w becomes the day number;move.w d0,WDN ; returns the day number to address WDNrts; ; Los días de la semana corresponden a los números diarios de la semana como: ; Sun=0 Mon=1 Tue=2 Wed=3 Thu=4 Fri=5 Sat=6 ;

Contenido relacionado

Freno de aire ferroviario

Ethernet rápida

Aprovisionamiento (telecomunicaciones)