Matriz lógica programable

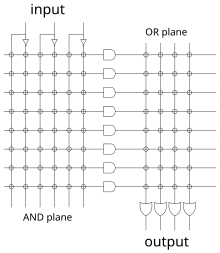

Una matriz lógica programable (PLA) es un tipo de dispositivo lógico programable que se utiliza para implementar circuitos lógicos combinacionales. El PLA tiene un conjunto de planos de puerta AND programables, que se vinculan a un conjunto de planos de puerta OR programables, que luego pueden complementarse condicionalmente para producir una salida. Tiene 2N puertas AND para N variables de entrada, y para M salidas de PLA, debe haber M puertas OR, cada una con entradas programables de todas las puertas AND. Este diseño permite sintetizar muchas funciones lógicas en la suma de formas canónicas de productos.

Los PLA se diferencian de los dispositivos lógicos de matriz programables (PAL y GAL) en que tanto los planos de puerta AND como OR son programables. [PAL tiene puertas AND programables pero puertas OR fijas]

Historia

En 1970, Texas Instruments desarrolló un circuito integrado programable por máscara basado en la memoria asociativa de sólo lectura o ROAM de IBM. Este dispositivo, el TMS2000, fue programado alterando la capa de metal durante la producción del CI. El TMS2000 tenía hasta 17 entradas y 18 salidas con 8 flip-flops JK para memoria. TI acuñó el término matriz lógica programable para este dispositivo.

Procedimiento de implementación

- Preparación en forma SOP (sumo de productos).

- Obtener el formulario mínimo SOP para reducir el número de términos de producto al mínimo.

- Decide la conexión de entrada de la matriz AND para generar el término de producto requerido.

- Luego decide las conexiones de entrada de la matriz OR para generar los términos de suma.

- Decide las conexiones de matriz invertida.

- Programa el PLA.

Diagrama de bloques de PLA:

| 1ST BLOCK | 2ND BLOCK | 3RD BLOCK | 4th BLOCK | 5th BLOCK |

|---|---|---|---|---|

| INPUT BUFFER | Y MATRIX | O MATRIX | INVERT/ NO INVERTIR MATRIX | FLIP FLOP OUTPUT BUFFER |

Ventajas sobre la memoria de solo lectura

Las salidas deseadas para cada combinación de entradas podrían programarse en una memoria de solo lectura, siendo las entradas controladas por el bus de direcciones y las salidas leídas como datos. Sin embargo, eso requeriría una ubicación de memoria separada para cada combinación posible de entradas, incluidas combinaciones que se supone que nunca deben ocurrir, y también duplicar datos para "no importa"; condiciones (por ejemplo, lógica como "si la entrada A es 1, entonces, en lo que respecta a la salida X, no nos importa cuál sea la entrada B": en una ROM esto tendría que ser se escribe dos veces, una para cada valor posible de B, y a medida que se agregan más entradas "no importa", la duplicación crece exponencialmente); por lo tanto, una matriz lógica programable a menudo puede implementar una pieza de lógica usando menos transistores que el equivalente en la memoria de solo lectura. Esto es particularmente valioso cuando es parte de un chip de procesamiento donde los transistores son escasos (por ejemplo, el chip 6502 original contenía un PLA para dirigir varias operaciones del procesador).

Aplicaciones

Una aplicación de un PLA es implementar el control sobre una ruta de datos. Define varios estados en un conjunto de instrucciones y produce el siguiente estado (mediante bifurcación condicional). [p.ej. si la máquina está en el estado 2, y pasará al estado 4 si la instrucción contiene un campo inmediato; entonces el PLA debería definir las acciones del control en el estado 2, establecerá el siguiente estado en 4 si la instrucción contiene un campo inmediato y definirá las acciones del control en el estado 4]. Los conjuntos lógicos programables deben corresponder a un diagrama de estado del sistema.

Las primeras computadoras domésticas Commodore 64 lanzadas en 1982 (hasta principios de 1983) inicialmente usaban un PLA Signetics 82S100 programado, pero a medida que aumentó la demanda, MOS Technology / Commodore Semiconductor Group comenzaron a producir un PLA programado con máscara, que llevaba el número de pieza 906114. -01.

Contenido relacionado

Historia de la cámara

Tubo de vacío

Señales de humo