Cirix 6x86

El Cyrix 6x86 es una línea de microprocesadores x86 de 32 bits de sexta generación diseñados y lanzados por Cyrix en 1995. Cyrix, al ser una empresa sin fábrica, tenía los chips fabricados por IBM y SGS. Thomson. El 6x86 se fabricó como un competidor directo de la línea de microprocesadores Pentium de Intel y era compatible con pines. Durante el desarrollo de 6x86, la mayoría de las aplicaciones (software de oficina y juegos) realizaban operaciones con enteros casi en su totalidad. Los diseñadores previeron que las aplicaciones futuras probablemente mantendrían este enfoque de instrucción. Entonces, para optimizar el rendimiento del chip para lo que creían que era la aplicación más probable de la CPU, los recursos de ejecución de enteros recibieron la mayor parte del presupuesto del transistor. Más tarde, esto resultaría ser un error estratégico, ya que la popularidad del Pentium P5 hizo que muchos desarrolladores de software optimizaran manualmente el código en lenguaje ensamblador, para aprovechar la FPU de latencia más baja y estrechamente canalizada del Pentium P5. Por ejemplo, el juego de disparos en primera persona muy esperado Quake utilizó un código ensamblador altamente optimizado diseñado casi en su totalidad alrededor de la FPU del P5 Pentium. Como resultado, el Pentium P5 superó significativamente a otras CPU en el juego.

Historia

El 6x86, anteriormente con el nombre en clave "M1" fue anunciado por Cyrix en octubre de 1995. En el momento del lanzamiento, solo estaba disponible la versión de 100 MHz (P120+), pero se planeó una versión de 120 MHz (P150+) para mediados de 1995 con un modelo de 133 MHz (P166+) más tarde. El 6x86 de 100 MHz (P120+) estaba disponible para los OEM a un precio de 450 USD por chip en grandes cantidades.

A mediados de febrero de 1996, Cyrix anunció que se agregarían los modelos P166+, P150+ y P133+ a la línea de modelos 6x86. IBM, que produjo los chips, también anunció que venderá sus propias versiones de los chips.

El P200+ de 6x86 se planificó para fines de 1996 y terminó siendo lanzado en junio.

El M2 (6x86MX) se anunció por primera vez para estar en desarrollo a mediados de 1996. Tendría MMX y optimización de 32 bits. El M2 también tendría algunas de las mismas características que el Intel Pentium Pro, como el cambio de nombre de registro, la finalización desordenada y la ejecución especulativa. Además, tendría 64 KB de caché sobre el 6x86 original y los 16 KB de Pentium Pro. En marzo de 1997, cuando se le preguntó cuándo comenzaría a enviarse la línea de procesadores M2, el director gerente de Cyrix UK, Brendan Sherry, dijo: "He leído que será en mayo, pero hemos dicho finales del segundo trimestre todo el tiempo y estoy bastante seguro de que lo lograremos.

El 6x86L se lanzó por primera vez en enero de 1997 para solucionar los problemas de calor de la línea 6x86 original. El 6x86L tenía un voltaje de núcleo en V más bajo y requería un regulador de voltaje de plano de potencia dividido.

En abril de 1997 se puso a la venta el primer portátil con procesador 6x86. Fueron vendidos por TigerDirect y tenían una pantalla DSTN de 12,1 pulgadas, 16 MB de memoria, 10x CD-ROM, disco duro de 1,3 GB y un precio base de 1.899 dólares.

Más tarde, a fines de mayo de 1997, el 27, Cyrix dijo que anunciarían los detalles de la nueva línea de chips (6x86MX) el día antes de Computex en junio de 1997. Para el extremo inferior de la serie, el PR166 6x86MX estaba disponible para $190 con versiones de gama alta PR200 y PR233 disponibles por $240 y $320. IBM, al ser el productor de los chips de Cyrix, también vendería su propia versión. Cyrix esperaba enviar decenas de miles en junio de 1997 con hasta 1 millón para fin de año. Cyrix también esperaba lanzar un chip de 266 MHz a finales de 1997 y uno de 300 MHz en el primer trimestre de 1998. Tenían un rendimiento de punto flotante ligeramente mejor, lo que reducía los tiempos de suma y multiplicación en un tercio, pero seguía siendo más lento que el Intel Pentium. El M2 también tenía instrucciones MMX completas, 64 KB de caché sobre los 16 KB originales y tenía un voltaje de núcleo más bajo de 2,5 V sobre 3,3 V de la línea original de 6x86.

National Semiconductor adquirió Cyrix en julio de 1997. National Semiconductor no estaba interesado en procesadores de alto rendimiento, sino en dispositivos de sistema en un chip, y quería cambiar el enfoque de Cyrix a la línea MediaGX.

En enero de 1998, National Semiconductors produjo un procesador 6x86MX con una tecnología de proceso de 0,25 micras. Esto redujo el tamaño del chip de 150 milímetros cuadrados a 88. National cambió su producción de MII y MediaGX a 0,25 en agosto.

En septiembre de 1998, National Semiconductors dijo que la asociación de licencias de IBM con Cyrix había terminado. Esto se debió a que National quería aumentar la producción de chips Cyrix en sus propias instalaciones, y porque tener a IBM produciendo los chips de Cyrix estaba causando problemas tales como pérdidas de ganancias debido a que IBM solía fijar precios más bajos para sus versiones de chips de Cyrix.. National pagaría entre 50 y 55 millones de dólares a IBM para poner fin a la asociación, que finalizaría en abril siguiente. Luego, National trasladaría la producción de chips a sus propias instalaciones en South Portland, Maine.

El Cyrix MII se lanzó en mayo de 1998. Estos chips no eran tan emocionantes como la gente esperaba, ya que solo eran un cambio de marca del 6x86MX. En diciembre, estos chips costaron $80 por un MII-333, $59 por un MII-300, $55 por un MII-266 y $48 por un MII-233.

En mayo de 1999, National Semiconductor decidió abandonar el mercado de chips para PC debido a pérdidas significativas y puso a la venta la división de CPU de Cyrix.

VIA compró la línea Cyrix en junio de 1999 y puso fin al desarrollo de procesadores de alto rendimiento. El MII-433GP sería el último procesador producido por Cyrix. Además, después de la adquisición de VIA, se descontinuó el 6x86/L, pero VIA continuó vendiendo la línea 6x86MX/MII.

VIA continuaría produciendo el MII a principios de la década de 2000. Se esperaba que se suspendiera cuando se lanzara el VIA Cyrix MII. Sin embargo, el MII todavía estuvo disponible para la venta hasta mediados o finales de 2003, y se mostró en el sitio web de VIA como un producto hasta octubre, y todavía se usaba en dispositivos como computadoras en red.

Arquitectura

El 6x86 es superescalar y supercanalizado y realiza cambios de nombre de registros, ejecución especulativa, ejecución fuera de orden y eliminación de dependencia de datos. Sin embargo, siguió utilizando la ejecución x86 nativa y solo el microcódigo ordinario, como Winchip de Centaur, a diferencia de los competidores Intel y AMD, que introdujeron el método de traducción dinámica a microoperaciones con Pentium Pro y K5.. El 6x86 es compatible con socket con Intel P54C Pentium y se ofreció en seis niveles de rendimiento: PR 90+, PR 120+, PR 133+, PR 150+, PR 166+ y PR 200+. Estos niveles de rendimiento no se corresponden con la velocidad del reloj del propio chip (por ejemplo, un PR 133+ funcionó a 110 MHz, un PR 166+ funcionó a 133 MHz, etc.).

Con respecto a los cachés internos, tiene un caché principal de 16 KB y un caché de línea de instrucciones de 256 bytes totalmente asociativo se incluye junto con el caché principal, que funciona como caché de instrucciones principal.

El 6x86 y el 6x86L no eran completamente compatibles con el conjunto de instrucciones Intel P5 Pentium y no son compatibles con varios procesadores. Por esta razón, el chip se identificó como 80486 y deshabilitó la instrucción CPUID de forma predeterminada. El soporte de CPUID podría habilitarse habilitando primero los registros CCR extendidos y luego configurando el bit 7 en CCR4. La falta de compatibilidad total con P5 Pentium causó problemas con algunas aplicaciones porque los programadores habían comenzado a usar instrucciones específicas de P5 Pentium. Algunas empresas lanzaron parches para sus productos para que funcionen en el 6x86.

Se mejoró la compatibilidad con el Pentium en el 6x86MX, al agregar un contador de marca de tiempo para admitir la instrucción RDTSC del P5 Pentium. También se agregó soporte para las instrucciones CMOVcc de Pentium Pro.

Rendimiento

Al igual que AMD con sus procesadores K5 y los primeros K6, Cyrix usó una calificación PR (calificación de rendimiento) para relacionar su rendimiento con el Intel P5 Pentium (anterior a P55C), ya que el 6x86 es el rendimiento por reloj más alto. en relación con un Pentium P5 podría cuantificarse frente a una parte de Pentium con mayor frecuencia de reloj. Por ejemplo, un 6x86 de 133 MHz igualará o superará a un P5 Pentium a 166 MHz y, como resultado, Cyrix podría comercializar el chip de 133 MHz como equivalente a un P5 Pentium 166. Sin embargo, la calificación de relaciones públicas no fue una representación completamente veraz del desempeño del 6x86.

Si bien el rendimiento de enteros del 6x86 fue significativamente más alto que el del Pentium P5, su rendimiento de punto flotante fue más mediocre: entre 2 y 4 veces el rendimiento del 486 FPU por ciclo de reloj (dependiendo de la operación y precisión). La FPU en el 6x86 era en gran medida el mismo circuito que se desarrolló para los coprocesadores compatibles con 8087/80287/80387 de alto rendimiento anteriores de Cyrix, que era muy rápido para su época: la FPU de Cyrix era mucho más rápida que la 80387 y incluso el 80486 FPU. Sin embargo, seguía siendo considerablemente más lento que las nuevas y completamente rediseñadas FPU P5 Pentium y P6 Pentium Pro-Pentium III. Una de las características principales de las FPU P5/P6 es que admitían la intercalación de FPU e instrucciones enteras en su diseño, que los chips Cyrix no integraban. Esto provocó un rendimiento muy bajo con las CPU Cyrix en juegos y software que se aprovecharon de esto.

Por lo tanto, a pesar de ser muy rápidos reloj a reloj, el 6x86 y el MII se vieron obligados a competir en el extremo inferior del mercado, ya que AMD K6 e Intel P6 Pentium II siempre estaban por delante en velocidad de reloj. El 6x86's y el MII's de vieja generación "486 class" La unidad de coma flotante combinada con una sección entera que, en el mejor de los casos, estaba a la par con los nuevos chips P6 y K6 significaba que Cyrix ya no podía competir en rendimiento.

Modelos y amplificadores; variantes

6x86

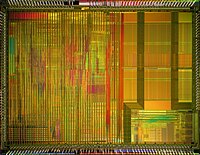

El 6x86 (nombre en clave M1) fue lanzado por Cyrix en 1996. La primera generación de 6x86 tenía problemas de calor. Esto se debió principalmente a su mayor producción de calor que otras CPU x86 de la época y, como tal, los fabricantes de computadoras a veces no las equiparon con la refrigeración adecuada. Las CPU alcanzaron un máximo de alrededor de 25 W de salida de calor (como el AMD K6), mientras que el P5 Pentium produjo alrededor de 15 W de calor residual en su punto máximo. Sin embargo, ambos números serían una fracción del calor generado por muchos procesadores de alto rendimiento, algunos años después. Poco después del M1 original, se lanzó el M1R. El M1R fue un cambio del proceso SGS-Thomson 3M al proceso IBM 5M, lo que hizo que los chips 6x86 fueran un 50 % más pequeños.

6x86L

Cyrix lanzó más tarde el 6x86L (nombre en clave M1L) para abordar los problemas de calor; la L significa baja potencia. Las tecnologías de fabricación mejoradas permitieron el uso de un Vcore más bajo. Al igual que el Pentium MMX, el 6x86L requería un regulador de voltaje de plano de potencia dividido con voltajes separados para E/S y núcleo de CPU.

6x86MX/MII

Otra versión del 6x86, el 6x86MX, agregó compatibilidad con MMX junto con el conjunto de instrucciones EMMI, mejoró la compatibilidad con Pentium y Pentium Pro al agregar un contador de marca de tiempo y las instrucciones CMOVcc respectivamente, y cuadriplicó el tamaño de caché principal a 64 KB. El caché de línea de instrucciones de 256 bytes se puede convertir en un caché de scratchpad para proporcionar soporte para operaciones multimedia. Las revisiones posteriores de este chip pasaron a llamarse MII, para competir mejor con el procesador Pentium II. Desafortunadamente, 6x86MX / MII llegó tarde al mercado y no pudo escalar bien en la velocidad del reloj con los procesos de fabricación utilizados en ese momento.

Modelo de mesa

| Imágenes | Modelo | Nombre básico | Tamaño del proceso

(μm) | Zona de muerte

(mm2) | Número de transistores

(millones) | Socket(s) | Paquete | Voltaje básico | TDP (W) | Velocidad del reloj | Velocidad del autobús | L1 Cache | Precio (USD) | Lanzamiento |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| PR90+ | M1 | 0,65 | 394 | 3.0 | Socket 7 | CPGA | 3.3 | 15,5 | 80 MHz | 40 MHz | 16 KB | 84 dólares | Nov 1995 | |

| PR120+ | M1 | 0,65 | 394 | 3.0 | Socket 7 | CPGA | 3.3 | ? | 100 MHz | 50 MHz | 16 KB | $450 | Oct 1995 | |

| PR133+ | M1R | 0,65 | 225 | 3.0 | Socket 7 | CPGA | 3.3 | 19.1 | 110 MHz | 55 MHz | 16 KB | $326 | 2-5-1996 | |

| PR150+ | M1R | 0,65 | 225 | 3.0 | Socket 7 | CPGA | 3.3/3.52 | 20.1 | 120 MHz | 60 MHz | 16 KB | $451 | 2-5-1996 | |

| PR166+ | M1R | 0,65 | 225 | 3.0 | Socket 7 | CPGA | 3.3/3.52 | 21.8 | 133 MHz | 66 MHz | 16 KB | $621 | 2-5-1996 | |

| PR200+ | M1R | 0,44 | ? | 3.0 | Socket 7 | CPGA | 3.52 | 17.13 | 150 MHz | 75 MHz | 16 KB | 499 | 6 a 6 de 1996 | |

| L-PR120+ | M1L | 0,35 | 169 | 3.0 | Socket 7 | CPGA | 2.8/3.3 | ? | 100 MHz | 50 MHz | 16 KB | ? | Jan-1997 | |

| L-PR133+ | M1L | 0,35 | 169 | 3.0 | Socket 7 | CPGA | 2.8/3.3 | ? | 110 MHz | 55 MHz | 16 KB | ? | Feb-1997 | |

| L-PR150+ | M1L | 0,35 | 169 | 3.0 | Socket 7 | CPGA | 2.8/3.3 | ? | 120 MHz | 60 MHz | 16 KB | ? | Mar-1997 | |

| L-PR166+ | M1L | 0,35 | 169 | 3.0 | Socket 7 | CPGA | 2.8/3.3 | 15.98 | 133 MHz | 66 MHz | 16 KB | ? | Apr-1997 | |

| L-PR200+ | M1L | 0,35 | 169 | 3.0 | Socket 7 | CPGA | 2.8/3.3 | 17.13 | 150 MHz | 75 MHz | 16 KB | ? | Apr-1997 | |

| PR166-MMX | MII | 0,35 | 197 | 6.0 | Socket 7 | CPGA | 2.9/3.3 | ?

? | 133 MHz

150 MHz | 66 MHz

60 MHz | 64 KB | 190 dólares

? | 5-30-97

Q2 1998 | |

| PR200-MMX | MII | 0,35 (IBM)

0,30 (NS) | 197

156 | 6.0 | Socket 7 | CPGA | 2.9/3.3 | ?

? | 150 MHz

166 MHz | 75 MHz

66 MHz | 64 KB | $240

? | 5-30-97

Q2 1998 | |

| PR233-MMX | MII | 0,35 (IBM)

0,30 (NS) | 197

156 | 6.0 | Socket 7 | CPGA | 2.9/3.3 | ?

? | 188 MHz

200 MHz | 75 MHz

66 MHz | 64 KB | $320

? | 5-30-97

Q2 1998 | |

| PR266-MMX | MII | 0,35 (IBM)

0,30 (NS) | 197

156 | 6.0 | Socket 7 | CPGA | 2.9/3.3 | ? | 208 MHz | 83 MHz | 64 KB | $180

? | 3-19-98

Q2 1998 | |

| MII-300-MMX (*m) | MII | 0,30

0,25 | 156

88 | 6.0 | Super 7 | CPGA | 2.9/3.3

2.2 (*m) | ?

? | 233 MHz

225 MHz | 66 MHz

75 MHz | 64 KB | $180

? | 4-14-98

Q1 1999 | |

| MII-333-MMX (*m) | MII | 0,30

0,25 | 156

88 | 6.0 | Super 7 | CPGA | 2.9/3.3

2.2 (*m) | ?

? | 250 MHz | 100 MHz

83 MHz | 64 KB | $180

? | 6-15-98

Mar-1999 | |

| MII-350-MMX | MII | 0,25 | 88 | 6.0 | Super 7 | CPGA | 2.9/3.3 | ? | 270 MHz

250 MHz | 90 MHz

83 MHz | 64 KB | ?

? | ?

? | |

| MII-366-MMX | MII | 0,25 | 88 | 6.0 | Super 7 | CPGA | 2.9/3.3 | ? | 250 MHz | 100 MHz | 64 KB | ? | Mar-1999 | |

| MII-400-MMX (*m) | MII | 0,18 | 65 | 6.0 | Super 7 | CPGA | 2.2/3.3 | ? | 285 MHz | 95 MHz | 64 KB | ? | Jun-1999 | |

| MII-433-MMX (*m) | MII | 0,18 | 65 | 6.0 | Super 7 | CPGA | 2.2/3.3 | ? | 300 MHz | 100 MHz | 64 KB | ? | Jun-1999 | |

| ? | Modelos SGS-Thomson 6x86 | |||||||||||||

| ST6x86P90+HS | M1 | 0,65 | 394 | 3.0 | Socket 7 | CPGA | 3.52 | 17.39 | 80 MHz | 40 MHz | 16 KB | ? | ? | |

| ST6x86P120+HS | M1 | 0,65 | 394 | 3.0 | Socket 7 | CPGA | 3.52 | 19.98 | 100 MHz | 50 MHz | 16 KB | ? | 2-5-1996 | |

| ST6x86P133+HS | M1 | 0,65 | 394 | 3.0 | Socket 7 | CPGA | 3.52 | 21.46 | 110 MHz | 55 MHz | 16 KB | ? | 2-5-1996 | |

| ST6x86P150+HS | M1 | 0,65 | 225 | 3.0 | Socket 7 | CPGA | 3.52 | ? | 120 MHz | 60 MHz | 16 KB | ? | 2-5-1996 | |

| ST6x86P166+HS | M1 | 0,65 | 225 | 3.0 | Socket 7 | CPGA | 3.52 | ? | 133 MHz | 66 MHz | 16 KB | ? | 2-5-1996 | |

| ST6x86P200+HS | M1 | 0,44 | ? | 3.0 | Socket 7 | CPGA | 3.52 | ? | 150 MHz | 75 MHz | 16 KB | ? | ? | |

| Modelos IBM 6x86 | ||||||||||||||

| 2V2100GB | M1 | 0,65 | 394 | 3.0 | Socket 7 | CPGA | 3.3 | ? | 80 MHz | 40 MHz | 16 KB | ? | ? | |

| 2V2P120GC | M1 | 0,65 | 394 | 3.0 | Socket 7 | CPGA | 3.3 | ? | 100 MHz | 50 MHz | 16 KB | ? | ? | |

| 2V2120GB | M1R | 0,65 | 394 | 3.0 | Socket 7 | CPGA | 3.33 | ? | 100 MHz | 50 MHz | 16 KB | ? | ? | |

| 2V2P150GE | M1R | 0,65 | 225 | 3.0 | Socket 7 | CPGA | 3.3/3.52 | ? | 120 MHz | 60 MHz | 16 KB | ? | 2-5-1996 | |

| 2V2P166GE | M1R | 0,65 | 225 | 3.0 | Socket 7 | CPGA | 3.3/3.52 | 21.8 | 133 MHz | 66 MHz | 16 KB | ? | 2-5-1996 | |

| 2V7P200GE | M1R | 0,44 | ? | 3.0 | Socket 7 | CPGA | 3.52 | 14 | 150 MHz | 75 MHz | 16 KB | ? | 2-5-1996 | |

| 2VAP120GB | M1L | 0,35 | 169 | 3.0 | Socket 7 | CPGA | 2.8 | ? | 100 MHz | 50 MHz | 16 KB | ? | ? | |

| 2VAP150GB | M1L | 0,35 | 169 | 3.0 | Socket 7 | CPGA | 2.8 | ? | 120 MHz | 60 MHz | 16 KB | ? | ? | |

| 2VAP166GB | M1L | 0,35 | 169 | 3.0 | Socket 7 | CPGA | 2.8 | ? | 133 MHz | 66 MHz | 16 KB | ? | ? | |

| 2VAP200GB | M1L | 0,35 | 169 | 3.0 | Socket 7 | CPGA | 2.8 | ? | 150 MHz | 75 MHz | 16 KB | ? | ? | |

| AVAPR166GB | MII | 0,35 | 197 | 6.0 | Socket 7 | CPGA | 2.9/3.3 | ? | 133 MHz | 66 MHz | 64 KB | 202 | 5-30-97 | |

| ? | MII | 0,35 | 197 | 6.0 | Socket 7 | CPGA | 2.9/3.3 | ? | 150 MHz | 60 MHz | 64 KB | ? | 5-30-97 | |

| BVAPR200GB | MII | 0,35 | ? | 6.0 | Socket 7 | CPGA | 2.9/3.3 | ? | 150 MHz | 75 MHz | 64 KB | 369 | 5-30-97 | |

| AVAPR200GA | MII | 0,30 | ? | 6.0 | Socket 7 | CPGA | 2.9/3.3 | ? | 166 MHz | 66 Mhz | 64 KB | ? | Q2 1998 | |

| BVAPR233GC | MII | 0,35 | ? | 6.0 | Socket 7 | CPGA | 2.9/3.3 | ? | 166 MHz | 83 MHz | 64 KB | 477 | 5-30-97 | |

| AVAPR233GB | MII | 0,30 | ? | 6.0 | Socket 7 | CPGA | 2.9/3.3 | ? | 188 MHz | 75 MHz | 64 KB | ? | Q2 1998 | |

| BVAPR233GD | MII | 0,30 | ? | 6.0 | Socket 7 | CPGA | 2.9/3.3 | ? | 200 MHz | 66 MHz | 64 KB | ? | Q2 1998 | |

| BVAPR266GE | MII | 0,35

0,30 | ? | 6.0 | Socket 7 | CPGA | 2.9/3.3 | ? | 208 MHz | 83 MHz | 64 KB | ? | 3-19-98

Q2 1998 | |

| CVAPR300GF (*m) | MII | 0,25 | 119 | 6.0 | Super 7 | CPGA | 2.9/3.3 | ? | 225 MHz | 75 MHz | 64 KB | $217 | 3-19-98 | |

| DVAPR300GF (*m) | MII | 0,25 | 119 | 6.0 | Super 7 | CPGA | 2.9/3.3 | ? | 233 MHz | 66 MHz | 64 KB | ? | ? | |

| CVAPR333GF (*m) | MII | 0,25 | 119 | 6.0 | Super 7 | CPGA | 2.9/3.3

2.2 (*m) | ? | 250 MHz | 83 MHz | 64 KB | 299 | 3-19-98 | |

| ? | MII | 0,25 | 119 | 6.0 | Super 7 | CPGA | 2.9/3.3 | ? | 263 MHz | 75 MHz | 64 KB | ? | ? | |

| ? - Falta de información

*m -Disponible en versión móvil para portátiles Información de:

| ||||||||||||||

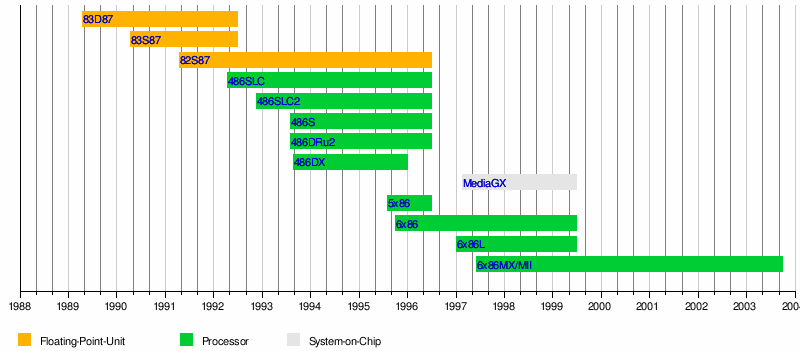

Cronología

| Timeline of Cyrix Products |

|---|

|

Contenido relacionado

Transporte en Albania

Krupp

Arma antiaérea autopropulsada