JFET

El transistor de efecto de campo de puerta de unión (JFET) es uno de los tipos más simples de transistor de efecto de campo. Los JFET son dispositivos semiconductores de tres terminales que se pueden usar como interruptores o resistencias controlados electrónicamente, o para construir amplificadores.

A diferencia de los transistores de unión bipolar, los JFET están controlados exclusivamente por voltaje, ya que no necesitan una corriente de polarización. La carga eléctrica fluye a través de un canal semiconductor entre las terminales de fuente y drenaje. Al aplicar un voltaje de polarización inversa a un terminal de compuerta, el canal se pellizca, de modo que la corriente eléctrica se impide o se apaga por completo. Un JFET generalmente conduce cuando no hay voltaje entre sus terminales de puerta y fuente. Si se aplica una diferencia de potencial de la polaridad adecuada entre sus terminales de puerta y fuente, el JFET será más resistente al flujo de corriente, lo que significa que fluirá menos corriente en el canal entre la fuente y los terminales de drenaje.

Los JFET a veces se denominan dispositivos de modo de agotamiento, ya que se basan en el principio de una región de agotamiento, que carece de portadores de carga mayoritarios. La región de agotamiento debe cerrarse para permitir que fluya la corriente.

Los JFET pueden tener un canal tipo n o tipo p. En el tipo n, si el voltaje aplicado a la puerta es negativo con respecto a la fuente, la corriente se reducirá (de manera similar en el tipo p, si el voltaje aplicado a la puerta es positivo con respecto a la fuente). Debido a que un JFET en una configuración de fuente común o drenaje común tiene una gran impedancia de entrada (a veces del orden de 1010 ohmios), se extrae poca corriente de los circuitos utilizados como entrada a la puerta.

Historia

Julius Lilienfeld patentó una sucesión de dispositivos similares a FET en las décadas de 1920 y 1930. Sin embargo, la ciencia de los materiales y la tecnología de fabricación requerirían décadas de avances antes de que los FET pudieran fabricarse.

JFET fue patentado por primera vez por Heinrich Welker en 1945. Durante la década de 1940, los investigadores John Bardeen, Walter Houser Brattain y William Shockley intentaron construir un FET, pero fracasaron en sus repetidos intentos. Descubrieron el transistor de contacto puntual mientras intentaban diagnosticar las razones de sus fallas. Siguiendo el tratamiento teórico de Shockley sobre JFET en 1952, George C. Dacey e Ian M. Ross crearon un JFET práctico y funcional en 1953. Los ingenieros japoneses Jun-ichi Nishizawa e Y. Watanabe solicitaron una patente para un dispositivo similar en 1950 denominado transistor de inducción estática (SIT). El SIT es un tipo de JFET con un canal corto.

La conmutación de alto voltaje y alta velocidad con JFET se volvió técnicamente factible luego de la introducción comercial de dispositivos de banda prohibida ancha de carburo de silicio (SiC) en 2008. Debido a las primeras dificultades en la fabricación, en particular, las inconsistencias y el bajo rendimiento, los JFET de SiC siguió siendo un producto de nicho al principio, con costos correspondientemente altos. Para 2018, estos problemas de fabricación se habían resuelto en su mayoría. Para entonces, los JFET de SiC también se usaban comúnmente junto con los MOSFET de silicio de bajo voltaje convencionales. En esta combinación, los dispositivos SiC JFET + Si MOSFET tienen las ventajas de los dispositivos de ancho de banda ancha, así como la fácil activación de puerta de los MOSFET.

Estructura

El JFET es un canal largo de material semiconductor, dopado para contener una gran cantidad de portadores de carga positiva o huecos (tipo p), o de portadores negativos o electrones (tipo n ). Los contactos óhmicos en cada extremo forman la fuente (S) y el drenaje (D). Se forma una unión pn en uno o ambos lados del canal, o rodeándolo usando una región con dopaje opuesto al del canal, y polarizada usando un contacto de puerta óhmica (G).

Funciones

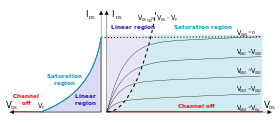

El funcionamiento de JFET se puede comparar con el de una manguera de jardín. El flujo de agua a través de una manguera se puede controlar apretándolo para reducir la sección transversal y el flujo de carga eléctrica a través de un JFET se controla restringiendo el canal de transporte de corriente. La corriente también depende del campo eléctrico entre la fuente y el drenaje (análogo a la diferencia de presión en cada extremo de la manguera). Esta dependencia actual no está respaldada por las características que se muestran en el diagrama por encima de un cierto voltaje aplicado. Esta es la región de saturación, y el JFET normalmente funciona en esta región de corriente constante donde la corriente del dispositivo prácticamente no se ve afectada por el voltaje de la fuente de drenaje. El JFET comparte esta característica de corriente constante con los transistores de unión y con los tetrodos y pentodos de tubo termoiónico (válvula).

La constricción del canal conductor se logra mediante el efecto de campo: se aplica un voltaje entre la puerta y la fuente para polarizar inversamente la unión pn de la puerta-fuente, lo que amplía la capa de agotamiento de esta unión (consulte la figura superior). invadiendo el canal conductor y restringiendo su área de sección transversal. La capa de agotamiento se denomina así porque está desprovista de portadores móviles y, por lo tanto, es eléctricamente no conductora para fines prácticos.

Cuando la capa de agotamiento abarca el ancho del canal de conducción, se logra pinch-off y se detiene la conducción del drenaje a la fuente. El pellizco ocurre en una polarización inversa particular (VGS) de la unión puerta-fuente. El voltaje de pinch-off (Vp) (también conocido como voltaje de umbral o voltaje de corte) varía considerablemente, incluso entre dispositivos del mismo tipo. Por ejemplo, VGS(apagado) para el dispositivo Temic J202 varía de −0.8 V a −4 V. Los valores típicos varían de −0.3 V a −10 V. (Confusamente, el término voltaje de pinch-off también se usa para referirse al valor de VDS que separa las regiones lineales y de saturación).

Para apagar un dispositivo de n-canales se requiere un voltaje de fuente de puerta negativo n (VGS). Por el contrario, para apagar un dispositivo de canal p se requiere pVGS positivo.

En funcionamiento normal, el campo eléctrico desarrollado por la compuerta bloquea la conducción fuente-drenaje hasta cierto punto.

Algunos dispositivos JFET son simétricos con respecto a la fuente y el drenaje.

Símbolos esquemáticos

La compuerta JFET a veces se dibuja en el medio del canal (en lugar de en el electrodo de drenaje o fuente como en estos ejemplos). Esta simetría sugiere que "drenaje" y "fuente" son intercambiables, por lo que el símbolo debe usarse solo para aquellos JFET en los que realmente son intercambiables.

El símbolo se puede dibujar dentro de un círculo (que representa la envoltura de un dispositivo discreto) si la caja es importante para la función del circuito, como componentes dobles en el mismo paquete.

En todos los casos, la punta de flecha muestra la polaridad de la unión P-N formada entre el canal y la puerta. Al igual que con un diodo ordinario, la flecha apunta de P a N, la dirección de la corriente convencional cuando está polarizada en directa. Un nemotécnico en inglés es que la flecha de un dispositivo de canal N "apunta in".

Comparación con otros transistores

A temperatura ambiente, la corriente de compuerta JFET (la fuga inversa de la unión de compuerta a canal) es comparable a la de un MOSFET (que tiene óxido aislante entre la compuerta y el canal), pero mucho menor que la corriente base de un Transistor de unión bipolar. El JFET tiene una mayor ganancia (transconductancia) que el MOSFET, así como un ruido de parpadeo más bajo y, por lo tanto, se utiliza en algunos amplificadores operacionales de alta impedancia de entrada y bajo ruido. Además, el JFET es menos susceptible al daño por la acumulación de carga estática.

Modelo matemático

Región óhmica lineal

La corriente en N-JFET debido a un pequeño voltaje VDS (es decir, en el lineal o Ohmic o región triode) es dado por tratar el canal como una barra rectangular de material de conductividad eléctrica :

dónde

- ID = corriente de drenaje-fuente,

- b = grosor de canal para un voltaje de puerta dado,

- W = ancho de canal,

- L = longitud del canal,

- q = carga de electrones = 1.6×10−19C,

- μn = movilidad de electrones,

- Nd = concentración de dopaje tipo n (donor)

- VP = tensión de despegue.

Entonces la corriente de drenaje en la región lineal se puede aproximar como

En términos de , la corriente de drenaje se puede expresar como

Región de corriente constante

La corriente de drenaje en la región saturación o activa o pinch-off a menudo se aproxima en términos de polarización de puerta como

donde IDSS es la corriente de saturación con voltaje de puerta-fuente cero, es decir, la corriente máxima que puede fluir a través del FET desde el drenaje a la fuente en cualquier (permisible) voltaje de drenaje a fuente (consulte, por ejemplo, el diagrama de características I–V anterior).

En la región de saturación, la corriente de drenaje del JFET se ve afectada de manera más significativa por el voltaje de la fuente de compuerta y apenas se ve afectada por el voltaje de la fuente de drenaje.

Si el dopaje del canal es uniforme, de modo que el espesor de la región de empobrecimiento crecerá en proporción a la raíz cuadrada del valor absoluto del voltaje de la puerta-fuente, entonces el espesor del canal b se puede expresar en términos del espesor del canal de polarización cero a como

dónde

- VP es el voltaje de presión – el voltaje de fuente de la puerta a la que el espesor del canal va a cero,

- a es el grosor del canal en el voltaje de fuente cero.

Transconductancia

La transconductancia para el FET de unión viene dada por

Donde es la tensión de despegue, y IDSS es la corriente máxima de drenaje. Esto también se llama o (para la transmisión).

Contenido relacionado

Computadora personal IBM

Instrumento musical electronico

Nanoingeniería