Interconexión de componentes periféricos

La interconexión de componentes periféricos (PCI) es un bus de computadora local para conectar dispositivos de hardware en una computadora y es parte del estándar PCI Local Bus. El bus PCI admite las funciones que se encuentran en un bus de procesador, pero en un formato estandarizado que es independiente del bus nativo de cualquier procesador dado. Los dispositivos conectados al bus PCI le parecen a un maestro de bus que están conectados directamente a su propio bus y se les asignan direcciones en el espacio de direcciones del procesador. Es un bus paralelo, síncrono a un solo reloj de bus. Los dispositivos adjuntos pueden adoptar la forma de un circuito integrado instalado en la placa base (llamado dispositivo plano en la especificación PCI) o una tarjeta de expansión que encaja en una ranura. El bus local PCI se implementó por primera vez en IBM PC compatibles, donde desplazó la combinación de varias ranuras de arquitectura estándar de la industria (ISA) lentas y una ranura de bus local VESA (VLB) rápida como configuración de bus. Posteriormente se ha adoptado para otros tipos de computadoras. Las tarjetas PCI típicas que se utilizan en las PC incluyen: tarjetas de red, tarjetas de sonido, módems, puertos adicionales como Universal Serial Bus (USB) o serie, tarjetas sintonizadoras de TV y adaptadores de host de unidad de disco duro. Las tarjetas de video PCI reemplazaron a las tarjetas ISA y VLB hasta que las crecientes necesidades de ancho de banda superaron las capacidades de PCI. La interfaz preferida para las tarjetas de video se convirtió en Accelerated Graphics Port (AGP), un superconjunto de PCI, antes de dar paso a PCI Express.

La primera versión de PCI que se encontró en las computadoras de escritorio minoristas era un bus de 32 bits que usaba un reloj de bus de 33 MHz y una señalización de 5 V, aunque el estándar PCI 1.0 también proporcionaba una variante de 64 bits. Estos tienen una muesca de ubicación en la tarjeta. La versión 2.0 del estándar PCI introdujo ranuras de 3,3 V, que se distinguen físicamente por un conector físico volteado para evitar la inserción accidental de tarjetas de 5 V. Las tarjetas universales, que pueden funcionar con cualquier voltaje, tienen dos muescas. La versión 2.1 del estándar PCI introdujo la operación opcional de 66 MHz. Una variante de PCI orientada a servidor, PCI Extended (PCI-X) operaba a frecuencias de hasta 133 MHz para PCI-X 1.0 y hasta 533 MHz para PCI-X 2.0. En la versión 2.2 de la especificación PCI se introdujo un conector interno para tarjetas de portátiles, denominado Mini PCI. El bus PCI también se adoptó para un estándar de conector de computadora portátil externa: el CardBus. Intel desarrolló la primera especificación PCI, pero el desarrollo posterior del estándar pasó a ser responsabilidad del Grupo de Interés Especial PCI (PCI-SIG).

PCI y PCI-X a veces se denominan PCI paralelo o PCI convencional para distinguirlos tecnológicamente de su sucesor más reciente, PCI Express, que adoptó una serie, Arquitectura basada en carriles. El apogeo de PCI en el mercado de las computadoras de escritorio fue aproximadamente de 1995 a 2005. PCI y PCI-X se han vuelto obsoletos para la mayoría de los propósitos; sin embargo, en 2020 todavía son comunes en las computadoras de escritorio modernas a los efectos de la compatibilidad con versiones anteriores y el bajo costo relativo de producción. Otra aplicación moderna común de PCI paralela es en PC industriales, donde muchas tarjetas de expansión especializadas, utilizadas aquí, nunca hicieron la transición a PCI Express, al igual que con algunas tarjetas ISA. Muchos tipos de dispositivos que antes estaban disponibles en las tarjetas de expansión PCI ahora se integran comúnmente en las placas base o están disponibles en versiones USB y PCI Express.

Historia

El trabajo en PCI comenzó en Intel Architecture Labs (IAL, también Architecture Development Lab) c. 1990. Un equipo compuesto principalmente por ingenieros de IAL definió la arquitectura y desarrolló un conjunto de chips y una plataforma de prueba de concepto (Saturn) en asociación con los equipos de los sistemas de PC de escritorio de la empresa y las organizaciones de productos de lógica central.

PCI se puso en uso de inmediato en servidores, reemplazando la arquitectura Micro Channel (MCA) y la arquitectura estándar industrial extendida (EISA) como el bus de expansión de servidor de elección. En las PC convencionales, PCI fue más lenta para reemplazar a VLB y no logró una penetración significativa en el mercado hasta finales de 1994 en las PC Pentium de segunda generación. En 1996, VLB estaba casi extinto y los fabricantes habían adoptado PCI incluso para las computadoras Intel 80486 (486). EISA se siguió utilizando junto con PCI hasta 2000. Apple Computer adoptó PCI para computadoras Power Macintosh profesionales (reemplazando a NuBus) a mediados de 1995, y la línea de productos de consumo Performa (reemplazando a LC Processor Direct Slot (PDS)) a mediados de 1996.

Fuera del mercado de servidores, la versión de 64 bits de PCI simple siguió siendo rara en la práctica, aunque fue utilizada, por ejemplo, por todas las computadoras G3 y G4 Power Macintosh (posteriores a iMac).

Revisiones posteriores de PCI agregaron nuevas funciones y mejoras de rendimiento, incluido un estándar de 3,3 V de 66 MHz y PCI-X de 133 MHz, y la adaptación de la señalización de PCI a otros factores de forma. Tanto PCI-X 1.0b como PCI-X 2.0 son compatibles con versiones anteriores de algunos estándares PCI. Estas revisiones se usaron en el hardware del servidor, pero el hardware de la PC del consumidor siguió siendo casi todo de 32 bits, 33 MHz y 5 voltios.

El PCI-SIG introdujo el PCI Express serial en c. 2004. Desde entonces, los fabricantes de placas base han incluido progresivamente menos ranuras PCI a favor del nuevo estándar. Muchas placas base nuevas no proporcionan ranuras PCI en absoluto, a finales de 2013.

| Específico | Año | Resumen |

|---|---|---|

| PCI 1.0 | 1992 | Cuestión original |

| PCI 2.0 | 1993 | Conector incorporado y especificación de tarjetas add-in |

| PCI 2.1 | 1995 | Incorporated clarifications and added 66 MHz chapter |

| PCI 2.2 | 1998 | Incorporated ECNs, and improved readability |

| PCI 2.3 | 2002 | ECNs incorporados, errata y borrado 5 volt sólo tarjetas de adición clave |

| PCI 3.0 | 2004 | Soporte extraído para conector de mesa de sistema de 5,0 voltios |

Configuración automática

PCI proporciona memoria separada y espacios de direcciones de puertos de E/S mapeados en memoria para la familia de procesadores x86, 64 y 32 bits, respectivamente. Las direcciones en estos espacios de direcciones son asignadas por software. Un tercer espacio de direcciones, llamado PCI Configuration Space, que utiliza un esquema de direccionamiento fijo, permite que el software determine la cantidad de memoria y espacio de direcciones de E/S que necesita cada dispositivo. Cada dispositivo puede solicitar hasta seis áreas de espacio de memoria o espacio de puerto de entrada/salida (E/S) a través de sus registros de espacio de configuración.

En un sistema típico, el firmware (o sistema operativo) consulta todos los buses PCI en el momento del inicio (a través del espacio de configuración PCI) para averiguar qué dispositivos están presentes y qué recursos del sistema (espacio de memoria, espacio de E/S, líneas de interrupción, etc.) que cada uno necesita. Luego asigna los recursos y le dice a cada dispositivo cuál es su asignación.

El espacio de configuración de PCI también contiene una pequeña cantidad de información sobre el tipo de dispositivo, lo que ayuda a un sistema operativo a elegir controladores de dispositivo para él, o al menos a tener un diálogo con un usuario sobre la configuración del sistema.

Los dispositivos pueden tener una memoria de solo lectura (ROM) integrada que contiene un código ejecutable para procesadores x86 o PA-RISC, un controlador Open Firmware o una ROM opcional. Suelen ser necesarios para los dispositivos que se utilizan durante el inicio del sistema, antes de que el sistema operativo cargue los controladores de dispositivos.

Además, hay temporizadores de latencia PCI que son un mecanismo para que los dispositivos de control de bus PCI compartan el bus PCI de manera justa. "Justo" en este caso significa que los dispositivos no utilizarán una porción tan grande del ancho de banda del bus PCI disponible que otros dispositivos no puedan realizar el trabajo necesario. Tenga en cuenta que esto no se aplica a PCI Express.

Cómo funciona esto es que cada dispositivo PCI que puede operar en modo bus-master es necesario para implementar un temporizador, llamado Latency Timer, que limita el tiempo que el dispositivo puede contener el bus PCI. El temporizador comienza cuando el dispositivo gana la propiedad del autobús, y cuenta a la velocidad del reloj PCI. Cuando el contador llega a cero, el dispositivo es necesario para liberar el autobús. Si ningún otro dispositivo está esperando la propiedad del autobús, puede simplemente tomar el autobús de nuevo y transferir más datos.

Interrupciones

Los dispositivos deben seguir un protocolo para que las líneas de interrupción se puedan compartir. El bus PCI incluye cuatro pines de interrupción, luego permite que hasta 8 dispositivos PCI compartan la misma línea de interrupción en sistemas APIC, todos los cuales están disponibles para cada dispositivo. Sin embargo, no están conectados en paralelo como lo están las otras líneas de bus PCI. Las posiciones de las líneas de interrupción rotan entre las ranuras, por lo que lo que aparece en un dispositivo como el pin INTA# es INTB# en el siguiente e INTC# en el siguiente. Los dispositivos de una sola función generalmente usan su INTA# para la señalización de interrupción, por lo que la carga del dispositivo se distribuye de manera bastante uniforme entre los cuatro pines de interrupción disponibles. Esto alivia un problema común con las interrupciones compartidas.

La asignación de líneas de interrupción PCI en líneas de interrupción del sistema, a través del puente de host PCI, depende de la implementación. El código del sistema básico de entrada/salida (BIOS) específico de la plataforma está diseñado para saber esto y establecer la "línea de interrupción" campo en el espacio de configuración de cada dispositivo que indica a qué IRQ está conectado.

Las líneas de interrupción PCI se activan por nivel. Se eligió esto sobre la activación por borde para obtener una ventaja al dar servicio a una línea de interrupción compartida y por robustez: las interrupciones activadas por borde son fáciles de perder.

Revisiones posteriores de la especificación PCI agregan soporte para interrupciones señaladas por mensaje. En este sistema, un dispositivo señala su necesidad de servicio al realizar una escritura en la memoria, en lugar de afirmar una línea dedicada. Esto alivia el problema de la escasez de líneas de interrupción. Incluso si los vectores de interrupción aún se comparten, no sufre los problemas de uso compartido de las interrupciones activadas por nivel. También resuelve el problema de enrutamiento, porque la escritura en la memoria no se modifica de manera impredecible entre el dispositivo y el host. Finalmente, debido a que la señalización del mensaje está en banda, resuelve algunos problemas de sincronización que pueden ocurrir con escrituras publicadas y líneas de interrupción fuera de banda.

PCI Express no tiene ninguna línea de interrupción física. Utiliza interrupciones señalizadas por mensaje exclusivamente.

Especificaciones de hardware convencional

Estas especificaciones representan la versión más común de PCI utilizada en PC normales:

- 33.33 MHz reloj con transferencias sincronizadas

- Tasa de transferencia de pico de 133 MB/s (133 megabytes por segundo) para ancho de autobús de 32 bits (33.33 MHz × 32 bits ÷ 8 bits/byte = 133 MB/s)

- ancho de autobús de 32 bits

- Espacio de dirección de memoria de 32 o 64 bits (4 GiB o 16 EiB)

- 32-bit I/O espacio portuario

- 256-byte (por dispositivo) espacio de configuración

- 5-volt signaling

- Cambio de onda reflejada

La especificación PCI también proporciona opciones para señalización de 3,3 V, ancho de bus de 64 bits y frecuencia de reloj de 66 MHz, pero estas no se encuentran comúnmente fuera de la compatibilidad con PCI-X en las placas base de servidor.

El árbitro de bus PCI realiza el arbitraje de bus entre varios maestros en el bus PCI. Cualquier número de maestros de bus puede residir en el bus PCI, así como solicitudes para el bus. Un par de señales de solicitud y concesión está dedicado a cada maestro de bus.

Tensión y codificación de la tarjeta

Las tarjetas PCI típicas tienen una o dos muescas clave, según su voltaje de señalización. Las tarjetas que requieren 3,3 voltios tienen una muesca a 56,21 mm de la placa posterior de la tarjeta; los que requieren 5 voltios tienen una muesca a 104,47 mm de la placa trasera. Esto permite que las tarjetas se instalen solo en ranuras con un voltaje que admitan. "Tarjetas universales" aceptar cualquiera de los voltajes tiene ambas muescas clave.

Disposición de pines del conector

Se define que el conector PCI tiene 62 contactos en cada lado del conector de borde, pero dos o cuatro de ellos se reemplazan por muescas clave, por lo que una tarjeta tiene 60 o 58 contactos en cada lado. El lado A se refiere al 'lado de soldadura' y el lado B se refiere al 'lado del componente': si la tarjeta se sostiene con el conector hacia abajo, una vista del lado A tendrá la placa posterior a la derecha, mientras que una vista del lado B tendrá la placa posterior a la izquierda. La distribución de pines de los lados B y A es la siguiente, mirando hacia abajo en el conector de la placa base (los pines A1 y B1 son los más cercanos a la placa posterior).

| Pin | Lado B | Lado A | Comentarios | ||

|---|---|---|---|---|---|

| 1 | −12 V | TRST# | Agujas de puerto JTAG (opcional) | ||

| 2 | TCK | +12 V | |||

| 3 | Terreno | TMS | |||

| 4 | TDO | TDI | |||

| 5 | +5 V | +5 V | |||

| 6 | +5 V | INTA# | Pernos interrumpidos (abierto-drain) | ||

| 7 | INTB# | INTC# | |||

| 8 | INTD# | +5 V | |||

| 9 | PRSNT1# | Reservado | Baja para indicar la potencia de 7,5 o 25 W | ||

| 10 | Reservado | IOPWR | +5 V o +3.3 V | ||

| 11 | PRSNT2# | Reservado | Baja para indicar la potencia de 7,5 o 15 W | ||

| 12 | Terreno | Terreno | Noch clave para 3,3 tarjetas V | ||

| 13 | Terreno | Terreno | |||

| 14 | Reservado | 3.3 V aux | Potencia de reserva (opcional) | ||

| 15 | Terreno | RST# | Bus reset | ||

| 16 | CLK | IOPWR | reloj 33/66 MHz | ||

| 17 | Terreno | GNT# | Subsidio de autobús de placa madre a tarjeta | ||

| 18 | REQ# | Terreno | Solicitud de autobús de tarjeta a placa madre | ||

| 19 | IOPWR | PME# | Evento de gestión de energía (opcional) 3.3 V, desagüe abierto, activo bajo. | ||

| 20 | AD[31] | AD[30] | Autobús de dirección/data (medio superior) | ||

| 21 | AD[29] | +3.3 V | |||

| 22 | Terreno | AD[28] | |||

| 23 | AD[27] | AD[26] | |||

| 24 | AD[25] | Terreno | |||

| 25 | +3.3 V | AD[24] | |||

| 26 | C/BE[3]# | IDSEL | |||

| 27 | AD[23] | +3.3 V | |||

| 28 | Terreno | AD[22] | |||

| 29 | AD[21] | AD[20] | |||

| 30 | AD[19] | Terreno | |||

| 31 | +3.3 V | AD[18] | |||

| 32 | AD[17] | AD[16] | |||

| 33 | C/BE[2]# | +3.3 V | |||

| 34 | Terreno | FRAME# | Transferencia de autobuses en curso | ||

| 35 | IRDY# | Terreno | Iniciador listo | ||

| 36 | +3.3 V | TRDY# | Objetivo listo | ||

| 37 | DEVSEL# | Terreno | Objetivo seleccionado | ||

| 38 | PCIXCAP | Terreno | Parar | PCI-X capaz; | |

| 39 | LOCK# | +3.3 V | Transmisión bloqueada | ||

| 40 | PERR# | SMBCLK | SDONE | Error de paridad; reloj SMBus o Snoop made (obsolete) | |

| 41 | +3.3 V | SMBDAT | SBO# | SMBus datos o Snoop backoff (obsolete) | |

| 42 | SERR# | Terreno | Error de sistema | ||

| 43 | +3.3 V | PAR | Incluso la paridad sobre AD[31:00] y C/BE[3:0]# | ||

| 44 | C/BE[1] | AD[15] | Autobús de dirección/data (medio más alto) | ||

| 45 | AD[14] | +3.3 V | |||

| 46 | Terreno | AD[13] | |||

| 47 | AD[12] | AD[11] | |||

| 48 | AD[10] | Terreno | |||

| 49 | M66EN | Terreno | AD[09] | ||

| 50 | Terreno | Terreno | Punto clave para 5 tarjetas V | ||

| 51 | Terreno | Terreno | |||

| 52 | AD[08] | C/BE[0]# | Autobús de dirección/data (media baja) | ||

| 53 | AD[07] | +3.3 V | |||

| 54 | +3.3 V | AD[06] | |||

| 55 | AD[05] | AD[04] | |||

| 56 | AD[03] | Terreno | |||

| 57 | Terreno | AD[02] | |||

| 58 | AD[01] | AD[00] | |||

| 59 | IOPWR | IOPWR | |||

| 60 | ACK64# | REQ64# | Para la extensión de 64 bits; no hay conexión para dispositivos de 32 bits. | ||

| 61 | +5 V | +5 V | |||

| 62 | +5 V | +5 V | |||

PCI de 64 bits amplía esto con 32 contactos adicionales en cada lado que proporcionan AD[63:32], C/BE[7:4]#, la señal de paridad PAR64 y varios pines de alimentación y tierra.

| Alfil de tierra | Referencia de cero voltios |

|---|---|

| Pista de potencia | Suponga poder a la tarjeta PCI |

| Puño de salida | Conducido por la tarjeta PCI, recibida por la placa base |

| Salida del iniciador | Conducido por el maestro/iniciador, recibido por el objetivo |

| I/O signal | Puede ser impulsado por el iniciador o objetivo, dependiendo de la operación |

| Producto objetivo | Conducido por el objetivo, recibido por el iniciador/master |

| Input | Conducido por la placa base, recibido por la tarjeta PCI |

| Abastecimiento abierto | Puede ser tirado bajo y / o sentido por múltiples tarjetas |

| Reservado | No se utiliza actualmente, no se conecta |

La mayoría de las líneas están conectadas a cada ranura en paralelo. Las excepciones son:

- Cada ranura tiene su propia salida REQ# a, y entrada GNT# del arbiter de placa madre.

- Cada ranura tiene su propia línea IDSEL, generalmente conectada a una línea AD específica.

- TDO está preparado para el TDI de la siguiente ranura. Las tarjetas sin soporte JTAG deben conectar TDI a TDO para no romper la cadena.

- PRSNT1# y PRSNT2# para cada ranura tienen sus propios resistores de arranque en la placa base. La placa base puede (pero no tiene que) sentir estos pines para determinar la presencia de tarjetas PCI y sus requisitos de potencia.

- REQ64# y ACK64# se tiran individualmente en ranuras de 32 bits.

- Los pines interrumpidos INTA# a través de INTD# están conectados a todas las ranuras en diferentes pedidos. (INTA# en una ranura es INTB# en el siguiente e INTC# en el después de eso.)

Notas:

- IOPWR es +3.3 V o +5 V, dependiendo del backplane. Las ranuras también tienen una cresta en uno de dos lugares que evita la inserción de las tarjetas que no tienen la llave correspondiente, indicando soporte para ese estándar de tensión. Las tarjetas universales tienen ambos puntos clave y usan IOPWR para determinar sus niveles de señal I/O.

- El PCI SIG alienta firmemente 3.3 V PCI señalización, que requiere soporte para ella desde la revisión estándar 2.3, pero la mayoría de las placas madre PC utilizan la variante 5 V. Por lo tanto, mientras que muchas tarjetas PCI actualmente disponibles soportan ambos, y tienen dos pasos clave para indicar que, todavía hay un gran número de 5 tarjetas sólo V en el mercado.

- El pin M66EN es un terreno adicional en 5 autobuses PCI V que se encuentran en la mayoría de placas madre PC. Tarjetas y placas madre que no soportan la operación de 66 MHz también colocan este pin. Si todos los participantes soportan la operación 66 MHz, un resistor de arranque en la placa base eleva esta señal alta y la operación 66 MHz está habilitada. El pin todavía está conectado a tierra a través de condensadores de acoplamiento en cada tarjeta para preservar su función de blindaje AC.

- El pin PCIXCAP es un terreno adicional en autobuses y tarjetas PCI. Si todas las tarjetas y la placa base soportan el protocolo PCI-X, un resistor de arranque en la placa base eleva esta señal alta y la operación PCI-X está habilitada. El pin todavía está conectado a tierra a través de condensadores de acoplamiento en cada tarjeta para preservar su función de blindaje AC.

- Al menos uno de PRSNT1# y PRSNT2# deben ser castigados por la tarjeta. La combinación elegida indica los requisitos de potencia total de la tarjeta (25 W, 15 W, o 7.5 W).

- SBO# y SDONE son señales de un controlador de caché al objetivo actual. No son salidas iniciadoras, pero son coloreados de esa manera porque son entradas de destino.

- PME#19 A) – Evento de gestión de energía (opcional) que se apoya en PCI versión 2.2 y más alto. Es una 3.3 V, desagüe abierto, señal baja activa. Las tarjetas PCI pueden utilizar esta señal para enviar y recibir PME directamente a través de la toma PCI, lo que elimina la necesidad de un cable de Wake-on-LAN especial.

Combinación de tarjetas PCI de 32 y 64 bits en ranuras de diferentes anchos

La mayoría de las tarjetas PCI de 32 bits funcionarán correctamente en las ranuras PCI-X de 64 bits, pero la velocidad del reloj del bus estará limitada a la frecuencia del reloj de la tarjeta más lenta, una limitación inherente de la topología de bus compartido de PCI.. Por ejemplo, cuando se instala un periférico PCI 2.3 de 66 MHz en un bus PCI-X con capacidad para 133 MHz, todo el backplane del bus se limitará a 66 MHz. Para sortear esta limitación, muchas placas base tienen dos o más buses PCI/PCI-X, con un bus diseñado para usarse con periféricos PCI-X de alta velocidad y el otro bus diseñado para periféricos de propósito general.

Muchas tarjetas PCI-X de 64 bits están diseñadas para funcionar en modo de 32 bits si se insertan en conectores de 32 bits más cortos, con cierta pérdida de rendimiento. Un ejemplo de esto es la tarjeta de interfaz SCSI de 64 bits Adaptec 29160. Sin embargo, algunas tarjetas PCI-X de 64 bits no funcionan en ranuras PCI estándar de 32 bits.

La instalación de una tarjeta PCI-X de 64 bits en una ranura de 32 bits dejará la porción de 64 bits del conector del borde de la tarjeta sin conectar y sobresaliendo. Esto requiere que no haya componentes de la placa base colocados de forma que obstruyan mecánicamente la parte sobresaliente del conector del borde de la tarjeta.

Dimensiones físicas

Alturas de soportes PCI:

- Estándar: 120,02 mm;

- Perfil bajo: 79.20 mm.

Longitudes de la tarjeta PCI (soporte estándar y 3,3 V):

- Tarjeta corta: 169,52 mm;

- Tarjeta larga: 313.78 mm.

Longitudes de la tarjeta PCI (soporte de perfil bajo y 3,3 V):

- MD1: 121.79 mm;

- MD2: 169,52 mm;

- MD3: 243.18 mm.

Mini PCI

Mini PCI se agregó a PCI versión 2.2 para usar en computadoras portátiles; utiliza un bus de 32 bits y 33 MHz con conexiones alimentadas (solo 3,3 V; 5 V está limitado a 100 mA) y es compatible con bus mastering y DMA. El tamaño estándar de las tarjetas Mini PCI es aproximadamente una cuarta parte de sus contrapartes de tamaño completo. No hay acceso a la tarjeta desde el exterior de la caja, a diferencia de las tarjetas PCI de escritorio con soportes que llevan conectores. Esto limita los tipos de funciones que puede realizar una tarjeta Mini PCI.

Se desarrollaron muchos dispositivos Mini PCI como Wi-Fi, Fast Ethernet, Bluetooth, módems (a menudo Winmodems), tarjetas de sonido, aceleradores criptográficos, SCSI, IDE–ATA, controladores SATA y tarjetas combinadas. Las tarjetas mini PCI se pueden utilizar con hardware regular equipado con PCI, utilizando convertidores Mini PCI a PCI. Mini PCI ha sido reemplazada por la mucho más estrecha PCI Express Mini Card

Detalles técnicos de Mini PCI

Las minitarjetas PCI tienen un consumo de energía máximo de 2 W, lo que limita la funcionalidad que se puede implementar en este factor de forma. También se requieren para admitir la señal PCI CLKRUN# utilizada para iniciar y detener el reloj PCI con fines de administración de energía.

Hay tres factores de forma de tarjeta: tarjetas Tipo I, Tipo II y Tipo III. El conector de tarjeta utilizado para cada tipo incluye: los tipos I y II utilizan un conector de apilamiento de 100 pines, mientras que el tipo III utiliza un conector de borde de 124 pines, es decir, el conector para los tipos I y II difiere del tipo III, donde el conector está en el borde de una tarjeta, como con un SO-DIMM. Los 24 pines adicionales proporcionan las señales adicionales necesarias para enrutar las E/S de regreso a través del conector del sistema (audio, AC-Link, LAN, interfaz de línea telefónica). Las tarjetas de tipo II tienen conectores montados RJ11 y RJ45. Estas tarjetas deben ubicarse en el borde de la computadora o estación de acoplamiento para que los puertos RJ11 y RJ45 puedan montarse para acceso externo.

| Tipo | Tarjeta borde exterior sistema anfitrión | Conector | Tamaño (mm × mm × mm) | Comentarios |

|---|---|---|---|---|

| IA | No | 100-pin apilación | 7.5 × 70 × 45 | Gran dimensión Z (7,5 mm) |

| IB | 5,5 × 70 × 45 | Dimensión Z más pequeña (5,5 mm) | ||

| IIA | Sí. | 17.44 × 70 × 45 | Gran dimensión Z (17,44 mm) | |

| IIB | 5,5 × 78 × 45 | Dimensión Z más pequeña (5,5 mm) | ||

| IIIA | No | 124-pin tarjeta | 2.4 × 59.6 × 50.95 | Dimensión Y más grande (50,95 mm) |

| IIIB | 2.4 × 59.6 × 44.6 | Dimensión Y más pequeña (44,6 mm) |

Mini PCI es distinto de Micro PCI de 144 pines.

Transacciones de bus PCI

El tráfico del bus PCI consta de una serie de transacciones del bus PCI. Cada transacción consta de una fase de dirección seguida de una o más fases de datos. La dirección de las fases de datos puede ser desde el iniciador hasta el destino (transacción de escritura) o viceversa (transacción de lectura), pero todas las fases de datos deben estar en la misma dirección. Cualquiera de las partes puede pausar o detener las fases de datos en cualquier momento. (Un ejemplo común es un dispositivo PCI de bajo rendimiento que no admite transacciones en ráfaga y siempre detiene una transacción después de la primera fase de datos).

Cualquier dispositivo PCI puede iniciar una transacción. Primero, debe solicitar permiso de un árbitro de bus PCI en la placa base. El árbitro otorga permiso a uno de los dispositivos solicitantes. El iniciador comienza la fase de dirección transmitiendo una dirección de 32 bits más un código de comando de 4 bits, luego espera a que responda un objetivo. Todos los demás dispositivos examinan esta dirección y uno de ellos responde unos ciclos más tarde.

El direccionamiento de 64 bits se realiza mediante una fase de direccionamiento de dos etapas. El iniciador transmite los 32 bits de dirección bajos, acompañados de un "ciclo de dirección dual" código de comando. Los dispositivos que no admiten el direccionamiento de 64 bits simplemente no pueden responder a ese código de comando. El siguiente ciclo, el iniciador transmite los 32 bits de dirección altos, más el código de comando real. La transacción opera de manera idéntica a partir de ese momento. Para garantizar la compatibilidad con dispositivos PCI de 32 bits, está prohibido utilizar un ciclo de dirección dual si no es necesario, es decir, si los bits de dirección de orden superior son todos cero.

Mientras que el bus PCI transfiere 32 bits por fase de datos, el iniciador transmite 4 señales de habilitación de bytes bajos activos que indican qué bytes de 8 bits se deben considerar significativos. En particular, una escritura debe afectar solo a los bytes habilitados en el dispositivo PCI de destino. Son de poca importancia para las lecturas de memoria, pero las lecturas de E/S pueden tener efectos secundarios. El estándar PCI permite explícitamente una fase de datos sin bytes habilitados, que debe comportarse como no operativo.

Espacios de direcciones PCI

PCI tiene tres espacios de direcciones: memoria, dirección de E/S y configuración.

Las direcciones de memoria tienen un tamaño de 32 bits (opcionalmente, 64 bits), admiten el almacenamiento en caché y pueden ser transacciones en ráfaga.

Las direcciones de E/S son para compatibilidad con el espacio de direcciones del puerto de E/S de la arquitectura Intel x86. Aunque la especificación del bus PCI permite transacciones en ráfaga en cualquier espacio de direcciones, la mayoría de los dispositivos solo lo admiten para direcciones de memoria y no para E/S.

Finalmente, el espacio de configuración PCI brinda acceso a 256 bytes de registros de configuración especiales por dispositivo PCI. Cada ranura PCI tiene su propio rango de direcciones de espacio de configuración. Los registros se utilizan para configurar la memoria de los dispositivos y los rangos de direcciones de E/S a los que deben responder desde los iniciadores de transacciones. Cuando una computadora se enciende por primera vez, todos los dispositivos PCI responden solo a sus accesos al espacio de configuración. El BIOS de la computadora busca dispositivos y les asigna rangos de direcciones de memoria y E/S.

Si ningún dispositivo reclama una dirección, la fase de dirección del iniciador de la transacción expirará y el iniciador cancelará la operación. En caso de lecturas, se acostumbra proporcionar todos unos para el valor de datos de lectura (0xFFFFFFFF) en este caso. Por lo tanto, los dispositivos PCI generalmente intentan evitar el uso del valor de todos unos en registros de estado importantes, de modo que el software pueda detectar fácilmente dicho error.

Códigos de comando PCI

Hay 16 códigos de comando de 4 bits posibles y 12 de ellos están asignados. Con la excepción del ciclo de dirección dual único, el bit menos significativo del código de comando indica si las siguientes fases de datos son de lectura (datos enviados desde el objetivo al iniciador) o de escritura (datos enviados desde un iniciador al objetivo). Los destinos PCI deben examinar el código de comando así como la dirección y no responder a las fases de dirección que especifican un código de comando no compatible.

Los comandos que hacen referencia a las líneas de caché dependen de que el registro de tamaño de línea de caché del espacio de configuración PCI esté configurado correctamente; no se pueden utilizar hasta que se haya hecho.

- 0000: Reconocimiento interrumpido

- Esta es una forma especial de ciclo de lectura dirigida implícitamente al controlador de interrupción, que devuelve un vector de interrupción. Se ignora el campo de dirección de 32 bits. Una posible implementación es generar un ciclo de reconocimiento interrumpido en un autobús ISA usando un puente de autobús PCI/ISA. Este comando es para compatibilidad con IBM PC; si no hay un controlador de interrupción de estilo Intel 8259 en el bus PCI, este ciclo nunca necesita ser utilizado.

- 0001: Ciclo especial

- Este ciclo es una emisión especial de eventos del sistema que la tarjeta PCI puede estar interesada. El campo de dirección de un ciclo especial es ignorado, pero es seguido por una fase de datos que contiene un mensaje de carga útil. Los mensajes actualmente definidos anuncian que el procesador se detiene por alguna razón (por ejemplo, para ahorrar energía). Ningún dispositivo nunca responde a este ciclo; siempre se termina con un master abort después de dejar los datos en el autobús por lo menos 4 ciclos.

- 0010: I/O Read

- Esto realiza una lectura del espacio I/O. Se proporcionan los 32 bits de la dirección de lectura, de manera que un dispositivo puede (por razones de compatibilidad) implementar menos de 4 bytes de registro I/O. Si el byte permite solicitar datos no dentro del rango de dirección soportado por el dispositivo PCI (por ejemplo, un 4 bytes leído desde un dispositivo que solo admite 2 bytes de espacio de direcciones I/O), debe terminarse con un aborto objetivo. Se permiten múltiples ciclos de datos, utilizando pedidos lineales (aumento simple).

- El estándar PCI está desalentando el uso del espacio I/O en nuevos dispositivos, prefiriendo que tanto como sea posible se haga mediante el mapeo de memoria principal.

- 0011: I/O Write

- Esto realiza una escritura al espacio I/O.

- 010x: Reservado

- Un dispositivo PCI no debe responder a un ciclo de dirección con estos códigos de comandos.

- 0110: Memoria Leer

- Esto realiza un ciclo de lectura desde el espacio de memoria. Debido a que el espacio de memoria más pequeño que un dispositivo PCI se permite implementar es de 16 bytes, los dos bits menos significativos de la dirección no son necesarios durante la fase de dirección; la información equivalente llegará durante las fases de datos en forma de byte señales selectas. En cambio, especifican el orden en el que se deben devolver los datos de la explosión. Si un dispositivo no soporta el pedido solicitado, debe proporcionar la primera palabra y luego desconectar.

- Si un espacio de memoria está marcado como "prefetchable", entonces el dispositivo objetivo debe ignorar las señales selectas byte en una memoria leída y devolver siempre 32 bits válidos.

- 0111: Memory Write

- Esto funciona de forma similar a una memoria leída. Las señales selectas byte son más importantes en una escritura, ya que los bytes no seleccionados no deben ser escritos a la memoria.

- Generalmente, PCI escribe son más rápidos de lo que dice PCI, porque un dispositivo puede amortiguar los datos de escritura entrantes y soltar el autobús más rápido. Para leer, debe retrasar la fase de datos hasta que los datos hayan sido recogidos.

- 100x: Reservado

- Un dispositivo PCI no debe responder a un ciclo de dirección con estos códigos de comandos.

- 1010: Configuración Leer

- Esto es similar a una lectura I/O, pero lee desde el espacio de configuración PCI. Un dispositivo debe responder sólo si los 11 bits bajos de la dirección especifican una función y registran que implementa, y si se afirma la señal IDSEL especial. Debe ignorar los 21 bits altos. Se permite que Burst lea (usando incrementos lineales) en el espacio de configuración PCI.

- A diferencia del espacio I/O, los registros estándar de configuración PCI se definen para que las lecturas nunca alteren el estado del dispositivo. Es posible que un dispositivo tenga registros de espacio de configuración más allá de los 64 bytes estándar que han leído efectos secundarios, pero esto es raro.

- Los accesos al espacio de configuración suelen tener algunos ciclos de retraso para permitir que las líneas IDSEL se estabilicen, lo que las hace más lentas que otras formas de acceso. Además, un acceso al espacio de configuración requiere una operación de varios pasos en lugar de una sola instrucción de máquina. Por lo tanto, es mejor evitarlos durante el funcionamiento rutinario de un dispositivo PCI.

- 1011: Configuration Write

- Esto opera analógicamente a una configuración leída.

- 1100: Lección de memoria Múltiple

- Este comando es idéntico a una memoria genérica leída, pero incluye el indicio de que una larga ráfaga de lectura continuará más allá del final de la línea de caché actual, y el objetivo debe prefetch internamente una gran cantidad de datos. Un objetivo siempre se permite considerar este sinónimo para una memoria genérica leída.

- 1101: Ciclo de doble dirección

- Al acceder a una dirección de memoria que requiere más de 32 bits para representar, la fase de dirección comienza con este comando y los 32 bits bajos de la dirección, seguido de un segundo ciclo con el comando real y los 32 bits altos de la dirección. Los objetivos PCI que no soportan el tratamiento de 64 bits pueden simplemente tratar esto como otro código de comando reservado y no responder a él. Este código de comandos sólo se puede utilizar con una palabra de dirección no cero de alta orden; está prohibido utilizar este ciclo si no es necesario.

- 1110: Línea de lectura de memoria

- Este comando es idéntico a una memoria genérica leída, pero incluye la pista de que la lectura continuará hasta el final de la línea de caché. Un objetivo siempre se permite considerar este sinónimo para una memoria genérica leída.

- 1111: Memory Write e Invalidate

- Este comando es idéntico a un escrito de memoria genérico, pero viene con la garantía de que una o más líneas de caché enteras serán escritas, con todos los selectos byte habilitados. Esta es una optimización para los caches de la espalda que azotan el autobús. Normalmente, un caché de devolución que contiene datos sucios debe interrumpir la operación de escritura lo suficiente como para escribir sus propios datos sucios primero. Si el escrito se realiza utilizando este comando, los datos que se escriben de nuevo se garantizan a ser irrelevantes, y pueden simplemente ser invalidados en el caché de devolución.

- Esta optimización sólo afecta al caché de snooping, y no diferencia al objetivo, que puede tratar esto como un sinónimo para el comando de escritura de memoria.

Latencia del bus PCI

Poco después de la promulgación de la especificación PCI, se descubrió que las transacciones prolongadas de algunos dispositivos, debido a reconocimientos lentos, ráfagas de datos prolongadas o alguna combinación, podían causar una insuficiencia o sobrecarga del búfer en otros dispositivos. Las recomendaciones sobre el momento de las fases individuales en la Revisión 2.0 se hicieron obligatorias en la revisión 2.1:

- Un objetivo debe ser capaz de completar la fase inicial de datos (afirmar TRDY# y/o STOP#) dentro de 16 ciclos del inicio de una transacción.

- Un iniciador debe completar cada fase de datos (afirmar IRDY#) dentro de 8 ciclos.

Además, a partir de la revisión 2.1, todos los iniciadores capaces de generar más de dos fases de datos deben implementar un temporizador de latencia programable. El temporizador comienza a contar los ciclos de reloj cuando se inicia una transacción (el iniciador afirma FRAME#). Si el temporizador ha expirado y el árbitro ha eliminado GNT#, entonces el iniciador debe terminar la transacción en la próxima oportunidad legal. Esta suele ser la siguiente fase de datos, pero las transacciones de escritura e invalidación de memoria deben continuar hasta el final de la línea de caché.

Transacciones retrasadas

Los dispositivos que no pueden cumplir con esas restricciones de tiempo deben usar una combinación de escrituras publicadas (para escrituras en memoria) y transacciones retrasadas (para otras escrituras y todas las lecturas). En una transacción retrasada, el objetivo registra la transacción (incluidos los datos de escritura) internamente y aborta (afirma STOP# en lugar de TRDY#) la primera fase de datos. El iniciador debe volver a intentar exactamente la misma transacción más tarde. Mientras tanto, el objetivo realiza internamente la transacción y espera la transacción reintentada. Cuando se ve la transacción reintentada, se entrega el resultado almacenado en búfer.

Un dispositivo puede ser el objetivo de otras transacciones mientras completa una transacción retrasada; debe recordar el tipo de transacción, la dirección, las selecciones de bytes y (si es una escritura) el valor de los datos, y solo completar la transacción correcta.

Si el objetivo tiene un límite en la cantidad de transacciones retrasadas que puede registrar internamente (los objetivos simples pueden imponer un límite de 1), obligará a esas transacciones a reintentarlas sin registrarlas. Se tratarán cuando se complete la transacción retrasada actual. Si dos iniciadores intentan la misma transacción, una transacción retrasada iniciada por uno puede tener su resultado entregado al otro; esto es inofensivo

Un objetivo abandona una transacción retrasada cuando un reintento logra entregar el resultado almacenado en el búfer, el bus se reinicia o cuando transcurren 215=32768 ciclos de reloj (aproximadamente 1 ms) sin ver un reintento. Esto último nunca debería suceder en el funcionamiento normal, pero evita un interbloqueo de todo el bus si un iniciador se reinicia o funciona mal.

Puentes de bus PCI

El estándar PCI permite conectar varios buses PCI independientes mediante puentes de bus que reenviarán las operaciones de un bus a otro cuando sea necesario. Aunque PCI tiende a no usar muchos puentes de bus, los sistemas PCI Express usan muchos puentes PCI a PCI generalmente llamados Puerto raíz PCI Express; cada ranura PCI Express parece ser un bus separado, conectado por un puente a los demás. El puente de host PCI (generalmente puente norte en plataformas x86) se interconecta entre la CPU, la memoria principal y el bus PCI.

Escritos publicados

Por lo general, cuando un puente de bus ve una transacción en un bus que debe reenviarse al otro, la transacción original debe esperar hasta que se complete la transacción reenviada antes de que el resultado esté listo. Se produce una excepción notable en el caso de las escrituras de memoria. Aquí, el puente puede registrar los datos de escritura internamente (si tiene espacio) y señalar la finalización de la escritura antes de que se complete la escritura reenviada. O, de hecho, antes de que haya comenzado. Tal "enviado pero aún no llegado" las escrituras se denominan "escrituras publicadas", por analogía con un mensaje de correo postal. Aunque ofrecen una gran oportunidad para mejorar el rendimiento, las reglas que rigen lo que está permitido son un tanto intrincadas.

Combinar, fusionar y colapsar

El estándar PCI permite que los puentes de bus conviertan varias transacciones de bus en una transacción mayor en determinadas situaciones. Esto puede mejorar la eficiencia del bus PCI.

- Combinación

- Escribir transacciones a direcciones consecutivas puede combinarse en un escrito de ráfaga más largo, siempre y cuando el orden de los accesos en la ráfaga sea el mismo que el orden de los escritos originales. Es permisible insertar fases extra de datos con todos byte permite apagarse si los escritos son casi consecutivos.

- Fusión

- Múltiples escritos para descomponer partes de la misma palabra pueden fusionarse en un solo escrito con múltiples byte permite afirmarse. En este caso, los escritos que fueron presentados al puente de autobuses en un orden particular se fusionan para que ocurran al mismo tiempo cuando se envían.

- Colapso

- Múltiples escritos al mismo byte o bytes pueden no ser combinado, por ejemplo, realizando sólo la segunda escritura y saltando el primer escrito que fue sobrescrito. Esto se debe a que la especificación PCI permite escribir para tener efectos secundarios.

Señales de bus PCI

Las transacciones del bus PCI están controladas por cinco señales de control principales, dos impulsadas por el iniciador de una transacción (FRAME# e IRDY#) y tres impulsadas por el destino (DEVSEL#, TRDY# y STOP#). Hay dos señales de arbitraje adicionales (REQ# y GNT#) que se utilizan para obtener permiso para iniciar una transacción. Todos son activos-bajos, lo que significa que el estado activo o afirmado es un voltaje bajo. Las resistencias pull-up en la placa base aseguran que permanecerán altas (inactivas o desactivadas) si no están activadas por ningún dispositivo, pero el bus PCI no depende de las resistencias para cambiar el nivel de la señal; todos los dispositivos elevan las señales durante un ciclo antes de dejar de transmitir las señales.

Temporización de la señal

Todas las señales del bus PCI se muestrean en el flanco ascendente del reloj. Las señales cambian nominalmente en el flanco descendente del reloj, dando a cada dispositivo PCI aproximadamente medio ciclo de reloj para decidir cómo responder a las señales que observó en el flanco ascendente, y medio ciclo de reloj para transmitir su respuesta al otro dispositivo..

El bus PCI requiere que cada vez que el dispositivo que maneja una señal de bus PCI cambie, debe transcurrir un ciclo de respuesta entre el momento en que un dispositivo deja de conducir la señal y el otro dispositivo se inicia. Sin esto, podría haber un período en el que ambos dispositivos estuvieran conduciendo la señal, lo que interferiría con la operación del autobús.

La combinación de este ciclo de respuesta y el requisito de conducir una línea de control alta durante un ciclo antes de dejar de funcionar significa que cada una de las líneas de control principales debe estar alta durante un mínimo de dos ciclos al cambiar de propietario. El protocolo de bus PCI está diseñado para que esto rara vez sea una limitación; solo en unos pocos casos especiales (en particular, transacciones consecutivas rápidas) es necesario insertar un retraso adicional para cumplir con este requisito.

Arbitraje

Cualquier dispositivo en un bus PCI que sea capaz de actuar como maestro de bus puede iniciar una transacción con cualquier otro dispositivo. Para garantizar que solo se inicie una transacción a la vez, cada maestro primero debe esperar una señal de concesión de bus, GNT#, de un árbitro ubicado en la placa base. Cada dispositivo tiene una línea de solicitud separada REQ# que solicita el bus, pero el árbitro puede "estacionar" la señal de concesión de bus en cualquier dispositivo si no hay solicitudes actuales.

El árbitro puede eliminar GNT# en cualquier momento. Un dispositivo que pierde GNT# puede completar su transacción actual, pero no puede iniciar una (afirmando FRAME#) a menos que observe que GNT# afirmó el ciclo antes de que comience.

El árbitro también puede proporcionar GNT# en cualquier momento, incluso durante la transacción de otro maestro. Durante una transacción, se afirma FRAME# o IRDY# o ambos; cuando ambos son anulados, el autobús está inactivo. Un dispositivo puede iniciar una transacción en cualquier momento en que se afirma GNT# y el bus está inactivo.

Fase de dirección

Una transacción de bus PCI comienza con una fase de dirección. El iniciador, al ver que tiene GNT# y que el bus está inactivo, dirige la dirección de destino a las líneas AD[31:0], el comando asociado (por ejemplo, lectura de memoria o escritura de E/S) en C/BE[3:0]# líneas y tira de FRAME# hacia abajo.

Cada uno de los demás dispositivos examina la dirección y el comando y decide si responder como el objetivo afirmando DEVSEL#. Un dispositivo debe responder afirmando DEVSEL# dentro de 3 ciclos. Se dice que los dispositivos que prometen responder en 1 o 2 ciclos tienen "fast DEVSEL" o "DEVSEL medio", respectivamente. (En realidad, el tiempo de respuesta es de 2,5 ciclos, ya que los dispositivos PCI deben transmitir todas las señales medio ciclo antes para poder recibirlas tres ciclos más tarde).

Tenga en cuenta que un dispositivo debe bloquear la dirección en el primer ciclo; se requiere que el iniciador elimine la dirección y el comando del bus en el siguiente ciclo, incluso antes de recibir una respuesta DEVSEL#. El tiempo adicional está disponible solo para interpretar la dirección y el comando después de capturarlo.

En el quinto ciclo de la fase de dirección (o antes si todos los demás dispositivos tienen un DEVSEL medio o más rápido), una "decodificación sustractiva" está permitido para algunos rangos de direcciones. Esto es comúnmente utilizado por un puente de bus ISA para direcciones dentro de su rango (24 bits para memoria y 16 bits para E/S).

En el sexto ciclo, si no ha habido respuesta, el iniciador puede abortar la transacción anulando FRAME#. Esto se conoce como terminación de aborto maestro y es habitual que los puentes de bus PCI devuelvan datos todos unos (0xFFFFFFFF) en este caso. Por lo tanto, los dispositivos PCI generalmente están diseñados para evitar el uso del valor de todos unos en registros de estado importantes, de modo que el software pueda detectar fácilmente dicho error.

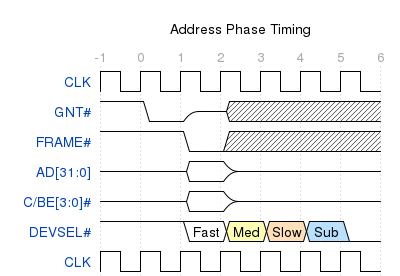

Tiempo de fase de dirección

Notas:

- GNT# Irrelevant after cycle has started

- La dirección sólo es válida para un ciclo.

- C/BE proporcionará el comando siguiente por primera fase de byte de datos

En el flanco ascendente del reloj 0, el iniciador observa FRAME# e IRDY# tanto altos como GNT# bajo, por lo que impulsa la dirección, el comando y afirma FRAME# a tiempo para el flanco ascendente del reloj 1. Objetivos enganche la dirección y comience a decodificarla. Pueden responder con DEVSEL# a tiempo para el reloj 2 (DEVSEL rápido), 3 (medio) o 4 (lento). Los dispositivos de decodificación sustractiva, al no ver otra respuesta en el reloj 4, pueden responder en el reloj 5. Si el maestro no ve una respuesta en el reloj 5, finalizará la transacción y eliminará FRAME# en el reloj 6.

TRDY# y STOP# se anulan (alto) durante la fase de dirección. El iniciador puede afirmar IRDY# tan pronto como esté listo para transferir datos, lo que teóricamente podría ser tan pronto como el reloj 2.

Dirección de doble ciclo

Para permitir el direccionamiento de 64 bits, un maestro presentará la dirección durante dos ciclos consecutivos. En primer lugar, envía los bits de dirección de orden inferior con una "dirección de doble ciclo" comando en C/BE[3:0]#. En el ciclo siguiente, envía los bits de dirección de orden superior y el comando real. Los ciclos de dirección dual están prohibidos si los bits de dirección de orden superior son cero, por lo que los dispositivos que no admiten el direccionamiento de 64 bits pueden simplemente no responder a los comandos de ciclo dual.

_ 0_ 1_ 2_ 3_ 4_ 5_ 6_ CLK _/ _/ _/ _/ _/ _/ _/ _/ _/ __ GNT# __/XXXXXXXXXXXXXXXXXXXXXXX _______ FRAME# _________________________________________________________________ _____ AD[31:0] ------------------------------- (Abajo, luego pedazos altos) ________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________ C/BE[3:0]# ---------------traducido_____________________ (DAC, luego comando real) ________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________ DEVSEL# ___________ Despacio rápido _ CLK _/ _/ _/ _/ _/ _/ _/ _/ _/ 0 1 2 3 4 5 6

Configuración de acceso

Las direcciones para el acceso al espacio de configuración PCI se descodifican especialmente. Para estos, las líneas de dirección de orden inferior especifican el desplazamiento del registro de configuración PCI deseado y las líneas de dirección de orden superior se ignoran. En cambio, una señal de dirección adicional, la entrada IDSEL, debe estar alta antes de que un dispositivo pueda afirmar DEVSEL#. Cada ranura conecta una línea de dirección de orden superior diferente al pin IDSEL y se selecciona utilizando una codificación one-hot en las líneas de dirección superiores.

Fases de datos

Después de la fase de dirección (específicamente, comenzando con el ciclo en el que DEVSEL# baja) viene una ráfaga de una o más fases de datos. En todos los casos, el iniciador impulsa señales de selección de byte bajo activo en las líneas C/BE[3:0]#, pero los datos en AD[31:0] pueden ser controlados por el iniciador (en caso de escrituras) o objetivo (en caso de lecturas).

Durante las fases de datos, las líneas C/BE[3:0]# se interpretan como habilitaciones de bytes bajos activos. En caso de una escritura, las señales afirmadas indican cuál de los cuatro bytes en el bus AD se escribirá en la ubicación direccionada. En el caso de una lectura, indican en qué bytes está interesado el iniciador. Para las lecturas, siempre es legal ignorar las señales de habilitación de bytes y simplemente devolver los 32 bits; Se requieren recursos de memoria caché para devolver siempre 32 bits válidos. Las habilitaciones de byte son principalmente útiles para accesos al espacio de E/S donde las lecturas tienen efectos secundarios.

El estándar PCI permite explícitamente una fase de datos con las cuatro líneas C/BE# anuladas, y no debe tener ningún efecto en el destino que no sea avanzar la dirección en el acceso de ráfaga en curso.

La fase de datos continúa hasta que ambas partes estén listas para completar la transferencia y continuar con la siguiente fase de datos. El iniciador afirma IRDY# (iniciador listo) cuando ya no necesita esperar, mientras que el objetivo afirma TRDY# (objetivo listo). Cualquiera que sea el lado que proporcione los datos, debe conducirlos en el bus AD antes de afirmar su señal de listo.

Una vez que uno de los participantes afirma su señal de listo, no puede dejar de estar listo ni alterar sus señales de control hasta el final de la fase de datos. El destinatario de los datos debe enclavar el bus AD en cada ciclo hasta que vea IRDY# y TRDY# afirmados, lo que marca el final de la fase de datos actual e indica que los datos recién enclavados son la palabra que se transferirá.

Para mantener la velocidad de ráfaga completa, el remitente de datos tiene medio ciclo de reloj después de ver IRDY# y TRDY# afirmados para enviar la siguiente palabra al bus AD.

0_ 1_ 2_ 3_ 4_ 5_ 7_ 8_ 9_ CLK _/ _/ _/ _/ _/ _/ _/ _/ _/ _/ _/ __ ________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________ AD[31:0] -... (Si escribe) ________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________ AD[31:0] -... (Si lee) __ ________________ ________________________________________________________________________________________ C/BE[3:0]# -... (Debe ser siempre válido) ________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________ IRDY# x_________________________________________________________________ ___________________________________________________________________________________________________ TRDY# x x___________________________________________________________________________________________ _________________ DEVSEL# #____________________________________ ___ Silencio Silencio FRAME# __________________________________________ _ CLK _/ _/ _/ _/ _/ _/ _/ _/ _/ _/ _/ 0 1 2 3 4 5 6 7 8 9

Esto continúa el ciclo de dirección ilustrado arriba, asumiendo un solo ciclo de dirección con DEVSEL medio, por lo que el objetivo responde a tiempo para el reloj 3. Sin embargo, en ese momento, ninguna de las partes está lista para transferir datos. Para el reloj 4, el iniciador está listo, pero el objetivo no. En el reloj 5, ambos están listos y tiene lugar una transferencia de datos (como lo indican las líneas verticales). Para el reloj 6, el objetivo está listo para transferir, pero el iniciador no. En el reloj 7, el iniciador está listo y se transfieren los datos. Para los relojes 8 y 9, ambos lados permanecen listos para transferir datos y los datos se transfieren a la velocidad máxima posible (32 bits por ciclo de reloj).

En caso de una lectura, el reloj 2 se reserva para dar la vuelta al bus AD, por lo que el objetivo no puede conducir datos en el bus incluso si es capaz de DEVSEL rápido.

Fast DEVSEL# en lecturas

En teoría, un objetivo que admita DEVSEL rápido podría comenzar a responder a un ciclo de lectura después de que se presente la dirección. Sin embargo, este ciclo está reservado para el giro del autobús AD. Por lo tanto, es posible que un objetivo no controle el bus AD (y, por lo tanto, no pueda afirmar TRDY#) en el segundo ciclo de una transacción. Tenga en cuenta que la mayoría de los objetivos no serán tan rápidos y no necesitarán ninguna lógica especial para hacer cumplir esta condición.

Terminar transacciones

Cualquier lado puede solicitar que finalice una ráfaga después de la fase de datos actual. Los dispositivos PCI simples que no admiten ráfagas de varias palabras siempre lo solicitarán de inmediato. Incluso los dispositivos que admiten ráfagas tendrán algún límite en la longitud máxima que pueden admitir, como el final de su memoria direccionable.

Terminación de ráfaga de iniciador

El iniciador puede marcar cualquier fase de datos como la final de una transacción anulando FRAME# al mismo tiempo que afirma IRDY#. El ciclo después de que el objetivo afirma TRDY#, la transferencia de datos final se completa, ambos lados anulan sus respectivas señales RDY# y el bus vuelve a estar inactivo. El maestro no puede anular la afirmación de FRAME# antes de afirmar IRDY#, ni tampoco puede anular la afirmación de FRAME# mientras espera, con IRDY# afirmado, a que el destino confirme TRDY#.

La única excepción menor es una terminación de cancelación maestra, cuando ningún objetivo responde con DEVSEL#. Obviamente, no tiene sentido esperar TRDY# en tal caso. Sin embargo, incluso en este caso, el maestro debe afirmar IRDY# durante al menos un ciclo después de anular la confirmación de FRAME#. (Comúnmente, un maestro afirmará IRDY# antes de recibir DEVSEL#, por lo que simplemente debe mantener IRDY# afirmado durante un ciclo más).

Terminación de ráfaga de destino

El objetivo solicita al iniciador que finalice una ráfaga afirmando STOP#. El iniciador luego finalizará la transacción al anular la afirmación de FRAME# en la próxima oportunidad legal; si desea transferir más datos, continuará en una transacción separada. Hay varias maneras para que el objetivo haga esto:

- Desconectarse con datos

- Si el objetivo afirma STOP# y TRDY# al mismo tiempo, esto indica que el objetivo desea que sea la última fase de datos. Por ejemplo, un objetivo que no apoye las transferencias de ráfagas siempre hará esto para forzar transacciones PCI de una sola palabra. Esta es la forma más eficiente para que un objetivo termine una explosión.

- Desconexión sin datos

- Si el objetivo afirma STOP# sin afirmar TRDY#, esto indica que el objetivo desea parar sin transferir datos. STOP# se considera equivalente a TRDY# con el fin de terminar una fase de datos, pero no se transfiere ningún dato.

- Retry

- Una desconexión sin datos antes de transferir datos es un retry, y a diferencia de otras transacciones de PCI, los iniciadores de PCI deben pausar ligeramente antes de continuar la operación. Vea la especificación PCI para detalles.

- Objetivo abortado

- Normalmente, un objetivo mantiene DEVSEL# afirmado a través de la última fase de datos. Sin embargo, si un objetivo desmonta DEVSEL# antes de desconectar sin datos (afirmando STOP#), esto indica un Objetivo abortado, que es una condición de error fatal. El iniciador puede no volver a entrar, y generalmente lo trata como un error de autobús. Tenga en cuenta que un objetivo no puede desactivar DEVSEL# mientras espera con TRDY# o STOP# bajo; debe hacerlo al comienzo de una fase de datos.

Siempre habrá al menos un ciclo más después de una desconexión iniciada por el objetivo, para permitir que el maestro anule la afirmación de FRAME#. Hay dos subcasos, que toman la misma cantidad de tiempo, pero uno requiere una fase de datos adicional:

- Desconexión-A

- Si el iniciador observa STOP# antes de afirmar su propio IRDY#, entonces puede terminar la explosión desactivando el FRAME# al mismo tiempo que afirma IRDY#, terminando la explosión después de la fase actual de datos.

- Desconexión-B

- Si el iniciador ya ha afirmado IRDY# (sin desactivar FRAME#) en el momento en que observa el STOP# del objetivo, se compromete a una fase adicional de datos. El objetivo debe esperar a través de una fase de datos adicional, manteniendo STOP# afirmado sin TRDY#, antes de que la transacción pueda terminar.

Si el iniciador finaliza la ráfaga al mismo tiempo que el objetivo solicita la desconexión, no hay ciclo de bus adicional.

Direccionamiento en ráfaga

Para accesos al espacio de memoria, se puede acceder a las palabras de una ráfaga en varios órdenes. Los bits de dirección de orden inferior innecesarios AD[1:0] se utilizan para transmitir la orden solicitada por el iniciador. Un destino que no admita un orden en particular debe terminar la ráfaga después de la primera palabra. Algunas de estas órdenes dependen del tamaño de la línea de caché, que se puede configurar en todos los dispositivos PCI.

| A[1] | A[0] | Orden de Burst (con línea de caché de 16 bytes) |

|---|---|---|

| 0 | 0 | Incremento lineal (0x0C, 0x10, 0x14, 0x18, 0x1C,...) |

| 0 | 1 | Cacheline toggle (0x0C, 0x08, 0x04, 0x00, 0x1C, 0x18,...) |

| 1 | 0 | Cacheline wrap (0x0C, 0x00, 0x04, 0x08, 0x1C, 0x10,...) |

| 1 | 1 | Reservado (desconectado después de la primera transferencia) |

Si el desplazamiento inicial dentro de la línea de caché es cero, todos estos modos se reducen al mismo orden.

Los modos de cambio de línea de caché y ajuste de línea de caché son dos formas de obtención de línea de caché de palabra crítica primero. El modo de alternancia aplica XOR a la dirección suministrada con un contador incremental. Este es el orden nativo de los procesadores Intel 486 y Pentium. Tiene la ventaja de que no es necesario conocer el tamaño de línea de caché para implementarlo.

La versión 2.1 de PCI dejó obsoleto el modo de alternar y agregó el modo de ajuste de línea de caché, en el que la búsqueda se realiza de forma lineal y se ajusta al final de cada línea de caché. Cuando una línea de caché se obtiene por completo, la búsqueda salta al desplazamiento inicial en la siguiente línea de caché.

Tenga en cuenta que la mayoría de los dispositivos PCI solo admiten una gama limitada de tamaños de línea de caché típicos; si el tamaño de la línea de caché está programado en un valor inesperado, fuerzan el acceso de una sola palabra.

PCI también admite acceso en ráfagas a E/S y espacio de configuración, pero solo se admite el modo lineal. (Esto rara vez se usa y puede tener errores en algunos dispositivos; es posible que no lo admitan, pero tampoco fuercen correctamente el acceso de una sola palabra).

Ejemplos de transacciones

Esta es la ráfaga de escritura de cuatro palabras de mayor velocidad posible, terminada por el maestro:

0_ 1_ 2_ 3_ 4_ 5_ 6_ 7_ CLK _/ _/ _/ _/ _/ _/ _/ _/ _/ _/ _/ ________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________ AD[31:0] --- ________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________ C/BE[3:0]# --- ___ IRDY# ^^^^^^^^^^____________________________________________________________________________________ ___ TRDY# ^^^^^^^^^^^___________________________________________________________ ___ ¿Por qué? ___ _ _ ___ FRAME# #_________________________________ _ CLK _/ _/ _/ _/ _/ _/ _/ _/ _/ _/ _/ 0 1 2 3 4 5 6 7

En el flanco 1 del reloj, el iniciador inicia una transacción mediante la activación de una dirección, un comando y la confirmación del n.º de FOTOGRAMA Las otras señales están inactivas (indicadas por ^^^), elevadas por las resistencias pull-up de la placa base. Ese podría ser su ciclo de recuperación. En el ciclo 2, el objetivo afirma tanto DEVSEL# como TRDY#. Como el iniciador también está listo, se produce una transferencia de datos. Esto se repite durante tres ciclos más, pero antes del último (flanco 5 del reloj), el maestro desactiva el FOTOGRAMA #, lo que indica que este es el final. En el flanco 6 del reloj, el bus AD y el NÚMERO DE MARCO no se activan (ciclo de respuesta) y las otras líneas de control se activan a nivel alto durante 1 ciclo. En el borde del reloj 7, otro iniciador puede iniciar una transacción diferente. Este es también el ciclo de respuesta para las otras líneas de control.

La ráfaga de lectura equivalente toma un ciclo más, porque el destino debe esperar 1 ciclo para que el bus AD cambie antes de que pueda afirmar TRDY#:

0_ 1_ 2_ 3_ 4_ 5_ 7_ 8_ CLK _/ _/ _/ _/ _/ _/ _/ _/ _/ _/ _/ ________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________ AD[31:0] --- __ ________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________ C/BE[3:0]# --- ____ _ _ ____ # IRDY# ^^^^___________________________________________________________________ __________ ________ _____________________________________________________________________ _________________________________________________________________________________________________________________________________________________________________________ TRDY# ^^^^ ________________/ ^^^^^^^^^^ ____ _ _ ____ ¿Por qué? ___ _ _ ___ FRAME# ________________________________________________________________ ↑. _ CLK _/ _/ _/ _/ _/ _/ _/ _/ _/ _/ _/ 0 1 2 3 4 5 6 7 8

Una ráfaga de alta velocidad terminada por el objetivo tendrá un ciclo adicional al final:

0_ 1_ 2_ 3_ 4_ 5_ 7_ 8_ CLK _/ _/ _/ _/ _/ _/ _/ _/ _/ _/ _/ ________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________ AD[31:0] ------------- __ ________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________ C/BE[3:0]# -... ___ IRDY# ^^^^^^^^^________________________________________ _________________________________________________________________________________________________________ _______________________________________________________________________________________________________________________________________________________ TRDY# ^^^^^^^^ __________________/ ________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________ Parar # ^^^^^^^^ Silencio Silencio ___ ¿Por qué? ____ _ _ ____ FRAME# _____________________________/ ^^^^^^ _ CLK _/ _/ _/ _/ _/ _/ _/ _/ _/ _/ _/ 0 1 2 3 4 5 6 7 8

En el flanco 6 del reloj, el objetivo indica que quiere detenerse (con datos), pero el iniciador ya mantiene IRDY# bajo, por lo que hay una quinta fase de datos (flanco 7 del reloj), durante la cual no se transfieren datos..

Paridad

El bus PCI detecta errores de paridad, pero no intenta corregirlos reintentando las operaciones; es puramente una indicación de falla. Debido a esto, no hay necesidad de detectar el error de paridad antes de que ocurra, y el bus PCI lo detecta unos ciclos más tarde. Durante una fase de datos, cualquier dispositivo que esté manejando las líneas AD[31:0] calcula incluso la paridad sobre ellas y las líneas C/BE[3:0]#, y las envía a la línea PAR un ciclo más tarde. Todas las reglas de acceso y ciclos de respuesta del bus AD se aplican a la línea PAR, solo un ciclo después. El dispositivo que escucha en el bus AD verifica la paridad recibida y afirma la línea PERR# (error de paridad) un ciclo después de eso. Esto generalmente genera una interrupción del procesador, y el procesador puede buscar en el bus PCI el dispositivo que detectó el error.

La línea PERR# solo se usa durante las fases de datos, una vez que se ha seleccionado un objetivo. Si se detecta un error de paridad durante una fase de dirección (o la fase de datos de un ciclo especial), los dispositivos que lo observan afirman la línea SERR# (Error del sistema).

Incluso cuando algunos bytes están enmascarados por las líneas C/BE# y no están en uso, aún deben tener algún valor definido, y este valor debe usarse para calcular la paridad.

Transacciones consecutivas rápidas

Debido a la necesidad de un ciclo de respuesta entre diferentes dispositivos que controlan las señales del bus PCI, en general, es necesario tener un ciclo inactivo entre las transacciones del bus PCI. Sin embargo, en algunas circunstancias se permite omitir este ciclo inactivo, pasando directamente del ciclo final de una transferencia (IRDY# confirmado, FRAME# desactivado) al primer ciclo de la siguiente (FRAME# activado, IRDY# desactivado).

Un iniciador solo puede realizar transacciones consecutivas cuando:

- son por el mismo iniciador (o no habría tiempo para dar la vuelta a las líneas C/BE# y FRAME#),

- la primera transacción fue una escritura (por lo que no hay necesidad de dar vuelta alrededor del autobús AD), y

- el iniciador todavía tiene permiso (de su entrada GNT#) para utilizar el bus PCI.

Las restricciones de tiempo adicionales pueden provenir de la necesidad de dar la vuelta a las líneas de control de destino, particularmente DEVSEL#. El objetivo anula DEVSEL#, llevándolo alto, en el ciclo que sigue a la fase final de datos, que en el caso de transacciones consecutivas es el primer ciclo de la fase de dirección. El segundo ciclo de la fase de dirección se reserva entonces para el cambio de DEVSEL#, por lo que si el objetivo es diferente del anterior, no debe afirmar DEVSEL# hasta el tercer ciclo (velocidad DEVSEL media).

Un caso en el que este problema no puede surgir es si el iniciador sabe de alguna manera (probablemente porque las direcciones comparten suficientes bits de alto orden) que la segunda transferencia está dirigida al mismo destino que la anterior. En ese caso, puede realizar transacciones consecutivas. Todos los destinos PCI deben admitir esto.

También es posible que el objetivo realice un seguimiento de los requisitos. Si nunca hace DEVSEL rápido, se cumplen trivialmente. Si lo hace, debe esperar hasta el tiempo medio de DEVSEL a menos que:

- la transacción actual fue precedida por un ciclo ocioso (no es retrocedente), o

- la transacción anterior era al mismo objetivo, o

- la transacción actual comenzó con un ciclo de doble dirección.

Los destinos que tienen esta capacidad lo indican mediante un bit especial en un registro de configuración PCI, y si todos los destinos en un bus la tienen, todos los iniciadores pueden usar transferencias consecutivas libremente.

Un puente de bus de decodificación sustractiva debe saber que debe esperar este retraso adicional en el caso de ciclos consecutivos, para anunciar la compatibilidad consecutiva.

PCI de 64 bits

A partir de la revisión 2.1, la especificación PCI incluye soporte opcional de 64 bits. Esto se proporciona a través de un conector extendido que proporciona las extensiones de bus de 64 bits AD[63:32], C/BE[7:4]# y PAR64, y varios pines de tierra y alimentación adicionales. El conector PCI de 64 bits se puede distinguir de un conector de 32 bits por el segmento adicional de 64 bits.

Las transacciones de memoria entre dispositivos de 64 bits pueden usar los 64 bits para duplicar la tasa de transferencia de datos. Las transacciones que no son de memoria (incluida la configuración y los accesos al espacio de E/S) no pueden usar la extensión de 64 bits. Durante una ráfaga de 64 bits, el direccionamiento de ráfagas funciona igual que en una transferencia de 32 bits, pero la dirección se incrementa dos veces por fase de datos. La dirección inicial debe estar alineada con 64 bits; es decir, AD2 debe ser 0. Los datos correspondientes a las direcciones intermedias (con AD2 = 1) se transportan en la mitad superior del bus AD.

Para iniciar una transacción de 64 bits, el iniciador maneja la dirección inicial en el bus AD y afirma REQ64# al mismo tiempo que FRAME#. Si el objetivo seleccionado puede admitir una transferencia de 64 bits para esta transacción, responde afirmando ACK64# al mismo tiempo que DEVSEL#. Tenga en cuenta que un destino puede decidir por transacción si permite una transferencia de 64 bits.

Si se afirma REQ64# durante la fase de dirección, el iniciador también maneja los 32 bits altos de la dirección y una copia del comando de bus en la mitad alta del bus. Si la dirección requiere 64 bits, aún se requiere un ciclo de dirección dual, pero la mitad superior del bus transporta la mitad superior de la dirección y el código de comando final durante ambos ciclos de fase de dirección; esto permite que un objetivo de 64 bits vea la dirección completa y comience a responder antes.

Si el iniciador ve DEVSEL# afirmado sin ACK64#, realiza fases de datos de 32 bits. Los datos que se habrían transferido en la mitad superior del bus durante la primera fase de datos se transfieren en cambio durante la segunda fase de datos. Por lo general, el iniciador maneja los 64 bits de datos antes de ver DEVSEL#. Si falta ACK64#, puede dejar de controlar la mitad superior del bus de datos.

Las líneas REQ64# y ACK64# se mantienen activas durante toda la transacción, salvo la última fase de datos, y se anulan al mismo tiempo que FRAME# y DEVSEL#, respectivamente.

La línea PAR64 funciona igual que la línea PAR, pero ofrece paridad uniforme sobre AD[63:32] y C/BE[7:4]#. Solo es válido para las fases de dirección si se afirma REQ64#. PAR64 solo es válido para las fases de datos si se afirman tanto REQ64# como ACK64#.

Espionaje de caché (obsoleto)

PCI originalmente incluía soporte opcional para coherencia de caché de reescritura. Esto requería el apoyo de objetivos de memoria caché, que escucharían dos pines del caché en el bus, SDONE (snoop done) y SBO# (snoop backoff).

Debido a que esto rara vez se implementó en la práctica, se eliminó de la revisión 2.2 de la especificación PCI y los pines se reutilizaron para el acceso a SMBus en la revisión 2.3.

La memoria caché controlaría todos los accesos a la memoria, sin afirmar DEVSEL#. Si notó un acceso que podría estar en caché, reduciría SDONE (no se hizo snoop). Un objetivo compatible con la coherencia evitaría completar una fase de datos (afirmando TRDY#) hasta que observe SDONE alto.

En el caso de una escritura en datos que estaban limpios en el caché, el caché solo tendría que invalidar su copia y afirmaría SDONE tan pronto como se estableciera. Sin embargo, si la memoria caché contenía datos sucios, la memoria caché tendría que volver a escribirlos antes de poder continuar con el acceso. por lo que afirmaría SBO# al generar SDONE. Esto indicaría al objetivo activo que confirme STOP# en lugar de TRDY#, lo que provocaría que el iniciador se desconecte y vuelva a intentar la operación más tarde. Mientras tanto, el caché arbitraría el bus y volvería a escribir sus datos en la memoria.

También se requieren objetivos compatibles con la coherencia de caché para terminar las ráfagas antes de que crucen las líneas de caché.

Herramientas de desarrollo

Al desarrollar y/o solucionar problemas del bus PCI, el examen de las señales de hardware puede ser muy importante. Los analizadores lógicos y los analizadores de bus son herramientas que recopilan, analizan y decodifican señales para que los usuarios las vean de manera útil.

Contenido relacionado

Memoria de acceso aleatorio no volátil

Familia de tanques IS

Ford tauro