Intel 8080

El Intel 8080 ("ochenta y ochenta") es el segundo microprocesador de 8 bits diseñado y fabricado por Intel. Apareció por primera vez en abril de 1974 y es una variante ampliada y mejorada del diseño anterior del 8008, aunque sin compatibilidad binaria. La velocidad de reloj o límite de frecuencia especificado inicialmente era de 2 MHz, con instrucciones comunes que usaban 4, 5, 7, 10 u 11 ciclos. Como resultado, el procesador puede ejecutar varios cientos de miles de instrucciones por segundo. Dos variantes más rápidas, la 8080A-1 (a veces denominada 8080B) y la 8080A-2, estuvieron disponibles más tarde con límites de frecuencia de reloj de 3,125 MHz y 2,63 MHz, respectivamente. El 8080 necesita dos chips de soporte para funcionar en la mayoría de las aplicaciones: el controlador/generador de reloj i8224 y el controlador de bus i8228. Se implementa en la lógica de semiconductores de óxido de metal (NMOS) de tipo N utilizando transistores de modo de mejora no saturados como cargas, por lo que exige un voltaje de +12 V y −5 V además del transistor principal compatible con la lógica de transistores (TTL). +5 V.

Aunque los microprocesadores anteriores se usaban comúnmente en dispositivos producidos en masa, como calculadoras, cajas registradoras, terminales de computadora, robots industriales y otras aplicaciones, el 8080 tuvo un mayor éxito en un conjunto más amplio de aplicaciones y se le atribuye en gran medida el inicio de la industria de microcomputadoras. Varios factores contribuyeron a su popularidad: su paquete de 40 pines facilitó la interfaz que el 8008 de 18 pines y también hizo que su bus de datos fuera más eficiente; su implementación NMOS le dio transistores más rápidos que los de la lógica de semiconductor de óxido de metal (PMOS) 8008 de tipo P, al tiempo que simplificó la interfaz al hacerlo compatible con TTL; estaba disponible una variedad más amplia de chips de soporte; su conjunto de instrucciones se mejoró con respecto al 8008; y su bus de direcciones completo de 16 bits (frente al de 14 bits del 8008) le permitió acceder a 64 KB de memoria, cuatro veces más que el rango de 16 KB del 8008. Se usó en el Altair 8800 y en las computadoras personales de bus S-100 posteriores hasta que fue reemplazado por el Z80 en esta función, y fue la CPU de destino original para los sistemas operativos CP / M desarrollados por Gary Kildall.

El 8080 influyó directamente en la arquitectura x86 posterior. Intel diseñó el 8086 para que su lenguaje ensamblador fuera lo suficientemente similar al 8080, con la mayoría de las instrucciones mapeadas directamente entre sí, ese código ensamblador transpilado del 8080 podría ejecutarse en el 8086.

Historia

Los clientes de microprocesadores se mostraron reacios a adoptar el 8008 debido a limitaciones como el modo de direccionamiento único, la baja velocidad del reloj, el bajo número de pines y la pequeña pila en el chip, que restringían la escala y la complejidad del software. Hubo varios diseños propuestos para el 8080, que van desde simplemente agregar instrucciones de pila al 8008 hasta una desviación completa de todas las arquitecturas Intel anteriores. El diseño final fue un compromiso entre las propuestas.

Federico Faggin, el creador de la arquitectura 8080 a principios de 1972, propuso el chip a la gerencia de Intel e impulsó su implementación. Finalmente obtuvo el permiso para desarrollarlo seis meses después. Faggin contrató a Masatoshi Shima, quien ayudó a diseñar el 4004 con él, desde Japón en noviembre de 1972. Shima hizo el diseño detallado bajo la dirección de Faggin, utilizando la metodología de diseño para lógica aleatoria con puerta de silicio que Faggin había creado para la familia 4000..

El 8080 se diseñó explícitamente para ser un microprocesador de propósito general para una mayor cantidad de clientes. Gran parte del esfuerzo de desarrollo se dedicó a tratar de integrar las funcionalidades de los chips complementarios del 8008 en un solo paquete. Al principio del desarrollo, se decidió que el 8080 no sería compatible en binario con el 8008, sino que optaría por la compatibilidad de fuente una vez que se ejecutara a través de un transpilador, para permitir que el nuevo software no estuviera sujeto a las mismas restricciones que el 8008. Por lo mismo Por esta razón, además de expandir las capacidades de las rutinas e interrupciones basadas en pilas, la pila se movió a la memoria externa.

Teniendo en cuenta el uso especializado de los registros de uso general por parte de los programadores en los sistemas mainframe, Stanley Mazor, el arquitecto del chip, decidió que los registros del 8080 serían especializados, con pares de registros que tendrían un conjunto diferente de usos. Esto también permitió a los ingenieros usar transistores de manera más efectiva para otros fines.

Shima terminó el diseño en agosto de 1973. Después de la regulación de la fabricación de NMOS, se completó un prototipo del 8080 en enero de 1974. Tenía un defecto, ya que la conducción con dispositivos TTL estándar aumentaba el voltaje de tierra porque fluía alta corriente en la línea estrecha. Intel ya había producido 40.000 unidades del 8080 bajo la dirección de la sección de ventas antes de que Shima caracterizara el prototipo. Se lanzó para requerir dispositivos Schottky TTL (LS TTL) de bajo consumo. El 8080A solucionó este defecto.

Intel ofreció un simulador de conjunto de instrucciones para el 8080 llamado INTERP/80 para ejecutar programas PL/M compilados. Fue escrito por Gary Kildall mientras trabajaba como consultor para Intel.

Descripción

Modelo de programación

El Intel 8080 es el sucesor del 8008. Utiliza el mismo conjunto de instrucciones básico y modelo de registro que el 8008, aunque no es compatible con el código fuente ni con el código binario con su predecesor. Cada instrucción en el 8008 tiene una instrucción equivalente en el 8080. El 8080 también agrega operaciones de 16 bits en su conjunto de instrucciones. Mientras que el 8008 requería el uso del par de registros HL para acceder indirectamente a su espacio de memoria de 14 bits, el 8080 agregó modos de direccionamiento para permitir el acceso directo a su espacio de memoria completo de 16 bits. La pila de llamadas push-down interna de 7 niveles del 8008 fue reemplazada por un registro de puntero de pila (SP) de 16 bits dedicado. El paquete DIP de 40 pines del 8080 le permite proporcionar un bus de direcciones de 16 bits y un bus de datos de 8 bits, lo que permite el acceso a 64 KiB (216 bytes) de memoria.

Registros

El procesador tiene siete registros de 8 bits (A, B, C, D, E, H y L), donde A es el acumulador principal de 8 bits. Los otros seis registros se pueden usar como registros individuales de 8 bits o en tres pares de registros de 16 bits (BC, DE y HL, denominados B, D y H en los documentos de Intel) según la instrucción particular. Algunas instrucciones también permiten que el par de registros HL se use como un acumulador (limitado) de 16 bits. Un pseudo-registro M, que se refiere a la ubicación de memoria desreferenciada señalada por HL, se puede usar casi en cualquier lugar donde se puedan usar otros registros. El 8080 tiene un puntero de memoria de pila de 16 bits, que reemplaza la pila interna del 8008, y un contador de programa de 16 bits.

Banderas

El procesador mantiene bits indicadores internos (un registro de estado), que indican los resultados de las instrucciones aritméticas y lógicas. Solo ciertas instrucciones afectan a las banderas. Las banderas son:

- Firme (S), establece si el resultado es negativo.

- Cero (Z), establecido si el resultado es cero.

- Paridad (P), establece si el número de 1 bits en el resultado es incluso.

- Carry (C), establecer si la última operación de adición resultó en un porte o si la última operación de resta requiere un préstamo

- Carga auxiliar (AC o H), utilizada para aritmética decimal de código binario (BCD).

El bit de acarreo se puede configurar o complementar con instrucciones específicas. Las instrucciones de bifurcación condicional prueban los diversos bits de estado de las banderas. Las banderas se pueden copiar como un grupo al acumulador. El acumulador A y las banderas juntas se denominan registro PSW o palabra de estado del programa.

Comandos, instrucciones

Al igual que con muchos otros procesadores de 8 bits, todas las instrucciones están codificadas en un byte (incluidos los números de registro, pero excluyendo los datos inmediatos), por simplicidad. Algunos pueden ir seguidos de uno o dos bytes de datos, que pueden ser un operando inmediato, una dirección de memoria o un número de puerto. Al igual que los procesadores más avanzados, tiene instrucciones CALL y RET automáticas para llamadas y devoluciones de procedimientos de varios niveles (que incluso pueden ejecutarse condicionalmente, como saltos) e instrucciones para guardar y restaurar cualquier par de registros de 16 bits en la pila de la máquina. Ocho instrucciones de llamada de un byte (RST) para subrutinas existen en las direcciones fijas 00h, 08h, 10h,..., 38h. Estos están destinados a ser suministrados por hardware externo para invocar una rutina de servicio de interrupción correspondiente, pero también se emplean a menudo como llamadas rápidas al sistema. La instrucción que se ejecuta más lentamente es XTHL, que se utiliza para intercambiar el par de registros HL con el valor almacenado en la dirección indicada por el puntero de pila.

Instrucciones de 8 bits

Todas las operaciones de 8 bits con dos operandos solo se pueden realizar en el acumulador de 8 bits (el registro A). El otro operando puede ser un valor inmediato, otro registro de 8 bits o un byte de memoria direccionado por el par de registros de 16 bits HL. Los incrementos y decrementos se pueden realizar en cualquier registro de 8 bits o en un byte de memoria con dirección HL. Se admite la copia directa entre dos registros cualesquiera de 8 bits y entre cualquier registro de 8 bits y un byte de memoria con dirección HL. Debido a la codificación regular de la instrucción MOV (usando una cuarta parte del espacio de código de operación disponible), hay códigos redundantes para copiar un registro en sí mismo (MOV B,B, por ejemplo), que son de poca utilidad, excepto para los retrasos. Sin embargo, el código de operación sistemático para MOV M,M es en su lugar, se utiliza para codificar la instrucción detener (HLT), deteniendo la ejecución hasta que se produzca un reinicio externo o una interrupción.

Operaciones de 16 bits

Aunque el 8080 es generalmente un procesador de 8 bits, tiene capacidades limitadas para realizar operaciones de 16 bits. Cualquiera de los tres pares de registros de 16 bits (BC, DE o HL, denominados B, D, H en los documentos de Intel) o SP se puede cargar con un valor inmediato de 16 bits (usando LXI), incrementado o decrementado (usando INX y DCX), o agregado a HL (usando PAPÁ). Al agregar HL a sí mismo, es posible lograr el mismo resultado que un desplazamiento aritmético a la izquierda de 16 bits con una instrucción. Las únicas instrucciones de 16 bits que afectan a cualquier marca son DAD, que establece el indicador CY (carry) para permitir la aritmética programada de 24 o 32 bits (o mayor), necesaria para implementar la aritmética de coma flotante. Se puede asignar un marco de pila usando DAD SP y SPHL. Una bifurcación a un puntero calculado se puede ejecutar con PCHL. LHLD carga HL desde la memoria direccionada directamente y SHLD almacena HL de la misma manera. La instrucción XCHG intercambia los valores de HL y DE registrar pares. XTHLintercambia el último elemento colocado en la pila con HL.

Esquema de entrada/salida

Espacio del puerto de entrada y salida

El 8080 admite hasta 256 puertos de entrada/salida (E/S), a los que se accede a través de instrucciones de E/S dedicadas que toman direcciones de puertos como operandos. Este esquema de asignación de E/S se considera una ventaja, ya que libera el espacio de direcciones limitado del procesador. En cambio, muchas arquitecturas de CPU utilizan las denominadas E/S asignadas a la memoria (MMIO), en las que se utiliza un espacio de direcciones común para la RAM y los chips periféricos. Esto elimina la necesidad de instrucciones de E/S dedicadas, aunque un inconveniente en tales diseños puede ser que se debe usar hardware especial para insertar estados de espera, ya que los periféricos suelen ser más lentos que la memoria. Sin embargo, en algunas computadoras 8080 simples, la E/S se aborda como si fueran celdas de memoria, "asignadas en memoria", dejando los comandos de E/S sin usar. El direccionamiento de E/S a veces también puede emplear el hecho de que el procesador genera la misma dirección de puerto de 8 bits tanto para el byte de dirección inferior como para el superior (es decir, IN 05h colocaría la dirección 0505h en el bus de direcciones de 16 bits). Se utilizan esquemas de puertos de E / S similares en Zilog Z80 e Intel 8085 compatibles con versiones anteriores, y en las familias de microprocesadores x86 estrechamente relacionadas.

Espacio de pila separado

Uno de los bits en la palabra de estado del procesador (ver a continuación) indica que el procesador está accediendo a los datos de la pila. Usando esta señal, es posible implementar un espacio de memoria de pila separado. Esta función rara vez se utiliza.

La palabra de estado interno

Para sistemas más avanzados, durante una fase de su ciclo de trabajo, el procesador establece su "byte de estado interno" en el bus de datos. Este byte contiene indicadores que determinan si se accede a la memoria o al puerto de E/S y si es necesario manejar una interrupción.

El estado del sistema de interrupción (habilitado o deshabilitado) también se emite en un pin separado. Para sistemas simples, donde no se utilizan las interrupciones, es posible encontrar casos en los que este pin se utiliza como un puerto de salida de un solo bit adicional (la popular computadora Radio-86RK fabricada en la Unión Soviética, por ejemplo).

Código de ejemplo

El siguiente código fuente del ensamblador 8080/8085 es para una subrutina llamada memcpy que copia un bloque de bytes de datos de un tamaño determinado de una ubicación a otra. El bloque de datos se copia byte a byte, y el movimiento de datos y la lógica de bucle utilizan operaciones de 16 bits.

1000 1000 1000 78 1001 B1 1002 C8 1003 1A 1004 77 1005 13 1006 23 1007 0B 1008 78 1009 B1 100A C2 03 10 C9 100D | ; memcpy...; Copiar un bloque de memoria de un lugar a otro.;; Registros de entrada; BC - Número de bytes para copiar; DE - Dirección del bloque de datos de origen; HL - Dirección del bloque de datos de destino;; Registros de retorno; BC - Zero org 1000h ;Origin at 1000hmemcpy público mov a,b ;Copiar registro B para registrar A ora c ;Bitwise OR of A and C into register A rz ; Regresar si el cero-flag se pone alto.Loop: ldax d ; Carga A de la dirección señalada por el DE mov m,a ;Store A en la dirección señalada por el HL inx d ; Incremento DE inx h ; Incremento HL dcx b ;Decreto BC (no afecta a las banderas) mov a,b ;Copiar B a A (para comparar BC con cero) ora c ;A = A TENCIÓN C (son ambos B y C cero?) jnz bucle ; Jump to 'loop:' si el cero-flag no está establecido. Ret ; Retorno |

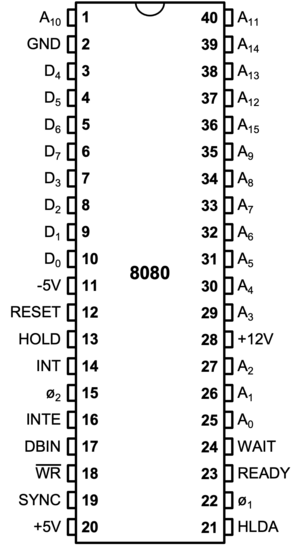

Uso de PIN

El bus de direcciones tiene sus propios 16 pines y el bus de datos tiene 8 pines que se pueden usar sin multiplexación. Usando los dos pines adicionales (señales de lectura y escritura), es posible ensamblar dispositivos de microprocesador simples muy fácilmente. Solo el espacio de E/S, las interrupciones y el DMA separados necesitan chips adicionales para decodificar las señales de los pines del procesador. Sin embargo, la capacidad de carga del pasador es limitada; incluso las computadoras simples a menudo requieren amplificadores de bus.

El procesador necesita tres fuentes de alimentación (−5, +5 y +12 V) y dos señales de sincronización de gran amplitud que no se superpongan. Sin embargo, al menos la última versión soviética КР580ВМ80А podía funcionar con una sola fuente de alimentación de +5 V, el pin de +12 V estaba conectado a +5 V y el pin de −5 V a tierra.

La tabla de pines, de la documentación que acompaña al chip, describe los pines de la siguiente manera:

| Número de pin | Signal | Tipo | Comentario |

|---|---|---|---|

| 1 | A10 | Producto | Dirección bus 10 |

| 2 | GND | — | Terreno |

| 3 | D4 | Bidirectional | Autobús de datos bidireccional. El procesador también establece de forma transitoria aquí el "estado del procesador", proporcionando información sobre lo que el procesador está haciendo actualmente:

|

| 4 | D5 | ||

| 5 | D6 | ||

| 6 | D7 | ||

| 7 | D3 | ||

| 8 | D2 | ||

| 9 | D1 | ||

| 10 | D0 | ||

| 11 | 5 - V | — | La fuente de alimentación −5 V. Esta debe ser la primera fuente de energía conectada y la última desconectada, de lo contrario el procesador será dañado. |

| 12 | RESET | Input | Reinicia. La señal obliga a ejecutar comandos ubicados en la dirección 0000. El contenido de otros registros de procesadores no se modifica. Esta es una entrada de inversión (el nivel activo es lógico 0) |

| 13 | HOLD | Input | Solicitud de acceso directo a la memoria. Se pide al procesador que cambie los datos y dirección del autobús al estado de alta impedancia ("desconectado"). |

| 14 | INT | Input | Solicitud interrumpida |

| 15 | φ2 | Input | La segunda fase de la señal del generador del reloj |

| 16 | INTE | Producto | El procesador tiene dos comandos para establecer 0 o 1 nivel en este pin. El pin normalmente se supone que se usa para el control de interrupción. Sin embargo, en computadoras simples se utilizó a veces como un solo puerto de salida de bits para varios propósitos. |

| 17 | DBIN | Producto | Lea (el procesador lee de memoria o puerto de entrada) |

| 18 | WR | Producto | Escribe (el procesador escribe al puerto de memoria o salida). Esta es una salida invertida, el nivel activo es lógico cero. |

| 19 | SYNC | Producto | El nivel activo indica que el procesador ha puesto la palabra "estado" en el autobús de datos. Los diferentes bits de esta palabra del estado proporcionan información adicional para apoyar la dirección separada y los espacios de memoria, interrumpe y acceso directo a la memoria. Esta señal es necesaria para pasar a través de la lógica adicional antes de que pueda utilizarse para escribir la palabra estado del procesador desde el bus de datos en algún registro externo, por ejemplo, Controlador de Sistema 8238 y Conductor de Autobús. |

| 20 | +5 V | — | La fuente de alimentación + 5 V |

| 21 | HLDA | Producto | Confirmación de acceso directo a la memoria. El procesador cambia los datos y los pines de dirección en el estado de alta impedancia, permitiendo que otro dispositivo manipular el autobús |

| 22 | φ1 | Input | La primera fase de la señal del generador del reloj |

| 23 | READY | Input | Espera. Con esta señal es posible suspender el trabajo del procesador. También se utiliza para apoyar el modo de depuración paso a paso basado en hardware. |

| 24 | Espera. | Producto | Espera (indica que el procesador está en el estado de espera) |

| 25 | A0 | Producto | Dirección bus |

| 26 | A1 | ||

| 27 | A2 | ||

| 28 | 12 V | — | La fuente de alimentación +12 V. Este debe ser el último conexión y primera fuente de energía desconectada. |

| 29 | A3 | Producto | El autobús de dirección; puede cambiar en estado de alta impedancia bajo demanda |

| 30 | A4 | ||

| 31 | A5 | ||

| 32 | A6 | ||

| 33 | A7 | ||

| 34 | A8 | ||

| 35 | A9 | ||

| 36 | A15 | ||

| 37 | A12 | ||

| 38 | A13 | ||

| 39 | A14 | ||

| 40 | A11 |

Fichas de soporte

Un factor clave en el éxito del 8080 fue la amplia gama de chips de soporte disponibles, que brindan comunicaciones en serie, contador/temporización, entrada/salida, acceso directo a la memoria y control de interrupción programable, entre otras funciones:

- 8238 – Controlador de sistema y conductor de autobús

- 8251 – Controlador de comunicaciones

- 8253 – Temporizador de intervalo programable

- 8255 – Interfaz periférica programable

- 8257 – Controlador DMA

- 8259 – Controlador interrumpido programable

Implementación física

El circuito integrado 8080 utiliza puertas nMOS de carga de mejora no saturada, lo que exige voltajes adicionales (para la polarización de la puerta de carga). Se fabricó en un proceso de puerta de silicio con un tamaño de característica mínimo de 6 µm. Se usa una sola capa de metal para interconectar los aproximadamente 4500 transistores en el diseño, pero la capa de polisilicio de mayor resistencia, que requiere un voltaje más alto para algunas interconexiones, se implementa con puertas de transistores. El tamaño del troquel es de aproximadamente 20 mm2.

El impacto industrial

Solicitudes y sucesores

El 8080 se usa en muchas de las primeras microcomputadoras, como MITS Altair 8800 Computer, Processor Technology SOL-20 Terminal Computer y IMSAI 8080 Microcomputer, formando la base para máquinas que ejecutan el sistema operativo CP/M (la última, casi totalmente compatible y más capaz, el procesador Zilog Z80 sacaría provecho de esto, con Z80 y CP/M convirtiéndose en la combinación dominante de CPU y sistema operativo del período entre 1976 y 1983, al igual que x86 y DOS para PC una década después).

En 1979, incluso después de la introducción de los procesadores Z80 y 8085, cinco fabricantes del 8080 vendían aproximadamente 500 000 unidades por mes a un precio de entre $3 y $4 cada una.

Las primeras microcomputadoras de placa única, como MYCRO-1 y dyna-micro / MMD-1 (ver: computadora de placa única) se basaron en Intel 8080. Una de las primeras Los usos del 8080 se hicieron a fines de la década de 1970 por Cubic-Western Data de San Diego, CA en sus sistemas automatizados de cobro de tarifas diseñados a la medida para sistemas de transporte masivo en todo el mundo. Uno de los primeros usos industriales del 8080 es como "cerebro" de la línea de productos DatagraphiX Auto-COM (Computer Output Microfiche) que toma grandes cantidades de datos de usuario de una cinta de carrete a carrete y los representa en microfichas. Los instrumentos Auto-COM también incluyen un subsistema completo automatizado de corte, procesamiento, lavado y secado de películas. Varios de los primeros videojuegos de arcade se crearon en torno al microprocesador 8080, incluido Space Invaders, uno de los juegos de arcade más populares jamás creados.

Zilog presentó el Z80, que tiene un conjunto de instrucciones de lenguaje de máquina compatible e inicialmente usó el mismo lenguaje ensamblador que el 8080, pero por razones legales, Zilog desarrolló un lenguaje ensamblador alternativo sintácticamente diferente (pero compatible con el código) para el Z80. En Intel, el 8080 fue seguido por el compatible y eléctricamente más elegante 8085.

Más tarde, Intel emitió el 8086 de 16 bits compatible con lenguaje ensamblador (pero no compatible con binario) y luego el 8088 de 8/16 bits, que fue seleccionado por IBM para su nueva PC que se lanzaría en 1981. Posteriormente NEC hizo el NEC V20 (un clon 8088 con compatibilidad con el conjunto de instrucciones Intel 80186) que también admite un modo de emulación 8080. Esto también es compatible con el V30 de NEC (un clon 8086 mejorado de manera similar). Por lo tanto, el 8080, a través de su arquitectura de conjunto de instrucciones (ISA), tuvo un impacto duradero en la historia de la informática.

En el Bloque del Este se fabricaron varios procesadores compatibles con Intel 8080A: el KR580VM80A (inicialmente marcado como KP580ИK80) en la Unión Soviética, el MCY7880 fabricado por Unitra CEMI en Polonia, el MHB8080A fabricado por TESLA en Checoslovaquia, el 8080APC fabricado por Tungsram/MEV en Hungría y el MMN8080 fabricado por Microelectronica Bucharest en Rumania.

A partir de 2017, el 8080 todavía está en producción en Lansdale Semiconductors.

- Fuentes Intel 8080

Cambio de industria

El 8080 también cambió la forma en que se crearon las computadoras. Cuando se introdujo el 8080, los sistemas informáticos solían ser creados por fabricantes de ordenadores como Digital Equipment Corporation, Hewlett Packard o IBM. Un fabricante produciría toda la computadora, incluido el procesador, las terminales y el software del sistema, como los compiladores y el sistema operativo. El 8080 fue diseñado para casi cualquier aplicación excepto un sistema informático completo. Hewlett Packard desarrolló la serie de terminales inteligentes HP 2640 en torno al 8080. El HP 2647 es un terminal que ejecuta el lenguaje de programación BASIC en el 8080. El producto fundador de Microsoft, Microsoft BASIC, se programó originalmente para el 8080.

El 8080 y el 8085 dieron origen al 8086, que fue diseñado como una extensión del 8080 compatible con el código fuente, aunque no compatible con los binarios. Este diseño, a su vez, dio lugar a la familia de chips x86, que sigue La línea principal de procesadores de Intel. Muchas de las instrucciones y conceptos básicos de la máquina del 8080 sobreviven en la plataforma x86 generalizada. Los ejemplos incluyen los registros denominados A, B, C y D y muchas de las banderas utilizadas para controlar condicional salta El código ensamblador 8080 aún se puede traducir directamente a instrucciones x86, ya que todos sus elementos centrales aún están presentes.

Impacto cultural

- Asteroid 8080 Intel es nombrado como un juego de palabras y elogio en el nombre de Intel 8080.

- El número de teléfono publicado de Microsoft, 425-882-8080, fue elegido porque mucho trabajo temprano estaba en este chip.

- Muchos de los números principales de Intel también toman una forma similar: xxx-xxx-8080

Contenido relacionado

Motor radial

Zoótropo

Boeing 727