IA-64

IA-64 (arquitectura Intel Itanium) es la arquitectura de conjunto de instrucciones (ISA) de la familia Itanium de microprocesadores Intel de 64 bits. La especificación ISA básica se originó en Hewlett-Packard (HP) y posteriormente fue implementada por Intel en colaboración con HP. El primer procesador Itanium, cuyo nombre en código es Merced, se lanzó en 2001.

La arquitectura Itanium se basa en un paralelismo explícito a nivel de instrucciones, en el que el compilador decide qué instrucciones ejecutar en paralelo. Esto contrasta con las arquitecturas superescalares, que dependen del procesador para gestionar las dependencias de las instrucciones en tiempo de ejecución. En todos los modelos de Itanium, hasta el Tukwila incluido, los núcleos ejecutan hasta seis instrucciones por ciclo de reloj.

En 2008, Itanium fue la cuarta arquitectura de microprocesador más implementada para sistemas de clase empresarial, detrás de x86-64, Power ISA y SPARC.

Historia

Desarrollo: 1989–2000

En 1989, HP comenzó a preocuparse porque las arquitecturas de cómputo de conjunto de instrucciones reducido (RISC) se acercaban a un límite de procesamiento de una instrucción por ciclo. Tanto los investigadores de Intel como los de HP habían estado explorando opciones de arquitectura informática para diseños futuros y, por separado, comenzaron a investigar un nuevo concepto conocido como palabra de instrucción muy larga (VLIW, por sus siglas en inglés) que surgió de una investigación realizada por la Universidad de Yale a principios de la década de 1980.

VLIW es un concepto de arquitectura informática (como RISC y CISC) en el que una sola palabra de instrucción contiene varias instrucciones codificadas en una palabra de instrucción muy larga para facilitar que el procesador ejecute varias instrucciones en cada ciclo de reloj. Las implementaciones típicas de VLIW dependen en gran medida de compiladores sofisticados para determinar en el momento de la compilación qué instrucciones se pueden ejecutar al mismo tiempo y la programación adecuada de estas instrucciones para la ejecución y también para ayudar a predecir la dirección de las operaciones de bifurcación. El valor de este enfoque es hacer un trabajo más útil en menos ciclos de reloj y simplificar la programación de instrucciones del procesador y los requisitos de hardware de predicción de bifurcaciones, con la penalización de una mayor complejidad, costo y consumo de energía del procesador a cambio de una ejecución más rápida.

Producción

Durante este tiempo, HP había comenzado a creer que ya no era rentable para empresas de sistemas empresariales individuales como ella misma desarrollar microprocesadores propietarios. Intel también había estado investigando varias opciones arquitectónicas para ir más allá de x86 ISA y abordar los requisitos de servidores empresariales de gama alta y computación de alto rendimiento (HPC).

Intel y HP se asociaron en 1994 para desarrollar el IA-64 ISA, utilizando una variación de los conceptos de diseño VLIW que Intel denominó explícitamente computación de instrucción paralela (EPIC). El objetivo de Intel era aprovechar la experiencia que HP había desarrollado en su trabajo VLIW inicial junto con el suyo propio para desarrollar una línea de productos de volumen dirigida a los sistemas de gama alta antes mencionados que podrían venderse a todos los fabricantes de equipos originales (OEM), mientras que HP deseaba poder comprar procesadores listos para usar creados con la fabricación en volumen de Intel y la tecnología de proceso contemporánea que eran mejores que sus procesadores PA-RISC.

Intel tomó la iniciativa en el proceso de diseño y comercialización, mientras que HP contribuye a la definición de ISA, la microarquitectura Merced/Itanium e Itanium 2. El año objetivo original para entregar el primer producto de la familia Itanium, Merced, era 1998.

Mercadotecnia

Los esfuerzos de participación de la industria y marketing de productos de Intel fueron sustanciales y lograron victorias en el diseño con la mayoría de los OEM de servidores empresariales, incluidos aquellos basados en procesadores RISC en ese momento. Compaq y Silicon Graphics decidieron abandonar un mayor desarrollo de las arquitecturas Alpha y MIPS respectivamente a favor de migrar a IA-64.

En 1997, era evidente que la arquitectura IA-64 y el compilador eran mucho más difíciles de implementar de lo que se pensaba originalmente, y la entrega de Itanium comenzó a fallar. Dado que Itanium fue el primer procesador EPIC, el esfuerzo de desarrollo encontró más problemas imprevistos de los que el equipo estaba acostumbrado. Además, el concepto EPIC depende de las capacidades del compilador que nunca antes se habían implementado, por lo que se necesitaba más investigación.

Varios grupos desarrollaron sistemas operativos para la arquitectura, incluidos Microsoft Windows, Unix y sistemas similares a Unix como Linux, HP-UX, FreeBSD, Solaris, Tru64 UNIX y Monterey/64 (los tres últimos se cancelaron antes de llegar a la mercado). En 1999, Intel lideró la formación de un consorcio industrial de código abierto para migrar Linux a IA-64 al que llamaron "Trillium" (y luego rebautizado como 'Trillian' debido a un problema de marca registrada), que fue dirigido por Intel e incluía Caldera Systems, CERN, Cygnus Solutions, Hewlett-Packard, IBM, Red Hat, SGI, SuSE, TurboLinux y VA Sistemas Linux. Como resultado, se entregó un IA-64 Linux en funcionamiento antes de lo previsto y fue el primer sistema operativo que se ejecutó en los nuevos procesadores Itanium.

Intel anunció el nombre oficial del procesador, Itanium, el 4 de octubre de 1999. En cuestión de horas, el nombre Itanic había sido acuñado en un grupo de noticias de Usenet como un juego de palabras. en el nombre Titanic, el "insumergible" trasatlántico que se hundió en su viaje inaugural en 1912.

El día siguiente, el 5 de octubre de 1999, AMD anunció sus planes para ampliar el conjunto de instrucciones x86 de Intel para incluir un modo de 64 bits totalmente compatible con versiones anteriores; además, reveló el nuevo x86 de 64 bits de AMD. arquitectura, en la que la compañía ya trabajó, para ser incorporada en el próximo microprocesador de octava generación de AMD, cuyo nombre en código es SledgeHammer. AMD también señaló una divulgación completa de las especificaciones de la arquitectura y más detalles que estarán disponibles en agosto de 2000.

Como nunca se invitó a AMD a contribuir con la arquitectura IA-64 y cualquier tipo de licencia parecía poco probable, la extensión de la arquitectura AMD64 de AMD se posicionó desde el principio como una forma evolutiva de agregar 64 bits capacidades de cómputo a la arquitectura x86 existente, sin dejar de admitir código x86 heredado de 32 bits, a diferencia del enfoque de Intel de crear una arquitectura de 64 bits completamente nueva y completamente incompatible con x86 con IA-64.

Itanio (Merced): 2001

Cuando se lanzó Itanium en junio de 2001, su rendimiento no era superior al de los procesadores RISC y CISC de la competencia.

Reconociendo que la falta de software podría ser un problema grave para el futuro, Intel puso a disposición de los proveedores de software independientes (ISV) miles de estos primeros sistemas para estimular el desarrollo. HP e Intel lanzaron al mercado el procesador Itanium 2 de próxima generación un año después.

Itanio 2: 2002–2010

El procesador Itanium 2 se lanzó en 2002. Aliviaba muchos de los problemas de rendimiento del procesador Itanium original, que en su mayoría eran causados por un subsistema de memoria ineficiente.

En 2003, AMD lanzó Opteron, que implementó su propia arquitectura de 64 bits (x86-64). Opteron obtuvo una rápida aceptación en el espacio de los servidores empresariales porque proporcionó una fácil actualización desde x86. Intel respondió implementando x86-64 (como Em64t) en sus microprocesadores Xeon en 2004.

En noviembre de 2005, los principales fabricantes de servidores Itanium se unieron a Intel y varios proveedores de software para formar Itanium Solutions Alliance para promover la arquitectura y acelerar la transferencia de software.

En 2006, Intel entregó Montecito (comercializado como la serie Itanium 2 9000), un procesador de doble núcleo que prácticamente duplicó el rendimiento y redujo el consumo de energía en aproximadamente un 20 por ciento..

Itanium 9300 (Tukwila): 2010

El procesador de la serie Itanium 9300, cuyo nombre en código es Tukwila, se lanzó el 8 de febrero de 2010 con mayor rendimiento y capacidad de memoria. Tukwila originalmente estaba programado para su lanzamiento en 2007.

El dispositivo utiliza un proceso de 65 nm, incluye de dos a cuatro núcleos, hasta 24 MB de caché en el chip, tecnología Hyper-Threading y controladores de memoria integrados. Implementa corrección de datos de dispositivo doble (DDDC), que ayuda a corregir errores de memoria. Tukwila también implementa Intel QuickPath Interconnect (QPI) para reemplazar la arquitectura basada en bus Itanium. Tiene un ancho de banda máximo entre procesadores de 96 GB/s y un ancho de banda máximo de memoria de 34 GB/s. Con QuickPath, el procesador tiene controladores de memoria integrados e interconecta la memoria directamente, utilizando interfaces QPI para conectarse directamente a otros procesadores y concentradores de E/S. QuickPath también se usa en procesadores Intel que usan la microarquitectura Nehalem, lo que hace probable que Tukwila y Nehalem puedan usar los mismos conjuntos de chips. Tukwila incorpora cuatro controladores de memoria, cada uno de los cuales admite múltiples DIMM DDR3 a través de un controlador de memoria separado, muy parecido al procesador Xeon basado en Nehalem cuyo nombre en código es Beckton.

Itanium 9500 (Poulson): 2012

El procesador de la serie Itanium 9500, cuyo nombre en código es Poulson, es el procesador sucesor de Tukwila, cuenta con ocho núcleos, tiene una arquitectura de 12 problemas, mejoras de subprocesos múltiples y nuevas instrucciones para aprovechar el paralelismo., especialmente en virtualización. El tamaño de caché de Poulson L3 es de 32 MB. El tamaño de caché L2 es de 6 MB, 512 I KB, 256 D KB por núcleo. El tamaño del troquel es de 544 mm², menos que su predecesor Tukwila (698,75 mm²).

En la ISSCC 2011, Intel presentó un documento titulado "Un procesador Itanium de 32 nm y 3100 millones de transistores de 12 problemas de ancho para servidores de misión crítica". Dado el historial de Intel de revelar detalles sobre los microprocesadores Itanium en la ISSCC, lo más probable es que este documento se refiera a Poulson. El analista David Kanter especula que Poulson utilizará una nueva microarquitectura, con una forma más avanzada de subprocesos múltiples que utiliza hasta dos subprocesos, para mejorar el rendimiento de las cargas de trabajo de un solo subproceso y subprocesos múltiples. Se dio a conocer nueva información en la conferencia de Hotchips. La nueva información presenta mejoras en subprocesos múltiples, mejoras en la resiliencia (Reproducción de instrucciones RAS) y pocas instrucciones nuevas (prioridad de subprocesos, instrucción de enteros, captura previa de caché, sugerencias de acceso a datos).

Itanium 9700 (Kittson): 2017

El Kittson es el mismo que el 9500 Poulson, pero con una frecuencia ligeramente superior.

Fin de vida útil: 2021

En enero de 2019, Intel anunció que Kittson sería descontinuado, con una fecha de último pedido de enero de 2020 y una fecha de último envío de julio de 2021.

No hay un sucesor planificado.

Arquitectura

Intel ha documentado ampliamente el conjunto de instrucciones de Itanium y la prensa técnica ha proporcionado descripciones generales. La arquitectura ha sido renombrada varias veces durante su historia. HP lo llamó originalmente PA-WideWord. Intel más tarde lo llamó IA-64, luego Arquitectura de procesador Itanium (IPA), antes de decidirse por Arquitectura Intel Itanium, pero todavía se le conoce ampliamente como IA-64.

Es una arquitectura explícitamente paralela rica en registros de 64 bits. La palabra de datos base es de 64 bits, direccionable por bytes. El espacio de direcciones lógicas es de 264 bytes. La arquitectura implementa predicación, especulación y predicción de bifurcación. Utiliza ventanas de registro de tamaño variable para el paso de parámetros. El mismo mecanismo también se utiliza para permitir la ejecución paralela de bucles. La especulación, la predicción, la predicación y el cambio de nombre están bajo el control del compilador: cada palabra de instrucción incluye bits adicionales para esto. Este enfoque es la característica distintiva de la arquitectura.

La arquitectura implementa una gran cantidad de registros:

- 128 registros generales de enteros, que son de 64 bits más una trampa ("NaT", que significa "nada") usados para la ejecución especulativa. 32 de ellos son estáticos, los otros 96 se apilan utilizando ventanas de registro de tamaño variable, o girando para bucles oleados.

gr0siempre lee 0. - 128 registros de puntos flotantes. Los registros de puntos flotantes son 82 bits de largo para preservar la precisión para los resultados intermedios. En lugar de una trampa dedicada "NaT" bit como los registros enteros, los registros de puntos flotantes tienen un valor de trampa llamado "NaTVal" ("No un valor Thing"), similar a (pero distinto de) NaN. Estos también tienen 32 registros estáticos y 96 registros ventanales o giratorios.

fr0siempre lee +0.0, yfr1siempre lee +1.0. - 64 registros predicados de un bit. Estos también tienen 32 registros estáticos y 96 registros ventanales o giratorios.

pr0siempre lee 1 (verdad). - 8 registros de rama, para las direcciones de saltos indirectos.

br0se establece en la dirección de retorno cuando una función se llama conbr.call. - 128 registros de propósito especial (o "aplicación"), que son principalmente de interés para el núcleo y no aplicaciones ordinarias. Por ejemplo, un registro llamado

bspapunta a la segunda pila, que es donde el hardware derrame automáticamente se registra cuando la ventana de registro se envuelve.

Cada palabra de instrucción de 128 bits se denomina paquete y contiene tres ranuras, cada una de las cuales contiene una instrucción de 41 bits, además de una plantilla que indica qué tipo de instrucción hay en cada ranura. Esos tipos son unidad M (instrucciones de memoria), unidad I (ALU entera, entero no ALU o instrucciones extendidas inmediatas largas), unidad F (instrucciones de coma flotante) o unidad B (instrucciones de rama o rama larga extendida). instrucciones). La plantilla también codifica paradas que indican que existe una dependencia de datos entre los datos antes y después de la parada. Todas las instrucciones entre un par de paradas constituyen un grupo de instrucciones, independientemente de su agrupación, y deben estar libres de muchos tipos de dependencias de datos; este conocimiento permite que el procesador ejecute instrucciones en paralelo sin tener que realizar su propio análisis de datos complicado, ya que ese análisis ya se realizó cuando se escribieron las instrucciones.

Dentro de cada ranura, todas las instrucciones excepto unas pocas se predican, especificando un registro de predicado, cuyo valor (verdadero o falso) determinará si la instrucción se ejecuta. Las instrucciones predicadas que siempre deben ejecutarse se predican en pr0, que siempre se lee como verdadero.

El lenguaje ensamblador IA-64 y el formato de instrucción se diseñaron deliberadamente para ser escritos principalmente por compiladores, no por humanos. Las instrucciones deben agruparse en paquetes de tres, asegurándose de que las tres instrucciones coincidan con una plantilla permitida. Las instrucciones deben emitir paradas entre ciertos tipos de dependencias de datos, y las paradas solo se pueden usar en lugares limitados de acuerdo con las plantillas permitidas.

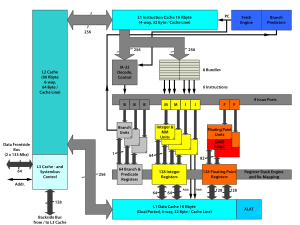

Ejecución de instrucciones

El mecanismo de obtención puede leer hasta dos paquetes por reloj desde la memoria caché L1 en la canalización. Cuando el compilador puede aprovechar esto al máximo, el procesador puede ejecutar seis instrucciones por ciclo de reloj. El procesador tiene treinta unidades de ejecución funcional en once grupos. Cada unidad puede ejecutar un subconjunto particular del conjunto de instrucciones, y cada unidad se ejecuta a una velocidad de una instrucción por ciclo a menos que la ejecución se detenga esperando datos. Si bien no todas las unidades de un grupo ejecutan subconjuntos idénticos del conjunto de instrucciones, las instrucciones comunes se pueden ejecutar en varias unidades.

Los grupos de unidades de ejecución incluyen:

- Seis ALUs para fines generales, dos unidades enteros, una unidad de cambio

- Cuatro unidades de caché de datos

- Seis unidades multimedia, dos unidades de cambio paralelos, una multiplicación paralela, una población

- Dos unidades de multiplicación de 82 bits de punto flotante, dos unidades de multiplicación de punto flotante SIMD (dos operaciones de 32 bits cada una)

- Tres unidades de rama

Idealmente, el compilador a menudo puede agrupar instrucciones en conjuntos de seis que pueden ejecutarse al mismo tiempo. Dado que las unidades de coma flotante implementan una operación de multiplicación y acumulación, una sola instrucción de coma flotante puede realizar el trabajo de dos instrucciones cuando la aplicación requiere una multiplicación seguida de una suma: esto es muy común en el procesamiento científico. Cuando ocurre, el procesador puede ejecutar cuatro FLOP por ciclo. Por ejemplo, el Itanium de 800 MHz tenía una calificación teórica de 3,2 GFLOPS y el Itanium 2 más rápido, a 1,67 GHz, tenía una calificación de 6,67 GFLOPS.

En la práctica, el procesador a menudo puede estar infrautilizado, con no todas las ranuras llenas de instrucciones útiles debido a, p. dependencias de datos o limitaciones en las plantillas de paquetes disponibles. El código más denso posible requiere 42,6 bits por instrucción, en comparación con los 32 bits por instrucción de los procesadores RISC tradicionales de la época, y las ausencias de operaciones debido a las ranuras desperdiciadas reducen aún más la densidad del código. Las instrucciones adicionales para cargas especulativas y sugerencias para ramas y caché son difíciles de generar de manera óptima, incluso con compiladores modernos.

Arquitectura de la memoria

De 2002 a 2006, los procesadores Itanium 2 compartieron una jerarquía de caché común. Tenían 16 KB de caché de instrucciones de nivel 1 y 16 KB de caché de datos de nivel 1. La caché L2 se unificó (tanto instrucciones como datos) y tiene 256 KB. La memoria caché de nivel 3 también se unificó y varió en tamaño de 1,5 MB a 24 MB. El caché L2 de 256 KB contiene suficiente lógica para manejar operaciones de semáforo sin perturbar la unidad lógica aritmética (ALU) principal.

Se accede a la memoria principal a través de un bus a un conjunto de chips fuera del chip. El autobús Itanium 2 se llamó inicialmente autobús McKinley, pero ahora se lo suele denominar autobús Itanium. La velocidad del bus ha aumentado constantemente con las nuevas versiones de procesadores. El bus transfiere 2 × 128 bits por ciclo de reloj, por lo que el bus McKinley de 200 MHz transfirió 6,4 GB/s y el bus Montecito de 533 MHz transfiere 17,056 GB/s

Cambios arquitectónicos

Los procesadores Itanium lanzados antes de 2006 tenían compatibilidad de hardware con la arquitectura IA-32 para permitir la compatibilidad con aplicaciones de servidor heredadas, pero el rendimiento del código IA-32 era mucho peor que el del código nativo y también peor que el rendimiento de los procesadores x86 contemporáneos. En 2005, Intel desarrolló IA-32 Execution Layer (IA-32 EL), un emulador de software que proporciona un mejor rendimiento. Por lo tanto, con Montecito, Intel eliminó el soporte de hardware para el código IA-32.

En 2006, con el lanzamiento de Montecito, Intel realizó una serie de mejoras en la arquitectura básica del procesador, entre ellas:

- Hardware multithreading: Cada núcleo del procesador mantiene el contexto para dos hilos de ejecución. Cuando un hilo se fija durante el acceso a la memoria, el otro hilo puede ejecutar. Intel llama a este "multreading grueso" para distinguirlo de la "técnica de lectura de Hyper" Intel integrado en algunos microprocesadores x86 y x86-64.

- Soporte de hardware para la virtualización: Intel agregó Tecnología de Virtualización Intel (Intel VT-i), que proporciona asistencias de hardware para funciones de virtualización básica. La virtualización permite que un software "hipervisor" ejecute múltiples instancias del sistema operativo en el procesador simultáneamente.

- Mejoras de caché: Montecito agregó un caché L2 dividido, que incluía un caché dedicado 1 MB L2 para instrucciones. El caché original 256 KB L2 se convirtió en un caché de datos dedicado. Montecito también incluyó hasta 12 MB de caché L3 en la dieta.

Ver Chipsets...Otros mercados.

Contenido relacionado

Motorola 6809

Flintlock

AGM-65 Inconformista