Arreglos de compuertas lógicas programables en sitio

Una matriz de compuertas programables en campo (FPGA) es un circuito integrado diseñado para ser configurado por un cliente o un diseñador después de la fabricación; de ahí el término campo -programable. La configuración de FPGA generalmente se especifica usando un lenguaje de descripción de hardware (HDL), similar al que se usa para un circuito integrado de aplicación específica (ASIC). Los diagramas de circuitos se usaban anteriormente para especificar la configuración, pero esto es cada vez más raro debido al advenimiento de las herramientas de automatización de diseño electrónico.

Los FPGA contienen una matriz de bloques lógicos programables y una jerarquía de interconexiones reconfigurables que permiten que los bloques se conecten entre sí. Los bloques lógicos se pueden configurar para realizar funciones combinacionales complejas o actuar como puertas lógicas simples como AND y XOR. En la mayoría de los FPGA, los bloques lógicos también incluyen elementos de memoria, que pueden ser simples flip-flops o bloques de memoria más completos. Muchos FPGA se pueden reprogramar para implementar diferentes funciones lógicas, lo que permite una computación reconfigurable flexible como se realiza en el software de la computadora.

Los FPGA tienen un papel notable en el desarrollo de sistemas integrados debido a su capacidad para iniciar el desarrollo de software del sistema simultáneamente con el hardware, permitir simulaciones de rendimiento del sistema en una fase muy temprana del desarrollo y permitir varias pruebas del sistema e iteraciones de diseño antes de finalizar el sistema. arquitectura.

Historia

La industria de FPGA surgió de la memoria programable de solo lectura (PROM) y los dispositivos lógicos programables (PLD). Tanto las PROM como los PLD tenían la opción de programarse en lotes en una fábrica o en el campo (programable en el campo).

Altera se fundó en 1983 y entregó el primer dispositivo lógico reprogramable de la industria en 1984, el EP300, que presentaba una ventana de cuarzo en el paquete que permitía a los usuarios hacer brillar una lámpara ultravioleta en el troquel para borrar el Celdas EPROM que contenían la configuración del dispositivo.

Xilinx produjo el primer conjunto de puertas programables en campo comercialmente viable en 1985: el XC2064. El XC2064 tenía puertas programables e interconexiones programables entre puertas, el comienzo de una nueva tecnología y mercado. El XC2064 tenía 64 bloques lógicos configurables (CLB), con dos tablas de búsqueda (LUT) de tres entradas.

En 1987, el Naval Surface Warfare Center financió un experimento propuesto por Steve Casselman para desarrollar una computadora que implementaría 600 000 puertas reprogramables. Casselman tuvo éxito y se emitió una patente relacionada con el sistema en 1992.

Altera y Xilinx continuaron sin oposición y crecieron rápidamente desde 1985 hasta mediados de la década de 1990, cuando surgieron competidores que erosionaron una parte importante de su participación en el mercado. Para 1993, Actel (ahora Microsemi) atendía alrededor del 18 por ciento del mercado.

La década de 1990 fue un período de rápido crecimiento para los FPGA, tanto en la sofisticación de los circuitos como en el volumen de producción. A principios de la década de 1990, los FPGA se usaban principalmente en telecomunicaciones y redes. A finales de la década, los FPGA se abrieron paso en aplicaciones industriales, automotrices y de consumo.

Para 2013, Altera (31 por ciento), Actel (10 por ciento) y Xilinx (36 por ciento) juntos representaban aproximadamente el 77 por ciento del mercado de FPGA.

Empresas como Microsoft han comenzado a utilizar FPGA para acelerar sistemas de computación intensivos de alto rendimiento (como los centros de datos que operan su motor de búsqueda Bing), debido a la ventaja de rendimiento por vatio que ofrecen los FPGA. Microsoft comenzó a usar FPGA para acelerar Bing en 2014, y en 2018 comenzó a implementar FPGA en otras cargas de trabajo del centro de datos para su plataforma de computación en la nube Azure.

Crecimiento

Los siguientes cronogramas indican el progreso en diferentes aspectos del diseño de FPGA.

Puertas

- 1987: 9.000 puertas, Xilinx

- 1992: 600,000, Naval Surface Warfare Department

- A principios de los años 2000: millones

- 2013: 50 millones, Xilinx

Tamaño del mercado

- 1985: Primera FPGA comercial: Xilinx XC2064

- 1987: 14 millones de dólares

- c.1993: 385 millones de dólares

- 2005: 1.900 millones de dólares

- Estimación para 2010: 2.750 millones de dólares

- 2013: 5.400 millones de dólares

- Estimación para 2020: 9.800 millones de dólares

Comienza el diseño

Un inicio de diseño es un nuevo diseño personalizado para la implementación en un FPGA.

- 2005: 80.000

- 2008: 90.000

Diseño

Los FPGA contemporáneos tienen amplias puertas lógicas y bloques de RAM para implementar cálculos digitales complejos. Los FPGA se pueden utilizar para implementar cualquier función lógica que pueda realizar un ASIC. La capacidad de actualizar la funcionalidad después del envío, la reconfiguración parcial de una parte del diseño y los bajos costos de ingeniería no recurrentes en relación con un diseño ASIC (a pesar del costo unitario generalmente más alto), ofrecen ventajas para muchas aplicaciones.

Como los diseños de FPGA emplean velocidades de E/S muy rápidas y buses de datos bidireccionales, se convierte en un desafío verificar la sincronización correcta de los datos válidos dentro del tiempo de configuración y el tiempo de espera. La planificación del suelo ayuda a la asignación de recursos dentro de los FPGA para cumplir con estas restricciones de tiempo.

Algunos FPGA tienen características analógicas además de funciones digitales. La función analógica más común es una velocidad de giro programable en cada pin de salida, lo que permite al ingeniero establecer tasas bajas en pines con poca carga que, de lo contrario, sonarían o se acoplarían de manera inaceptable, y establecer tasas más altas en canales de alta velocidad muy cargados que, de lo contrario, funcionarían. Demasiado lento. También son comunes los circuitos impulsores de osciladores de cristal de cuarzo, los osciladores de resistencia-capacitancia en el chip y los bucles de enganche de fase con osciladores controlados por voltaje incorporados que se utilizan para la generación y administración de relojes, así como para relojes de transmisión de serializador-deserializador de alta velocidad (SERDES). y recuperación del reloj del receptor. Bastante comunes son los comparadores diferenciales en pines de entrada diseñados para conectarse a canales de señalización diferencial. Algunos FPGA de señal mixta tienen convertidores periféricos de analógico a digital (ADC) y convertidores de digital a analógico (DAC) integrados con bloques de acondicionamiento de señales analógicas que les permiten operar como un sistema en un chip (SoC). Dichos dispositivos desdibujan la línea entre un FPGA, que transporta unos y ceros digitales en su estructura de interconexión programable interna, y una matriz analógica programable en campo (FPAA), que transporta valores analógicos en su estructura de interconexión programable interna.

Bloques lógicos

La arquitectura FPGA más común consta de una matriz de bloques lógicos (llamados bloques lógicos configurables, CLB o bloques de matrices lógicas, LAB, según el proveedor), pads de E/S y canales de enrutamiento. Generalmente, todos los canales de enrutamiento tienen el mismo ancho (número de cables). Múltiples pads de E/S pueden caber en la altura de una fila o el ancho de una columna en el arreglo.

"Un circuito de aplicación debe mapearse en un FPGA con los recursos adecuados. Si bien la cantidad de CLB/LAB y E/S requerida se determina fácilmente a partir del diseño, la cantidad de pistas de enrutamiento necesarias puede variar considerablemente incluso entre diseños con la misma cantidad de lógica. (Por ejemplo, un interruptor de barra transversal requiere mucho más enrutamiento que una matriz sistólica con el mismo conteo de puertas. Dado que las pistas de enrutamiento no utilizadas aumentan el costo (y disminuyen el rendimiento) de la pieza sin brindar ningún beneficio, los fabricantes de FPGA intentan proporcionar suficientes pistas de modo que se puedan enrutar la mayoría de los diseños que encajarán en términos de tablas de búsqueda (LUT) y E / S. Esto se determina mediante estimaciones como las derivadas de la regla de Rent o mediante experimentos con diseños existentes."

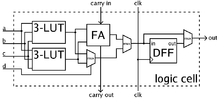

En general, un bloque lógico consta de unas pocas celdas lógicas (llamadas ALM, LE, slice, etc.). Una celda típica consta de una LUT de 4 entradas, un sumador completo (FA) y un flip-flop tipo D. Estos pueden dividirse en dos LUT de 3 entradas. En modo normal, se combinan en una LUT de 4 entradas a través del primer multiplexor (mux). En el modo aritmético, sus salidas se envían al sumador. La selección de modo está programada en el segundo mux. La salida puede ser síncrona o asíncrona, según la programación del tercer mux. En la práctica, la totalidad o partes del sumador se almacenan como funciones en las LUT para ahorrar espacio.

Bloques duros

Las familias modernas de FPGA amplían las capacidades anteriores para incluir funciones de mayor nivel fijadas en silicio. Tener estas funciones comunes incrustadas en el circuito reduce el área requerida y les da a esas funciones una mayor velocidad en comparación con construirlas a partir de primitivas lógicas. Ejemplos de estos incluyen multiplicadores, bloques DSP genéricos, procesadores integrados, lógica de E/S de alta velocidad y memorias integradas.

Los FPGA de gama alta pueden contener transceptores de varios gigabits de alta velocidad y núcleos IP duros, como núcleos de procesador, unidades de control de acceso al medio Ethernet, controladores PCI/PCI Express y controladores de memoria externos. Estos núcleos existen junto con la estructura programable, pero están construidos con transistores en lugar de LUT, por lo que tienen un rendimiento y un consumo de energía de nivel ASIC sin consumir una cantidad significativa de recursos de la estructura, dejando una mayor parte de la estructura libre para la lógica específica de la aplicación. Los transceptores de varios gigabits también contienen circuitos de entrada y salida analógica de alto rendimiento junto con serializadores y deserializadores de alta velocidad, componentes que no se pueden construir a partir de LUT. La funcionalidad de la capa física de nivel superior (PHY), como la codificación de línea, puede implementarse o no junto con los serializadores y deserializadores en lógica estricta, según la FPGA.

Núcleo blando

Un enfoque alternativo para el uso de procesadores macro duros es hacer uso de núcleos IP de procesador suave que se implementan dentro de la lógica FPGA. Nios II, MicroBlaze y Mico32 son ejemplos de procesadores softcore populares. Muchos FPGA modernos están programados en "tiempo de ejecución", lo que ha llevado a la idea de la computación reconfigurable o sistemas reconfigurables: CPU que se reconfiguran a sí mismas para adaptarse a la tarea en cuestión. Además, están comenzando a surgir nuevas arquitecturas que no son FPGA. Los microprocesadores configurables por software, como el Stretch S5000, adoptan un enfoque híbrido al proporcionar una matriz de núcleos de procesador y núcleos programables similares a FPGA en el mismo chip.

Integración

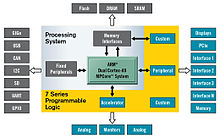

En 2012, el enfoque arquitectónico de grano grueso dio un paso más allá al combinar los bloques lógicos y las interconexiones de los FPGA tradicionales con microprocesadores integrados y periféricos relacionados para formar un "sistema completo en un chip programable". Este trabajo refleja la arquitectura creada por Ron Perloff y Hanan Potash de Burroughs Advanced Systems Group en 1982, que combinó una arquitectura de CPU reconfigurable en un solo chip llamado SB24. Se pueden encontrar ejemplos de tales tecnologías híbridas en el SoC totalmente programable Xilinx Zynq-7000, que incluye un procesador ARM Cortex-A9 MPCore de doble núcleo de 1,0 GHz integrado en la estructura lógica de la FPGA o en la FPGA Altera Arria V. que incluye un ARM Cortex-A9 MPCore de doble núcleo a 800 MHz. El Atmel FPSLIC es otro dispositivo de este tipo, que utiliza un procesador AVR en combinación con la arquitectura lógica programable de Atmel. Los dispositivos Microsemi SmartFusion incorporan un núcleo de procesador duro ARM Cortex-M3 (con hasta 512 kB de flash y 64 kB de RAM) y periféricos analógicos, como convertidores de analógico a digital multicanal y convertidores de digital a analógico para su tejido FPGA basado en memoria flash.

Reloj

La mayor parte de los circuitos integrados en una FPGA son circuitos síncronos que requieren una señal de reloj. Los FPGA contienen redes de enrutamiento regionales y globales dedicadas para el reloj y el restablecimiento, de modo que se puedan entregar con un sesgo mínimo. Además, los FPGA generalmente contienen componentes de bucle de bloqueo de fase analógico y/o bucle de bloqueo de retardo para sintetizar nuevas frecuencias de reloj y atenuar la fluctuación de fase. Los diseños complejos pueden usar múltiples relojes con diferentes relaciones de frecuencia y fase, cada uno formando dominios de reloj separados. Estas señales de reloj pueden ser generadas localmente por un oscilador o pueden recuperarse de un flujo de datos en serie de alta velocidad. Se debe tener cuidado al construir circuitos de cruce de dominio de reloj para evitar la metaestabilidad. Los FPGA generalmente contienen bloques de RAM que son capaces de funcionar como RAM de doble puerto con diferentes relojes, lo que ayuda en la construcción de FIFO y búferes de doble puerto que conectan diferentes dominios de reloj.

Arquitecturas 3D

Para reducir el tamaño y el consumo de energía de los FPGA, proveedores como Tabula y Xilinx han introducido arquitecturas 3D o apiladas. Tras la introducción de sus FPGA de la serie 7 de 28 nm, Xilinx dijo que varias de las piezas de mayor densidad en esas líneas de productos de FPGA se construirán utilizando múltiples troqueles en un solo paquete, empleando tecnología desarrollada para la construcción 3D y conjuntos de troqueles apilados.

El enfoque de Xilinx apila varios troqueles de FPGA activos (tres o cuatro) uno al lado del otro en un intercalador de silicio, una sola pieza de silicio que transporta una interconexión pasiva. La construcción de matriz múltiple también permite crear diferentes partes de la FPGA con diferentes tecnologías de proceso, ya que los requisitos del proceso son diferentes entre la propia estructura de la FPGA y los transceptores seriales de muy alta velocidad de 28 Gbit/s. Una FPGA construida de esta manera se llama FPGA heterogénea.

El enfoque heterogéneo de Altera implica el uso de un solo troquel monolítico de FPGA y la conexión de otros troqueles/tecnologías al FPGA mediante la tecnología de puente de interconexión multitroquel (EMIB) integrada de Intel.

Programación

Para definir el comportamiento de la FPGA, el usuario proporciona un diseño en un lenguaje de descripción de hardware (HDL) o como un diseño esquemático. El formulario HDL es más adecuado para trabajar con estructuras grandes porque es posible especificar un comportamiento funcional de alto nivel en lugar de dibujar cada pieza a mano. Sin embargo, la entrada esquemática puede permitir una visualización más sencilla de un diseño y sus módulos componentes.

Usando una herramienta de automatización de diseño electrónico, se genera una netlist mapeada por tecnología. Luego, la lista de conexiones se puede adaptar a la arquitectura FPGA real mediante un proceso llamado ubicación y ruta, que generalmente realiza el software de ubicación y ruta propiedad de la empresa FPGA. El usuario validará los resultados del mapa, el lugar y la ruta mediante análisis de tiempo, simulación y otras metodologías de verificación y validación. Una vez que se completa el proceso de diseño y validación, el archivo binario generado, generalmente utilizando el software propietario del proveedor de FPGA, se usa para (re)configurar el FPGA. Este archivo se transfiere al FPGA/CPLD a través de una interfaz serial (JTAG) o a un dispositivo de memoria externo como una EEPROM.

Los HDL más comunes son VHDL y Verilog, así como extensiones como SystemVerilog. Sin embargo, en un intento por reducir la complejidad del diseño en HDL, que se ha comparado con el equivalente de los lenguajes ensambladores, existen iniciativas para elevar el nivel de abstracción mediante la introducción de lenguajes alternativos. Instrumentos Nacionales' El lenguaje de programación gráfica LabVIEW (a veces denominado "G") tiene un módulo complementario FPGA disponible para apuntar y programar hardware FPGA. Verilog se creó para simplificar el proceso y hacer que HDL sea más robusto y flexible. Verilog es actualmente el más popular. Verilog crea un nivel de abstracción para ocultar los detalles de su implementación. Verilog tiene una sintaxis similar a C, a diferencia de VHDL.

Para simplificar el diseño de sistemas complejos en FPGA, existen bibliotecas de funciones y circuitos complejos predefinidos que se han probado y optimizado para acelerar el proceso de diseño. Estos circuitos predefinidos se denominan comúnmente núcleos de propiedad intelectual (IP) y están disponibles a través de proveedores de FPGA y proveedores de IP de terceros. Rara vez son gratuitos y, por lo general, se publican bajo licencias propietarias. Hay otros circuitos predefinidos disponibles en comunidades de desarrolladores como OpenCores (generalmente publicados bajo licencias gratuitas y de código abierto como GPL, BSD o licencias similares) y otras fuentes. Dichos diseños se conocen como "hardware de código abierto".

En un flujo de diseño típico, un desarrollador de aplicaciones FPGA simulará el diseño en varias etapas a lo largo del proceso de diseño. Inicialmente se simula la descripción RTL en VHDL o Verilog creando bancos de pruebas para simular el sistema y observar resultados. Luego, después de que el motor de síntesis haya asignado el diseño a una lista de conexiones, la lista de conexiones se traduce a una descripción a nivel de puerta donde se repite la simulación para confirmar que la síntesis se realizó sin errores. Finalmente, el diseño se presenta en el FPGA, momento en el que se pueden agregar retrasos de propagación y la simulación se ejecuta nuevamente con estos valores anotados en la lista de conexiones.

Más recientemente, los programadores están utilizando OpenCL (Open Computing Language) para aprovechar el rendimiento y la eficiencia energética que brindan los FPGA. OpenCL permite a los programadores desarrollar código en el lenguaje de programación C y apuntar a funciones FPGA como núcleos OpenCL utilizando construcciones OpenCL. Para obtener más información, consulte Síntesis de alto nivel y C a HDL.

La mayoría de los FPGA dependen de un enfoque basado en SRAM para programarse. Estos FPGA son programables y reprogramables en el sistema, pero requieren dispositivos de arranque externos. Por ejemplo, los dispositivos de memoria flash o EEPROM a menudo pueden cargar contenido en la SRAM interna que controla el enrutamiento y la lógica. El enfoque SRAM se basa en CMOS.

Las alternativas más raras al enfoque SRAM incluyen:

- Fuse: una vez programable. Bipolar. Obsoleto.

- Antifuso: una vez programable. CMOS. Ejemplos: Actel SX y Axcelerator families; Quicklogic Eclipse II familia.

- PROM: tecnología de memoria sólo lectura programable. Una vez programable por embalaje de plástico. Obsoleto.

- EPROM: tecnología de memoria de sólo lectura legible programable borrable. Una vez programable pero con ventana, se puede borrar con luz ultravioleta (UV). Obsoleto.

- EEPROM: la tecnología de memoria de sólo lectura legible para uso eléctrico. Puede ser borrado, incluso en paquetes de plástico. Algunos dispositivos EEPROM pero no todos pueden programarse en el sistema. CMOS.

- Flash: tecnología EPROM de fase flash. Puede ser borrado, incluso en paquetes de plástico. Algunos dispositivos flash pero no todos pueden ser programados en el sistema. Por lo general, una célula flash es más pequeña que una célula EEPROM equivalente y por lo tanto es menos costosa para la fabricación. CMOS. Ejemplo: familia Actel ProASIC.

Fabricantes

En 2016, los antiguos rivales de la industria Xilinx (ahora parte de AMD) y Altera (ahora una subsidiaria de Intel) fueron los líderes del mercado de FPGA. En ese momento, controlaban casi el 90 por ciento del mercado.

Tanto Xilinx (ahora AMD) como Altera (ahora Intel) ofrecen software patentado de automatización de diseño electrónico para Windows y Linux (ISE/Vivado y Quartus) que permite a los ingenieros diseñar, analizar, simular y sintetizar (compilar) sus diseños.

En marzo de 2010, Tabula anunció su tecnología FPGA que utiliza lógica multiplexada en el tiempo e interconexión que asegura ahorros potenciales en costos para aplicaciones de alta densidad. El 24 de marzo de 2015, Tabula cerró oficialmente.

El 1 de junio de 2015, Intel anunció que adquiriría Altera por aproximadamente 16 700 millones de dólares y completó la adquisición el 30 de diciembre de 2015.

El 27 de octubre de 2020, AMD anunció que adquiriría Xilinx y completó la adquisición valorada en unos 50.000 millones de dólares en febrero de 2022.

Otros fabricantes incluyen:

- Achronix, fabricación SRAM FPGAS basado con velocidad de tejido 1,5 GHz

- Altium, proporciona un entorno de diseño de hardware-software sistema-en-FPGA.

- Efinix ofrece pequeñas y medianas FPGAs. Combinan la lógica y las interconexiones de enrutamiento en una célula XLR configurable.

- GOWIN Semiconductors, manufacturing small and medium-sized SRAM and Flash-based FPGAs. También ofrecen reemplazos de pin-compatibles para algunos productos de Xilinx, Altera y Lattice.

- Lattice Semiconductor, que fabrica FPGA de baja potencia basada en SRAM con configuración integrada flash, instantánea y en vivo

- SiliconBlue Technologies, que proporciona FPGA de alta potencia basada en SRAM con memoria de configuración no volátil opcional integrada; adquirido por Lattice en 2011

- Microchip:

- Microsemi (previamente Actel), produciendo FPGAs antifuso, de base flash y señal mixta; adquirido por Microchip en 2018

- Atmel, segunda fuente de algunos dispositivos compatibles con Altera; también FPSLIC mencionado anteriormente; adquirido por Microchip en 2016

- QuickLogic, que fabrica Ultra Low Power Sensor Hubs, FPGA de baja densidad con potencia extremadamente baja, con puentes de visualización MIPI & entradas RGB, MIPI, RGB y salidas LVDS

Aplicaciones

Un FPGA se puede utilizar para resolver cualquier problema que sea computable. Esto se demuestra trivialmente por el hecho de que los FPGA se pueden usar para implementar un microprocesador suave, como Xilinx MicroBlaze o Altera Nios II. Su ventaja radica en que son significativamente más rápidos para algunas aplicaciones debido a su naturaleza paralela y su optimización en términos de la cantidad de puertas utilizadas para ciertos procesos.

Los FPGA originalmente comenzaron como competidores de los CPLD para implementar la lógica de pegado para las placas de circuito impreso. A medida que aumentaron su tamaño, capacidades y velocidad, los FPGA asumieron funciones adicionales hasta el punto de que algunos ahora se comercializan como sistemas completos en chips (SoC). Particularmente con la introducción de multiplicadores dedicados en las arquitecturas FPGA a fines de la década de 1990, las aplicaciones que tradicionalmente habían sido la única reserva del hardware de procesador de señal digital (DSP) comenzaron a incorporar FPGA en su lugar.

La evolución de los FPGA ha motivado un aumento en el uso de estos dispositivos, cuya arquitectura permite el desarrollo de soluciones de hardware optimizadas para tareas complejas, como la segmentación de imágenes de resonancia magnética 3D, la transformada wavelet discreta 3D, la reconstrucción de imágenes tomográficas o PET/ sistemas de resonancia magnética. Las soluciones desarrolladas pueden realizar tareas de computación intensivas con procesamiento paralelo, son dinámicamente reprogramables y tienen un bajo costo, al mismo tiempo que cumplen con los estrictos requisitos en tiempo real asociados con las imágenes médicas.

Otra tendencia en el uso de FPGA es la aceleración de hardware, en la que se puede usar la FPGA para acelerar ciertas partes de un algoritmo y compartir parte del cálculo entre la FPGA y un procesador genérico. El motor de búsqueda Bing se destaca por adoptar la aceleración FPGA para su algoritmo de búsqueda en 2014. A partir de 2018, los FPGA están experimentando un mayor uso como aceleradores de IA, incluido el denominado 'Project Catapult' de Microsoft. y para acelerar redes neuronales artificiales para aplicaciones de aprendizaje automático.

Tradicionalmente, los FPGA se han reservado para aplicaciones verticales específicas donde el volumen de producción es pequeño. Para estas aplicaciones de bajo volumen, la prima que pagan las empresas en el costo de hardware por unidad de un chip programable es más asequible que los recursos de desarrollo gastados en la creación de un ASIC. A partir de 2017, las nuevas dinámicas de costos y rendimiento han ampliado la gama de aplicaciones viables.

La empresa Gigabyte Technology creó una tarjeta i-RAM que usaba un FPGA de Xilinx, aunque un chip personalizado sería más económico si se fabricara en grandes cantidades. Se eligió el FPGA para llevarlo rápidamente al mercado y la tirada inicial fue de solo 1000 unidades, lo que hace que un FPGA sea la mejor opción. Este dispositivo permite que las personas usen la memoria RAM de la computadora como un disco duro.

Otros usos de los FPGA incluyen:

- Espacio (es decir, con endurecimiento de radiación)

- Módulos de seguridad de hardware

Seguridad

Los FPGA tienen ventajas y desventajas en comparación con los ASIC o los microprocesadores seguros en lo que respecta a la seguridad del hardware. FPGA' la flexibilidad hace que las modificaciones maliciosas durante la fabricación sean un riesgo menor. Anteriormente, para muchos FPGA, el flujo de bits de diseño estaba expuesto mientras el FPGA lo carga desde la memoria externa (normalmente en cada encendido). Todos los principales proveedores de FPGA ahora ofrecen un espectro de soluciones de seguridad a los diseñadores, como el cifrado y la autenticación de flujo de bits. Por ejemplo, Altera y Xilinx ofrecen cifrado AES (hasta 256 bits) para flujos de bits almacenados en una memoria flash externa.

Los FPGA que almacenan su configuración internamente en una memoria flash no volátil, como los dispositivos programables ProAsic 3 de Microsemi o XP2 de Lattice, no exponen el flujo de bits y no necesitan cifrado. Además, la memoria flash para una tabla de búsqueda proporciona protección contra alteraciones de un solo evento para aplicaciones espaciales. Los clientes que deseen una mayor garantía de resistencia a la manipulación pueden utilizar FPGA antifusibles de una sola escritura de proveedores como Microsemi.

Con sus FPGA y SoC Stratix 10, Altera introdujo un Administrador de dispositivos seguros y funciones físicas no clonables para brindar altos niveles de protección contra ataques físicos.

En 2012, los investigadores Sergei Skorobogatov y Christopher Woods demostraron que algunos FPGA pueden ser vulnerables a intenciones hostiles. Descubrieron que se había fabricado una vulnerabilidad de puerta trasera crítica en silicio como parte de Actel/Microsemi ProAsic 3, lo que lo hacía vulnerable en muchos niveles, como la reprogramación de criptografía y claves de acceso, el acceso al flujo de bits sin cifrar, la modificación de funciones de silicio de bajo nivel y la extracción de datos de configuración.

Tecnologías similares

Históricamente, los FPGA han sido más lentos, menos eficientes energéticamente y, en general, lograron menos funcionalidad que sus equivalentes ASIC fijos. Un estudio de 2006 mostró que los diseños implementados en FPGA necesitan en promedio 40 veces más área, consumen 12 veces más potencia dinámica y funcionan a un tercio de la velocidad de las implementaciones ASIC correspondientes. Más recientemente, los FPGA como Xilinx Virtex-7 o Altera Stratix 5 han llegado a rivalizar con las soluciones ASIC y ASSP correspondientes ("Parte estándar específica de la aplicación", como un chip de interfaz USB independiente) al proporcionar significativamente uso de energía reducido, mayor velocidad, menor costo de materiales, bienes raíces de implementación mínimos y mayores posibilidades de reconfiguración 'sobre la marcha'. Un diseño que incluía de 6 a 10 ASIC ahora se puede lograr usando solo un FPGA. Las ventajas de los FPGA incluyen la capacidad de reprogramar cuando ya están implementados (es decir, 'en el campo') para corregir errores y, a menudo, incluyen un tiempo de comercialización más corto y menores costos de ingeniería no recurrentes. Los proveedores también pueden tomar un camino intermedio a través de la creación de prototipos de FPGA: desarrollar su prototipo de hardware en FPGA, pero fabricar su versión final como un ASIC para que ya no pueda modificarse una vez que se haya comprometido el diseño. A menudo, este también es el caso con los nuevos diseños de procesadores. Algunos FPGA tienen la capacidad de reconfiguración parcial que permite reprogramar una parte del dispositivo mientras otras partes continúan funcionando.

Las principales diferencias entre los dispositivos lógicos programables complejos (CPLD) y los FPGA son arquitectónicas. Un CPLD tiene una estructura comparativamente restrictiva que consta de una o más matrices lógicas de suma de productos programables que alimentan una cantidad relativamente pequeña de registros sincronizados. Como resultado, los CPLD son menos flexibles, pero tienen la ventaja de demoras de tiempo más predecibles y una mayor relación lógica-interconexión. Las arquitecturas FPGA, por otro lado, están dominadas por la interconexión. Esto los hace mucho más flexibles (en términos de la gama de diseños que son prácticos para implementar en ellos), pero también mucho más complejos de diseñar, o al menos requieren un software de automatización de diseño electrónico (EDA) más complejo. En la práctica, la distinción entre FPGA y CPLD suele ser de tamaño, ya que los FPGA suelen ser mucho más grandes en términos de recursos que los CPLD. Por lo general, solo los FPGA contienen funciones integradas más complejas, como sumadores, multiplicadores, memoria y serializadores/deserializadores. Otra distinción común es que los CPLD contienen memoria flash integrada para almacenar su configuración, mientras que los FPGA generalmente requieren una memoria externa no volátil (pero no siempre). Cuando un diseño requiere un encendido instantáneo simple (la lógica ya está configurada en el encendido), generalmente se prefieren los CPLD. Para la mayoría de las otras aplicaciones, generalmente se prefieren los FPGA. A veces, tanto los CPLD como los FPGA se utilizan en un solo diseño de sistema. En esos diseños, los CPLD generalmente realizan funciones de lógica de unión y son responsables de "arrancar" la FPGA, además de controlar la secuencia de reinicio y arranque de la placa de circuito completa. Por lo tanto, dependiendo de la aplicación, puede ser prudente usar FPGA y CPLD en un solo diseño.

Contenido relacionado

Algoritmo de Grover

Minería subterránea de roca dura

TX-0