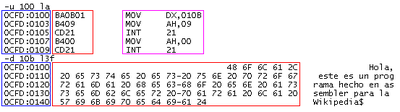

Intel 8086 and 8088

The Intel 8086 and the Intel 8088 (i8086, officially called iAPX 86, and i8088) are the first 16-bit microprocessors designed by Intel. They were the start and early members of the x86 architecture. Development work for the 8086 began in the spring of 1976 and was brought to market in the summer of 1978. The 8088 was released in 1979.

The 8086 and 8088 execute the same set of instructions. Internally they are identical, except that the 8086 has a 6-byte instruction queue and the 8088 only 4. Externally they differ in that the 8086 has a 16-bit data bus and the 8088 has only 8 bits, so, the 8086 was faster. On the other hand, the 8088 could use fewer supporting logic circuits, allowing cheaper systems to be manufactured.

The 8088 was the microprocessor used for IBM's first personal computer, the IBM PC, which was released in August 1981. Keep in mind that most of the hardware, from the early 1980s, was 8 bits, and cheaper. 16-bit hardware was almost non-existent in 1981 and very expensive.

History

Background

The 8088 was designed in Israel, at the Intel lab in Haifa, like a number of other Intel processors. In 1972, Intel released the 8008, the first 8-bit microprocessor. The 8008 implemented an instruction set designed by the Datapoint Corporation which had in mind making programmable CRT terminals. The 8008 also proved to be quite general purpose. The device required several additional ICs to produce a functional computer, in part due to its small 18-pin "memory package," which eliminated the use of a separate address bus (At the time, Intel was primarily a DRAM manufacturer).).

Two years later, in 1974, Intel released the 8080, using new 40-pin DIL packages originally developed for calculator ICs to allow for a separate address bus. It had an extended instruction set that was compatible at the source code level, not binary machine code, with the 8008 and also included some 16-bit instructions to make programming easier. The 8080 device, often described as the first truly useful microprocessor, was eventually replaced by the 8085, based on depletion-load NMOS technology (1977) that could work with a single 5V power supply instead of three different input voltages. performance of earlier chips. Other well-known 8-bit microprocessors that emerged during these years included the Motorola 6800 (1974), MOS Technology 6502 (1975), Zilog Z80 (1976), and Motorola 6809 (1978), as well as other.

The first x86 design

The 8086 project began in May 1976 and was originally intended as a temporary replacement for the ambitious and delayed iAPX 432 project. It was an attempt to steal the spotlight from the less retarded 16-bit and 32-bit processors of other manufacturers (such as Motorola, Zilog, and National Semiconductor) and at the same time counter the threat of the very successful Zilog Z80 (designed by former Intel employees). Therefore, both the architecture and the physical chip were developed rather quickly by a small group of people, and using the same basic microarchitecture elements and physical implementation techniques that were employed for the slightly older 8085 (and for which the 8086 would also work as a continuation).

Marketed as source code-level compatible, the 8086 was designed so that the assembly language for the 8008, 8080, or 8085 could be automatically converted into (suboptimal) equivalent 8086 source code, with little or no editing by hand. To make this possible, the programming model and instruction set were (loosely) based on the 8080. However, the 8086 design was expanded to support full 16-bit processing, rather than the rather basic 16-bit capabilities. bits of the 8080/8085.

New instruction classes were also added, support for signed integers, base + offset addressing, and auto-repeat operations were similar to the Z80 design, but all were made slightly more general in the 8086. Instructions supporting the nested functions of the ALGOL family of languages such as Pascal and PL/M were also added. According to principal architect Stephen P. Morse, this was a result of a more software-centric approach than the design of previous Intel processors (the designers had experience working with compiler implementations). Other improvements included microcode multiplication and division instructions and a better-adapted bus structure for future coprocessors (such as the 8087 and 8089) and multiprocessor systems.

The first revision of the instruction set and high-level architecture was ready after about three months, and since almost no CAD tools were used, four engineers and 12 layout people were simultaneously working on the chip. The 8086 took a little over two years from idea to working product, which was considered rather fast for a complex design in 1976-1978.

The 8086 was sequenced using a random mix of logic and microcode and was implemented using nMOS load depletion circuitry with approximately 20,000 active transistors (29,000 counting all ROM and PLA sites). It was soon moved to a new refined nMOS manufacturing process called HMOS (for High performance MOS) that Intel originally developed for manufacturing fast static RAM products. This was followed by versions of HMOS-II, HMOS-III, and eventually a fully static version of CMOS for battery-powered devices, manufactured using Intel's CHMOS processes. The original chip measured 33 mm² and the minimum size was 3.2 µm.

The architecture was defined by Stephen P. Morse with some help and assistance from Bruce Ravenel (the architect of the 8087) in refining the final revisions. Logic designers Jim McKevitt and John Bayliss were the lead engineers for the hardware level development team, and William Pohlma was the manager for the project. The 8086's heritage lives on in the basic instruction set of today's personal computers and servers; the 8086 also lent its last two digits to later extended versions of the design, such as the Intel 286 and Intel 386, all of which would eventually become known as the x86 family. (Another reference is that the PCI Vendor ID for Intel devices is 8086h!)

Internal structure

1 General purpose records block

2 Segment and IP Registration Block

3 Address Submer

4 Bus of internal addresses

5 Instructions (4 bytes for 8088 and 6 bytes for 8086)

6 Control unit (very simplified)

7 Bus interface

8 Internal Data Bus

9 Arithmetic logical unit (ALU)

10, 11, 12 Bus of external addresses, data and control

Bus interface unit and execution unit

The 8086 and 8088 have two internal components, the Bus Interface Unit and the Execution Unit (Bus Interface Unit (BIU) and Execution Unit (EU)).

- The Execution Unit processes the instructions of the CPU. It is made up of general records, index records and pointers, flags, arithmetic logical unity, and the control logic that handles the entire process to execute the instructions.

- The Bus Interface Unit handles reading and writing from and to memory and input/output ports. It is made up of segment logs, a 4-byte queue for instructions in 8088 and 6 in 8086, and logic to control the external buses of the microprocessor.

In the figure on the right, the Execution Unit is at the bottom and the Bus Interface Unit is at the top. The two are interconnected by an internal bus.

Logs

The i8086 and i8088 registrations were based on the design of the Intel 8080 and Intel 8085, and are actually assembly language compatible with the i8080. The register set is also similar to the i8080, but scaled up to 16 bits. Both the i8086 and i8088 have four 16-bit general purpose registers, which can also be accessed as eight 8-bit registers, and have four 16-bit index registers (including the stack pointer). Data registers are sometimes used implicitly by instructions, making it more difficult to organize registers for use with temporary values.

Processor registers are used to contain the data that is being worked on since access to registers is much faster than access to memory. You can perform arithmetic and logical operations, comparisons, among others. These operations can be done with all the registers except the segment, the IP, and the flags.

General Purpose Registers

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

The general-purpose registers are the 16-bit AX, BX, CX, and DX registers. Each one of them is divided into two 8-bit registers, called AH and AL, BH and BL, CH and CL, and, DH and DL, H meaning High (high) and L meaning Low (low), indicating the high part. or the lower part of the corresponding 16-bit register (see diagram). A program could use both 16-bit registers and 8-bit registers. Aside from the general use of registers to do arithmetic and logic calculations, there are instructions that use these registers for specialized particular use, as follows:

- Registration AX: The AX register is the accumulator, is used for operations involving entry/output, multiplication and division (the latter two together with the DX registry)

- Registration BX: The BX record is the base record, and is the only general purpose record that can be an index for indexed direction

- Registration CX: The CX registry is known as the accountant. It may contain a value to control the number of times a cycle is repeated or a bit corrigendum value

- Registration DX: The DX record is the data record. In some operations the number of input/output ports is indicated by this record, and in the multiply and division operations of 16 bits is used along with the AX accumulator

Index Records

The SI and DI registers are available for index addressing and string operations.

- Registration Yes: The 16-bit source index record is required by some operations with character strings. The SI is associated with the DS segment.

- Registration DI: The target index record is also required by some operations with character strings. The DI is associated with the ES segment.

Pointer Registers

The SP (stack pointer) and BP (base pointer) registers are associated with the SS register and allow the system to access data in the stack segment.

- SP Registry: The 16-bit stack pointer is associated with the SS segment and provides a displacement value that refers to the current word being processed in the stack. The system handles this record automatically, although the program can do certain manipulations with it.

- Register BP: The 16-bit base pointer facilitates the reference of parameters within the stack.

Flag Records

It is a 16-bit register, nine of which are used to indicate the current state of the machine and the result of processing. Many arithmetic and comparison instructions change the state of the flags and, based on them, decisions can be made to determine the subsequent action.

The table contains 16 positions (from 0 to 15), which are the 16 bits of the flag register, numbered from right to left. We will find position 0 on the right and position 15 on the left.

| - | - | - | - | OF | DF | IF | TF | SF | ZF | - | AF | - | PF | - | CF |

The flag bits are as follows:

- OF (overflow, overflow): Indicates overflow of the larger bit after an arithmetic operation of numbers with sign (1=existing overflow; 0=no overflow). For unsigned operations, this flag is not taken into account.

- DF (direction): Controls the selection of increase or decrease of the SI and DI records in the operations with character strings (1=auto decrement; 0=increment). The DF flag is controlled with STD and UNCCD instructions.

- IF (interruption): Controls the shooting of interruptions (1=habilitates interruptions; 0=disables interruptions). The unmaskable interruption is the only one that cannot be blocked by this flag. The status of the IF flag is controlled with STI and CLI instructions.

- TF (trap): Allows processor operation in depuration mode (step by step)

- SF (sign): It contains the sign resulting from an arithmetic operation (0=positive; 1=negative).

- ZF (zero): Indicates the result of an arithmetic or comparison operation (0=result different from zero; 1=result equal to zero).

- AF (supply): Contains the stroke of bit 3. This flag is tested with DAA and DAS instructions to adjust the value of AL after a sum or subtract BCD.

- PF (parity): Indicates if the number of bits 1, of the least significant byte of an operation, is pair (0=number of bits 1 is odd; 1=number of bits 1 is pair).

- CF: It contains the most orderly bit stroke after an arithmetic operation; it also stores the contents of the last bit in a displacement or rotation operation.

Segment Records

They define 64Kb areas within the 8086's 1Mb address space. These areas may partially or fully overlap. It is not possible to access a memory location not defined by some segment: if necessary, some will have to be moved.

- CS Registry: The DOS stores the initial address of the code segment of a program in the CS registry. This segment address, plus a displacement value in the instruction pointer register (IP), indicates the direction of an instruction that is sought for execution. For normal programming purposes, the CS registry is not required.

- Registration DS: The initial address of a program data segment is stored in the DS registry. This direction, plus a displacement value in an instruction, generates a reference to the location of a specific byte in the data segment.

- SS Registry: The SS registry allows the storage of a stack for temporary storage of addresses and data. The DOS stores the start address of the battery segment of a program in the SS registry. This segment address, plus a displacement value in the battery pointer log (SP), indicates the current word in the stack that is being directed. For normal programming purposes, the SS registry is not required.

- Registration ES: Some operations with character strings use the extra segment record to handle the memory direction. The ES registry is associated with the DI registry (Indice). A program that requires the use of the ES registry can initialize it with an appropriate segment address.

Instruction Pointer Register

The 16-bit IP register contains the address offset of the next instruction to be executed. The IP is associated with the CS register in the sense that the IP indicates the current instruction within the code segment that is currently executing in memory.

Memory and port access

Both microprocessors have a range of 65536 input/output addresses that can be accessed as 8-bit or 16-bit ports. In the lower part of memory there are 256 interrupt vectors.

These processors used 20 address bits that allowed them to access up to 1 MB of memory. Its internal registers were only 16 bits, so a mechanism was developed using segment registers to access the megabyte of memory. The 8086 and 8088 had four 16-bit segment registers (CS, DS, ES, and SS). Instead of supplying the missing 4 bits to address the 20 bits, like most pipelined processors, the 8086 and 8088 shift the contents of the segment register 4 bits to the left and add it to a 16-bit memory address. from index registers (BX, SI, DI, BP, SP, IP) and optionally a constant, the result being the effective address. This is often considered bad design, although it can be acceptable, and even useful, in assembly language. Conversely, it causes confusion when pointers are used extensively (as in the C language), because it is possible for two pointers with different values to point to the same memory address. This segment scheme was changed in the Intel 80286 and later in the Intel 80386.

Segmentation

There were also four 16-bit segment registers that allowed the 8086 and 8088 to access a megabyte of memory in an unusual way. Rather than concatenate the segment register with the address register, as in most processors whose address space exceeded their register size, the 8086 and 8088 shifted the 16-bit segment just four bits to the left before adding a 16-bit offset (16×segment + offset) to it, producing a 20-bit external (effective or physical) address from the 32-bit segment:offset pair. Consequently, each external address could be referred to by 212 = 4096 different segment:offset pairs. The 16-byte separation between segment bases (due to the 4-bit offset) was called a paragraph. Although it was considered complicated and cumbersome by many programmers, this scheme also had advantages; a small program (less than 64 KB) could be loaded starting at a fixed offset (such as 0) into its own segment, avoiding the need for relocation, with at most 15 bytes of alignment wasted.

Compilers for the 8086 family commonly supported two types of pointers, near and far. Near pointers were 16-bit offsets implicitly associated with the code or data segment of the program and thus could be used only within parts of a program small enough to fit in a segment. Far pointers were 32-bit segment:offset pairs that resolved to 20-bit external addresses. Some compilers also supported huge pointers, which were like far pointers except that the pointer arithmetic on a huge pointer treated it as a 20-bit linear pointer, while the pointer arithmetic on a huge pointer was wrapped. around) within its 16-bit offset without touching the segment portion of the address.

To avoid the need to specify near and far on numerous pointers, data structures, and functions, compilers also support "memory models" which specify default pointer sizes. Tiny (maximum 64K), small (maximum 128K), compact (data > 64K), medium (code > 64K), large (code and data) > 64K), and huge (individual arrays > 64K), covered the near pointer combinations. far and huge for code and data. The tiny model meant that code and data were shared in a single segment, just like most 8-bit based processors, and could be used to build file.com for example. Precompiled libraries often came in multiple versions compiled for different memory models.

According to Morse and others, the designers were actually contemplating using an 8-bit offset (instead of 4-bit), to create a 16MB physical address space. However, as this would have forced segments to start at 256-byte limits, and, around 1976, 1 MB was considered too large for a microprocessor, the idea was dropped. Also, there weren't enough pins available in a cheap 40-pin package.

In principle, the address space of the x86 series could have been extended on later processors, increasing the value of the offset, as long as applications got their segments from the operating system and made no assumptions about the equivalence of different segment:offset pairs. In practice the use of "huge" pointers and similar mechanisms was widespread and the flat 32-bit address became possible, with the 32-bit offset registers in the 80386 eventually extending the address range limit by one. more general way.

Porting old software

Small programs could ignore segmentation and just use the flat 16-bit address. This allowed 8-bit software to be ported quite easily to the 8086 and 8088. The authors of MS-DOS took advantage of this by providing an application programming interface very similar to that of CP/M as well as including the simple file format executable.com, identical to that of CP/M. This was important when the 8086/8088 and MS-DOS were new, because it allowed many existing CP/M (and other) applications to be made readily available, greatly facilitating acceptance of the new platform.

Address of the first executable statement: FFFF:0

The 8088 and 8086 processors, by hardware design, executed their first instruction at address FFFF:0 (16 bytes below the top of their 1 MB memory capacity with its 20 address bits). In this area there must be a ROM to be able to execute its instructions when turning on or restarting the computer (or device). In the case of the IBM PC, in that area was the IBM PC ROM BIOS, and the first instruction it executed was a jump (JMP) at the beginning of the Power On Self Test (POST) code, where there was code to check the CPU. and review and initialize the different hardware components and the computer's own BIOS, and at the end Boot Strap Loader was executed, which started Bootstrap. The x86 line microprocessors have inherited this memory address (FFFF: 0) for the first executable statement.

Addressing modes

The 8086 and 8088 processors had the following addressing modes:

- Implicit. The data is implied in the instruction itself. Yeah.

STC,STDandSTI(Set Carry, Set Direcction and Set Interrupts) light the corresponding flag indicated in the instruction itself.CBW(Convert Byte to Word) extends the bit of the AL sign to AX. Neither the AL nor the AX are specified, since the instructionCBWimplicitly works on them. - Immediate. The data to operate is immediately after the instruction ocode. Uh,

MOV AX, 5 - Registration. The data is in a second record. Yeah.

MOV AX, BX. Here, the data is on the BX record. - Direct. The address of the data is in the field of the direction of the opcode. Yeah.

MOV AX, [100h]. Here the content of the 100h and 101h addresses is moved to the AX registry. In this case two bytes move since AX is 16 bit. If it wereMOV BL, [100h]it would move only one byte because BL is an 8-bit register - Indirect. The data is specified by a combination of index and base records, and there may be a displacement

- Base. A base record (BX or BP) has the address where the data will be taken. Yeah.

MOV AX, [BX] - Contents. An index record (SI or DI) has the address where the data will be taken. Yeah.

MOV AX, [SI] - Base + Displacement. The data will be taken from the direction indicated by the sum of a base record plus a displacement. Yeah.

MOV AX, [BP + 7] - Contents + Displacement. The data will be taken from the direction indicated by the sum of an index record plus a displacement. Yeah.

MOV AX, [DI + 7] - Base + Index. The data will be taken from the address indicated by the sum of a base record plus an index record. Yeah.

MOV AX, [BX + SI] - Base + Index + Displacement. The data will be taken from the address indicated by the sum of a base record, plus an index record, plus a displacement. Yeah.

MOV AX, [BX + SI + 9]

- Base. A base record (BX or BP) has the address where the data will be taken. Yeah.

Sideburns

8086 and 8088 pinouts. Address bus lines are shown in red, data bus lines in blue, and control bus lines in green. The power bus lines are seen as black. These processors time multiplex the address bus with the data and control bus. In the 8086 you can see pins from 2 to 16 and pins 35 to 39 with double functionality, at a certain moment it transports the address and at another moment the data enters or leaves (or information leaves some lines of the control bus).

On the 8088, pins 9 through 16 are shared between the address and data bus, and pins 35 through 38 between the address and control bus.

8086 Pins

+- GND 1 complete. Vcc (+5V)≤2 A14 2UD A15 -- rigid D15 ≤2◊ D13 ... A13 3 short.38 A16 -- rigid S3 -- 2005≤2 A12 4Docs. A17 -- organic S4 -- 2005◊ D11 ... A11 5 short.36 A18 -- rigid S5 -- 2005◊ D10 A10 6 gap.35 A19 -- organic S6 -- 2005◊ D9 A9 7UD MINIS34 BHE/S7 -- 2005≤2 A8 8Docs. MN/!MX.◊ D7 A7 9UD Intel UD32 DRD -- rigid≤2 A6 10UD 8086 UDI31 HOLD, !RQ/!GTO ≤2≤2 A5 11UD HLDA, !RQ/!GT1 ≤2≤2 A4 12 gap.29 WR, !LOCK -- 2005≤3 A3 13IND UD28 M/!IO, !S2 -- 2005≤2 A2 14UDS DT/!R, !S1 -- 2005≤2 A1 15 short.26 DEN, !S0 -- 2005≤2 A0 16 short.25 ALE, QS0 -- HCFC -- voluntary NMI 17IND UDI24 INTA, QS1 -- 2005 -- 2005INTR 18 gap 23 ! TEST. -- CLK 19 short.22 READY. GND 20 gap RESET. +----

8088 Pins

Besides the external data bus, which is reduced to 8 bits, the difference with the 8086 is minimal.

+- GND 1 complete. Vcc (+5V) A14 2UD A15 -- rigid ... A13 3 short.38 A16 -- rigid S3 -- 2005 A12 4Docs. A17 -- organic S4 -- 2005 ... A11 5 short.36 A18 -- rigid S5 -- 2005 A10 6 gap.35 A19 -- organic S6 -- 2005 A9 7UD MINIS34 SSO!....HIGH, -- A8 8Docs. MN/!MX ... ◊ D7 A7 9UD Intel UD32 DDR! -- 2005 ≤2 A6 10UD 8088 UD31 HOLD....RQ/GTO ◊ ≤2 A5 11UD HLDA....RQ/!GT1 ◊ ≤2 A4 12 gap.29 WR....LOOK! -- 2005 ≤3 A3 13IND UD28 M/!IO...S2 -- 2005 ≤2 A2 14UDS DT/!R...S1 -- 2005 ≤2 A1 15 short.26 DEN....S0 -- 2005 ≤2 A0 16 short.25 ALE....QS0 -- 2005 -- voluntary NMI 17IND UDI24 !...QS1 -- 2005 -- 2005INTR 18 gap 23 TEST ... -- CLK 19 short.22 READY ... GND 20 gap RESET ... +----

Performance

Though overshadowed in part by other design choices on this particular chip, the multiplexed bus limited performance slightly; transfers of 16-bit or 8-bit quantities were done in memory access cycles of four clock cycles, which compared to typical contemporary 8-bit CPUs, was faster in 16-bit quantities, though slower in 16-bit quantities. 8 bit. Since the instructions ranged from one to six bytes, fetching and execution were done concurrently (as it still is on today's x86 processors): The Bus Interface Unit fed the instruction stream to the Running through a prefetch queue of 6 bytes for the 8086 and 4 bytes for the 8088 (a loosely coupled form of pipeline), speeding up operations on registers and with immediate operands, while memory operations unfortunately became more slow; four years later, this performance issue was fixed with the 80186, 80188, and 80286.

However, the 8086 and 8088 came with a full 16-bit architecture, with a full-width ALU, meaning that 16-bit arithmetic instructions could now be performed in a single ALU cycle, instead of two loops using carry used by the 8080 and 8085, speeding up such instructions considerably. It also had better performance with 16-bit logic operations. Combined with the orthogonalization of operations versus operand types and addressing modes, as well as other improvements, it made the performance gain over the 8080 or 8085 quite significant, despite the cases where older chips could be more quick.

| Instruction | Registration | Immediate registration | Registration-Memory | Memoria-Registro | Memory-Immediate |

|---|---|---|---|---|---|

| MOV | 2 | 4 | 8+EA | 9+EA | 10+EA |

| ALU | 3 | 4 | 9+EA, | 16+EA, | 17+EA |

| JMP | Registration = 11; Tag = 15; Status, Tag = 16 | ||||

| Full Multiplication | 70~160 (depending on the operation data as size) plus EA | ||||

| Full division with sign | 80~190 (depending on the operation data as size) plus EA | ||||

- EA = time to compute the effective address (Effective Address (EA)), extending from 5 to 12 cycles in 8086 and up to 19 in 8088.

- Times are the best case, depending on the status of the prefetch, the alignment of the instruction, and other factors.

As can be seen from these tables, operations on registers and immediate operands were fast (between 2 and 4 cycles), while instructions with memory operands and JMPs (jump unconditional) were quite slow; jumps took more cycles than the simple 8080 and 8085. The 8088 (used in the IBM PC) was further hampered by its narrower 8-bit data bus. The reasons why most memory-related instructions were slow were threefold:

- The weakly coupled reading and execution units are efficient for the prefetch of the instruction, but not for jumps (JMP) and random data access (without using special measures).

- A dedicated add-on was not offered for the calculation of addresses; microcode routines had to use the main ALU for this (although there was a dedicated add-on for the + offset segment).

- The address and data buses were multiplexed, forcing a slightly longer bus cycle (33~50%) than in the typical 8-bit contemporary processors.

However, memory access performance was drastically improved with Intel's next generation chips. The 80186, 80188, and 80286 had dedicated hardware for address calculation, saving many cycles, and the 80286 also additionally had separate (non-multiplexed) address and data buses.

Support Chips

The 8086/8088 use some supporting ICs made by Intel:

- Intel 8284. Watch generator

- Intel 8282. Octal Latch

- Intel 8286. Octal Bus Transceiver

- Intel 8288. Bus Controller

- Intel 8289. Bus radius

- Intel 8237. DMA Programmable Controller

- Intel 8259. Programmable Interruption Controller (PIC)

- Intel 8253. Programmable interval timer (PIT)

- Intel 8250 UART. Serial communications, RS-232

- Intel 8255. Programmable peripheral interface (PPI)

- Intel 8089. Input/output coprocessor

The functionality of most of these support chips still exists in x86 architecture computers to this day, it's just that they have long since been integrated and are no longer individual chips and are now part of the computer's chipset (the most are integrated into the south bridge).

Numeric coprocessor

The 8086/8088 did not have any floating point instructions and to perform operations on real numbers required libraries with floating point software routines. Computers with the 8086/8088 generally had a 40-pin socket into which an optional math coprocessor could be plugged in for much faster hardware/microcode based floating point capability. The Intel 8087 was the standard math coprocessor for the 8086 and 8088, operating internally on 80-bit numbers. Manufacturers such as Cyrix (8087 compatible) and Weitek (8087 non-compatible) eventually came up with a high performance floating point coprocessor that competed with the 8087, as well as the subsequent higher performance Intel 80387.

Chip versions

Originally the clock frequency was limited to 5 MHz (The IBM PC used 4.77 MHz, 4/3 of the standard NTSC colorburst frequency, but later HMOS versions were specified for 10 MHz. HMOS- III and CMOS were long manufactured (at least for a time in the 1990s) for embedded systems, although their successors, the 80186/80188 (which include some on-chip peripherals), have been more popular for embedded use..

Derivatives and clones

Compatible, and in many cases improved, versions were manufactured by Fujitsu, Harris/Intersil, OKI, Siemens AG, Texas Instruments, NEC, Mitsubishi, and AMD. For example, the NEC V20 and NEC V30 pair were hardware compatible with the 8088 and 8086 respectively, but incorporated the 80186's instruction set along with some (but not all) of the 80186's speed improvements, providing with only replace the chip, the ability to increase the instruction set and processing speed without manufacturers having to modify their designs. Such relatively simple and low power CMOS processors, compatible with the 8086/8088, are still used in embedded systems.

The electronics industry of the Soviet Union was able to replicate the 8086 with industrial espionage and reverse engineering. the resulting chip, the K1810BM86, was binary and pin-compatible with the 8086, but not mechanically compatible because it used metric measurements.

The 8088 and 8086 were the respective cores of the PC-compatible desktop computers, ES1840 and ES1841, made by the Soviets. However, these computers had significant hardware differences from their true prototypes, and the data/address bus circuitry was designed independently of Intel products.[citation needed] The ES1841 was the first PC to support dynamic bus size (US Patent #4,831,514). Subsequently, some of the principles of the ES1841 were adopted in the PS/2 (US Patent No. 5,548,786) and some other machines (British Patent Application, Publication No. GB-A-2211325, published June 28, 1989).

Microcomputers that used the i8086 or i8088

IBM PC and XT

The original IBM PC was the most influential microcomputer to use the 8088. It used a clock rate of 4.77 MHz (4/3 the colorburst rate of NTSC). Some of IBM's engineers and other employees wanted to use the IBM 801 processor, some would have preferred the new Motorola 68000, while others argued for a small and simple microprocessor similar to what had been used in earlier personal computers (such as the TRS -80 or the Apple II). However, IBM already had a history of using Intel chips in its products and had also acquired the rights to manufacture the 8086 family. Another factor was that the 8088 allowed the computer to be based on a modified 8085 design, as it could easily interface with most nMOS chips with 8-bit data buses, ie existing and mature components, and therefore inexpensive. This included ICs originally intended for support and peripheral functions around the 8085 and similar processors (not exclusively from Intel) that were already well known to many engineers, further reducing costs.

The immediate successor to the IBM PC, the IBM XT, used the 8088. It was very similar in architecture to the PC, only adding three expansion slots to the PC's five, a hard drive, additional RAM on the motherboard, and a higher capacity power source; and eliminating the interface for cassette.

Descendants of the 8088 include the 80188, 80186, 80286, 80386, 80486, Pentium, and later software-compatible processors, which are in use today.

Clones

Most clones of the IBM PC and XT used the Intel 8088 running at 4.77 or higher MHz. Some even ran at 8, 10, and even 12 MHz.

Others

Of the microcomputers that used the 8086 we have the following:

- The first commercial microcomputer based on 8086 was Mycron 2000.

- The IBM Displaywriter text processor.[chuckles]required]

- The Wang Professional Computer, manufactured by Wang Laboratories

- The AT fakeT 6300 PC (built by Olivetti)

- The NEC PC-9801 (built by NEC)

- The first Compaq Deskpro used an 8086 running at 7.14 MHz, but was able to run expansion cards designated for the IBM XT of 4.77 MHz

- The FLT86 is a well-established training system for the CPU 8086, which is still being manufactured by Flite Electronics International Limited Southampton, England.

- The IBM PS/2 models 25 and 30 were built with an 8086 of 8 MHz

- The SL series of the Tandy 1000

- Amstrad PC1512, PC1640, PC2086, PC3086 and PC5086 used 8086 to 8 MHz.

- Until 2002, NASA was still using the original 8086 CPU as ground maintenance equipment of the Discovery Space Shuttle, to prevent the regression of software that could result from updating or changing to imperfect clones.

Contenido relacionado

Sōkaku Takeda

Rhine league

Haitian Revolution