Complementary metal oxide semiconductor

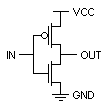

The complementary metal oxide semiconductor or complementary metal-oxide-semiconductor (CMOS) is one of the logic families used in manufacturing of integrated circuits. Its main characteristic consists of the joint use of transistors of the pMOS type and the nMOS type configured in such a way that, in the rest state, the energy consumption is only that due to parasitic currents, placed on the motherboard.

Most integrated circuits manufactured today use CMOS technology. This includes microprocessors, memories, digital signal processors, and many other types of substantially low power digital integrated circuits.

Drain (D) connected to ground (Vss), with value 0; the value 0 is not propagated to the source (S) and therefore to the output of the logic gate. The pMOS transistor, on the contrary, is in conduction state and is the one that propagates value 1 (Vdd) to the output.

Another important characteristic of CMOS circuits is that they are “regenerative”: a degraded signal driving a CMOS logic gate will be restored to its initial logic 0 or 1 value, as long as it is still within the noise margins that the CMOS logic gate allows. circuit can tolerate.

History

CMOS technology was developed by Wanlass and Sah, of Fairchild Semiconductor, in the early 1960s. However, its commercial introduction is due to RCA, with its famous CD4000 logic family.

Subsequently, the introduction of a buffer and improvements in the local oxidation process led to the introduction of the 4000B series, highly successful due to its low consumption (practically zero, in static conditions) and large power margin (of 3 to 18V).

RCA also manufactured LSIs in this technology, such as its COSMAC family, widely accepted in certain sectors, despite being an expensive product, due to the greater manufacturing difficulty compared to NMOS devices.

But its Achilles heel was its slow speed. When the clock frequency is increased, its consumption increases proportionally, becoming greater than that of other technologies. This is due to two factors:

- MOS capacity, intrinsic to MOS transistors.

- The use of P channel MOS, slower than N channel MOS, because it is the mobility of the gaps less than that of the electrons.

The other negative factor was the complexity involved in manufacturing the two types of transistors, which forced the use of a greater number of masks.

For these reasons, at the beginning of the 80s, some authors predicted the end of CMOS technology, which would be replaced by the new I2L technology, then promising.

This was the situation for a decade, but in the 1980s the scenario changed rapidly:

- On the one hand, improvements in materials, lithography and manufacturing techniques, allowed to reduce the size of the transistors, thus increasing MOS capacity.

- On the other hand, the integration of increasingly complex devices forced the introduction of a greater number of masks to ensure the isolation between transistors, so it was no more difficult to make CMOS than NMOS.

At this moment an explosion of CMOS memories began, whistles from 256x4 bits of the 5101 to 2kx8 of the 6116 and 8Kx8 in the 6264, exceeding, both in capacity and reduced consumption and speed, their NMOS counterparts. Also microprocessors, NMOS to date, began to appear in CMOS versions (80C85, 80C88, 65C02, etc.).

And new logic families appeared, HC and HCT in direct competition with TTL-LS, the dominator of the digital sector up to now.

To understand the speed of these new CMOS, one must consider the architecture of the NMOS circuits:

- Use of active loads. This is, a transistor is polarized with other transistors and not with resistance due to the smaller size of those. In addition, the MOS transistor works easily as a constant current source. Then an investor connects the inverter transistor to the active load. When the transistor is saturated, drain the entire current of the load and the level gives low output. When cut, the active load injects current until the output level rises. And here is the commitment: a small current is desirable because it reduces the need for surface in the silicon (small transistors) and dissipation (small consumption). But the low-level transitions at the high level are carried out because the active load carries the MOS capacity of the following transistor, in addition to the existing parasitic capabilities, so a high current is better, as the capabilities are rapidly loaded.

- Dynamic storage structures. The MOS capacity itself can be used to retain information for short periods of time. This means saves transistors in front of the static biset. Since MOS capacity is relatively small, in this application large transistors and reduced currents must be used, leading to a slow device.

CMOS technology improves these two factors:

- Remove the active load. The complementary structure makes it only consumed in the transitions, so that the P channel transistor can provide the necessary current to quickly load the parasitic capabilities, with a smaller N channel transistor, so that the cell is smaller than its counterpart in NMOS.

- In CMOS the dynamic registers are usually replaced by statics, because so you can lower the clock to zero and the reduced dimensions and low consumption of the CMOS cell no longer make dynamic records so attractive.

Lastly, small transistors are usually used, putting a larger cell for the interface with the pins, since the current needs are much higher in the output lines of the chip.

Decreasing the size of transistors and other improvements led to new CMOS families: AC, ACT, ACQ, etc.

Analog CMOS

MOS transistors are also employed in analog circuits, due to two important features, viz.

High input impedance

The gate of a MOS transistor is a small capacitor, so there is no bias current. For a transistor to work, it needs bias voltage.

Low channel resistance

A saturated MOS behaves like a resistor whose value depends on the area of the transistor. That is to say, that if reduced currents are requested, the voltage drop in the transistor becomes very small.

These characteristics make it possible to manufacture "Rail-to-Rail" operational amplifiers, in which the output voltage range extends from the negative to the positive supply. It is also useful in the design of linear voltage regulators and switching sources.

CMOS and bipolar

Bipolar and CMOS mixed circuits are used in both analog and digital circuits, in an attempt to take advantage of the best of both technologies. In the analog field, BiCMOS technology stands out, which allows maintaining the speed and precision of bipolar circuits, but with high input impedance and CMOS voltage ranges. As for digital families, the idea is to cut the current lines between power and ground of a bipolar circuit, placing MOS transistors. This is because a bipolar transistor is controlled by current, while a MOS transistor is controlled by voltage.

The relevance of these drawbacks is very low in current microelectronic design.

Advantages and disadvantages of CMOS

- Advantages

The logic family has a number of advantages that make it superior to others in the fabrication of digital integrated circuits:

- The low consumption of static power, thanks to the high impedance of entry of MOSFET-type transistors and to the fact that, at rest, a CMOS circuit will only experience parasitic currents. This is because in neither of the two logical states there is a direct path between the power supply and the terminal of land, or what is the same, one of the two transistors that form the basic CMOS investor is in the region of cutting in stationary state.

- Thanks to its regenerative character, the CMOS circuits are robust against noise or signal degradation due to the impedance of interconnection metal.

- CMOS circuits are simple to design.

- Manufacturing technology is very developed, and it is possible to achieve very high integration densities at a much lower price than other technologies.

- Inconvenient

Some of the drawbacks are:

- Due to the capacitive character of MOSFET transistors, and the fact that these are used by duplicate in nMOS-pMOS couples, the speed of the CMOS circuits is comparatively lower than that of other logical families.

- They are vulnerable to latch-up: It consists of the existence of a parasite thristorist in the CMOS structure that enters driving when the output exceeds the feeding. This occurs relatively easily due to the inductive component of the integrated circuit feeding network. The latch-up produces a path of low resistance to the power current that causes the destruction of the device. Following the appropriate design techniques this risk is practically zero. It is usually enough to space substrate contacts and diffusion wells with sufficient regularity, to ensure that it is solidly connected to mass or feeding.

- As the size of the transistors is reduced, the parasitic currents begin to be comparable to dynamic currents (due to the switching of the devices).

Problems

There are three main problems related to CMOS technology, although they are not unique to it.

Sensitivity to static charges

Historically, this problem has been solved by protections on the inputs of the circuit. They can be reverse diodes connected to ground and to power, which, in addition to protecting the device, reduce transients or zeners connected to ground. This latter method allows you to remove power from a single device.

Latch up

It consists of the existence of a parasitic thyristor in the cmos structure that is triggered when the output exceeds the power supply. This occurs relatively easily when there are transients due to using long badly adapted lines, excessive impedance in the power supply, or poorly decoupled power supply. The Latch-Up produces a path of low resistance to the supply current, so that, if it has not been foreseen, it leads to the destruction of the device. The latest technologies are advertised as being immune to latch-up.

Radiation resistance

The behavior of the MOS structure is extremely sensitive to the existence of charges trapped in the oxide. An alpha or beta particle passing through a CMOS chip can leave charges behind, changing the threshold voltage of the transistors and damaging or disabling the device. That is why there are "hardened" (Hardened), usually made of silicon on insulator (SOI).

Contenido relacionado

Catapult

Special phone numbers

File manager