Família de arquitetura ARM

ARM (estilizado em letras minúsculas como arm, anteriormente um acrônimo para Advanced RISC Machines e originalmente Acorn RISC Machine) é uma família de arquiteturas de conjunto de instruções (ISAs) RISC para processadores de computador. A Arm Ltd. desenvolve os ISAs e os licencia para outras empresas, que constroem os dispositivos físicos que usam o conjunto de instruções. Também projeta e licencia núcleos que implementam essas ISAs.

Devido ao seu baixo custo, baixo consumo de energia e baixa geração de calor, os processadores ARM são úteis para dispositivos leves, portáteis e alimentados por bateria, incluindo smartphones, laptops e tablets, bem como sistemas embarcados. No entanto, os processadores ARM também são usados para desktops e servidores, incluindo o supercomputador mais rápido do mundo (Fugaku) de 2020 a 2022. Com mais de 230 bilhões de chips ARM produzidos, em 2022, ARM é a família de instruções mais amplamente usada. definir arquiteturas.

Houve várias gerações de design ARM. O ARM1 original usava uma estrutura interna de 32 bits, mas tinha um espaço de endereço de 26 bits que o limitava a 64 MB de memória principal. Essa limitação foi removida na série ARMv3, que possui um espaço de endereço de 32 bits, e várias gerações adicionais até ARMv7 permaneceram em 32 bits. Lançada em 2011, a arquitetura ARMv8-A adicionou suporte para um espaço de endereço de 64 bits e aritmética de 64 bits com seu novo conjunto de instruções de comprimento fixo de 32 bits. Arm Ltd. também lançou uma série de conjuntos de instruções adicionais para regras diferentes; o "polegar" extensão adiciona instruções de 32 e 16 bits para melhorar a densidade do código, enquanto Jazelle adicionou instruções para manipular diretamente o bytecode Java. Mudanças mais recentes incluem a adição de multithreading simultâneo (SMT) para melhor desempenho ou tolerância a falhas.

Histórico

BBCMicro

Computadores Acorn' O primeiro projeto de grande sucesso foi o BBC Micro, lançado em dezembro de 1981. Esta era uma máquina relativamente convencional baseada na CPU MOS Technology 6502, mas funcionava com aproximadamente o dobro do desempenho de projetos concorrentes como o Apple II devido ao uso de dados aleatórios dinâmicos mais rápidos. memória de acesso (DRAM). A DRAM típica da época funcionava a cerca de 2 MHz; A Acorn fechou um acordo com a Hitachi para o fornecimento de peças mais rápidas de 4 MHz.

As máquinas da época geralmente compartilhavam memória entre o processador e o framebuffer, o que permitia ao processador atualizar rapidamente o conteúdo da tela sem ter que realizar entradas/saídas (E/S) separadas. Como o tempo de exibição do vídeo é exigente, o hardware de vídeo precisava ter acesso prioritário a essa memória. Devido a uma peculiaridade no design do 6502, a CPU deixou a memória intacta durante metade do tempo. Assim, ao executar a CPU a 1 MHz, o sistema de vídeo poderia ler dados durante esses tempos de inatividade, ocupando a largura de banda total de 2 MHz da RAM. No BBC Micro, o uso de RAM de 4 MHz permitiu a utilização da mesma técnica, mas rodando com o dobro da velocidade. Isso permitiu superar qualquer máquina semelhante no mercado.

Computador Empresarial Acorn

1981 também foi o ano em que o computador pessoal IBM foi lançado. Usando o recentemente lançado Intel 8088, uma CPU de 16 bits em comparação com o design de 8 bits do 6502, ele ofereceu maior desempenho geral. Sua introdução mudou radicalmente o mercado de computadores desktop: o que tinha sido em grande parte um hobby e um mercado de jogos emergente nos cinco anos anteriores começou a se transformar em uma ferramenta de negócios obrigatória, onde os designs anteriores de 8 bits simplesmente não conseguiam competir. Mesmo designs mais recentes de 32 bits também estavam chegando ao mercado, como o Motorola 68000 e o National Semiconductor NS32016.

A Acorn começou a considerar como competir neste mercado e produziu um novo design de papel denominado Acorn Business Computer. Eles se propuseram a produzir uma máquina com desempenho dez vezes maior que o BBC Micro, mas pelo mesmo preço. Isso superaria e reduziria o preço do PC. Ao mesmo tempo, a recente introdução do Apple Lisa trouxe o conceito de interface gráfica do usuário (GUI) para um público mais amplo e sugeriu que o futuro pertencia às máquinas com GUI. O Lisa, porém, custava US$ 9.995, pois vinha com chips de suporte, grandes quantidades de memória e uma unidade de disco rígido, todos muito caros na época.

Os engenheiros começaram então a estudar todos os designs de CPU disponíveis. A conclusão deles sobre os designs de 16 bits existentes foi que eles eram muito mais caros e ainda “um pouco ruins”, oferecendo desempenho apenas um pouco superior ao design BBC Micro. Eles também quase sempre exigiam um grande número de chips de suporte para operar mesmo nesse nível, o que aumentava o custo do computador como um todo. Esses sistemas simplesmente não atingiriam o objetivo do projeto. Eles também consideraram os novos designs de 32 bits, mas custavam ainda mais e apresentavam os mesmos problemas com chips de suporte. De acordo com Sophie Wilson, todos os processadores testados naquela época tiveram desempenho quase igual, com largura de banda de cerca de 4 Mbit/segundo.

Dois eventos importantes levaram a Acorn no caminho para o ARM. Um deles foi a publicação de uma série de relatórios da Universidade da Califórnia, em Berkeley, que sugeriam que um design simples de chip poderia, no entanto, ter um desempenho extremamente alto, muito superior aos designs de 32 bits mais recentes do mercado. A segunda foi uma visita de Steve Furber e Sophie Wilson ao Western Design Center, empresa dirigida por Bill Mensch e sua irmã, que se tornou a sucessora lógica da equipe MOS e oferecia novas versões como o WDC 65C02. A equipe da Acorn viu estudantes do ensino médio produzindo layouts de chips em máquinas Apple II, o que sugeria que qualquer um poderia fazer isso. Em contraste, uma visita a outra empresa de design que trabalha em CPUs modernas de 32 bits revelou uma equipe com mais de uma dúzia de membros que já estava na revisão H de seu design e ainda assim continha bugs. Isso consolidou a decisão do final de 1983 de iniciar seu próprio projeto de CPU, a Acorn RISC Machine.

Conceitos de design

Os projetos originais do Berkeley RISC eram, em certo sentido, sistemas de ensino, não projetados especificamente para desempenho total. Aos conceitos básicos de registro pesado e carregamento/armazenamento do RISC, a ARM adicionou uma série de notas de design bem recebidas do 6502. A principal delas era a capacidade de atender interrupções rapidamente, o que permitiu que as máquinas oferecessem taxas razoáveis. desempenho de entrada/saída sem hardware externo adicionado. Para oferecer interrupções com desempenho semelhante ao 6502, o design do ARM limitou seu espaço de endereço físico a 64 MB de espaço endereçável total, exigindo 26 bits de endereço. Como as instruções tinham 4 bytes (32 bits) de comprimento e precisavam ser alinhadas em limites de 4 bytes, os 2 bits inferiores de um endereço de instrução eram sempre zero. Isso significava que o contador de programa (PC) precisava ter apenas 24 bits, permitindo que fosse armazenado junto com os sinalizadores do processador de oito bits em um único registro de 32 bits. Isso significava que, ao receber uma interrupção, todo o estado da máquina poderia ser salvo em uma única operação, ao passo que se o PC tivesse um valor completo de 32 bits, seriam necessárias operações separadas para armazenar o PC e os sinalizadores de status. Esta decisão reduziu pela metade a sobrecarga de interrupção.

Outra mudança, e uma das mais importantes em termos de desempenho prático no mundo real, foi a modificação do conjunto de instruções para aproveitar as vantagens da DRAM do modo de página. Introduzido recentemente, o modo de página permitiu que acessos subsequentes à memória fossem executados duas vezes mais rápido se estivessem aproximadamente no mesmo local, ou “página”, no chip DRAM. O design de Berkeley não considerou o modo página e tratou toda a memória igualmente. O design do ARM adicionou instruções especiais de acesso à memória semelhantes a vetores, os 'ciclos S', que poderiam ser usadas para preencher ou salvar vários registros em uma única página usando o modo de página. Isso dobrou o desempenho da memória quando podiam ser usados e foi especialmente importante para o desempenho gráfico.

Os projetos Berkeley RISC usaram janelas de registro para reduzir o número de salvamentos e restaurações de registro realizadas em chamadas de procedimento; o design do ARM não adotou isso.

Wilson desenvolveu o conjunto de instruções, escrevendo uma simulação do processador em BBC BASIC que rodava em um BBC Micro com um segundo processador 6502. Isso convenceu os engenheiros da Acorn de que estavam no caminho certo. Wilson abordou o CEO da Acorn, Hermann Hauser, e solicitou mais recursos. Hauser deu sua aprovação e reuniu uma pequena equipe para projetar o processador real baseado no ISA de Wilson. O projeto oficial da Acorn RISC Machine começou em outubro de 1983.

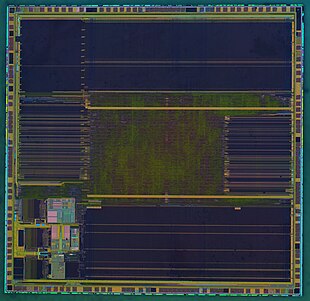

ARM1

A Acorn escolheu a VLSI Technology como "parceira de silício", pois ela era uma fonte de ROMs e chips personalizados para a Acorn. Acorn forneceu o design e a VLSI forneceu o layout e a produção. As primeiras amostras de silício ARM funcionaram corretamente quando recebidas e testadas pela primeira vez em 26 de abril de 1985. Conhecidas como ARM1, essas versões funcionavam a 6 MHz.

A primeira aplicação ARM foi como segundo processador para a BBC Micro, onde auxiliou no desenvolvimento de software de simulação para finalizar o desenvolvimento dos chips de suporte (VIDC, IOC, MEMC), e acelerou o software CAD utilizado no desenvolvimento ARM2. Posteriormente, Wilson reescreveu o BBC BASIC em linguagem assembly ARM. O conhecimento profundo obtido ao projetar o conjunto de instruções permitiu que o código fosse muito denso, tornando o ARM BBC BASIC um teste extremamente bom para qualquer emulador ARM.

ARM2

O resultado das simulações nas placas ARM1 levou à introdução, no final de 1986, do projeto ARM2 rodando a 8 MHz, e à versão com aumento de velocidade no início de 1987, de 10 a 12 MHz. Uma mudança significativa na arquitetura subjacente foi a adição de um multiplicador Booth, enquanto anteriormente a multiplicação tinha que ser realizada em software. Além disso, um novo modo de solicitação de interrupção rápida, abreviadamente FIQ, permitiu que os registros 8 a 14 fossem substituídos como parte da própria interrupção. Isso significava que as solicitações FIQ não precisavam salvar seus registros, acelerando ainda mais as interrupções.

De acordo com o benchmark Dhrystone, o ARM2 teve aproximadamente sete vezes o desempenho de um sistema típico baseado em 7 MHz 68000, como o Amiga ou o Macintosh SE. Ele era duas vezes mais rápido que um Intel 80386 rodando a 16 MHz e tinha aproximadamente a mesma velocidade de um superminicomputador multiprocessador VAX-11/784. Os únicos sistemas que o venceram foram as estações de trabalho baseadas em RISC Sun SPARC e MIPS R2000. Além disso, como a CPU foi projetada para E/S de alta velocidade, ela dispensou muitos dos chips de suporte vistos nessas máquinas; notavelmente, faltava qualquer controlador dedicado de acesso direto à memória (DMA), que era frequentemente encontrado em estações de trabalho. O sistema gráfico também foi simplificado com base no mesmo conjunto de suposições subjacentes sobre memória e tempo. O resultado foi um design dramaticamente simplificado, oferecendo desempenho equivalente ao de estações de trabalho caras, mas a um preço semelhante ao dos desktops contemporâneos.

O ARM2 apresentava um barramento de dados de 32 bits, espaço de endereço de 26 bits e 27 registros de 32 bits, dos quais 16 são acessíveis a qualquer momento (incluindo o PC). O ARM2 tinha uma contagem de transistores de apenas 30.000, em comparação com o modelo 68.000 da Motorola, seis anos mais antigo, com cerca de 68.000. Grande parte dessa simplicidade veio da falta de microcódigo, que representa cerca de um quarto a um terço dos transistores do 68000, e da falta de (como a maioria das CPUs da época) um cache. Essa simplicidade permitiu que o ARM2 tivesse baixo consumo de energia e empacotamento térmico mais simples, por ter menos transistores alimentados, mas oferecendo melhor desempenho do que o contemporâneo IBM PS/2 Modelo 50 de 1987, que inicialmente utilizava um Intel 80286, oferecendo 1,8 MIPS @ 10 MHz, e mais tarde em 1987, os 2 MIPS do PS/2 70, com seu Intel 386 DX @ 16 MHz.

Um sucessor, ARM3, foi produzido com cache de 4 KB, o que melhorou ainda mais o desempenho. O barramento de endereços foi estendido para 32 bits no ARM6, mas o código do programa ainda precisava estar dentro dos primeiros 64 MB de memória no modo de compatibilidade de 26 bits, devido aos bits reservados para os sinalizadores de status.

Advanced RISC Machines Ltd. – ARM6

No final da década de 1980, a Apple Computer e a VLSI Technology começaram a trabalhar com a Acorn em versões mais recentes do núcleo ARM. Em 1990, a Acorn separou a equipe de design em uma nova empresa chamada Advanced RISC Machines Ltd., que se tornou ARM Ltd. quando sua empresa-mãe, Arm Holdings plc, entrou na bolsa de valores de Londres e na Nasdaq em 1998. A nova Apple – ARM o trabalho eventualmente evoluiria para o ARM6, lançado pela primeira vez no início de 1992. A Apple usou o ARM610 baseado em ARM6 como base para seu PDA Apple Newton.

Licenciados iniciais

Em 1994, a Acorn usou o ARM610 como a principal unidade central de processamento (CPU) em seus computadores RiscPC. A DEC licenciou a arquitetura ARMv4 e produziu o StrongARM. A 233 MHz, esta CPU consumiu apenas um watt (as versões mais recentes consomem muito menos). Este trabalho foi posteriormente repassado à Intel como parte de um acordo judicial, e a Intel aproveitou a oportunidade para complementar sua linha i960 com o StrongARM. Posteriormente, a Intel desenvolveu sua própria implementação de alto desempenho chamada XScale, que desde então foi vendida para a Marvell. A contagem de transistores do núcleo ARM permaneceu essencialmente a mesma durante essas mudanças; O ARM2 tinha 30.000 transistores, enquanto o ARM6 cresceu apenas para 35.000.

Participação de mercado

Em 2005, cerca de 98% de todos os telemóveis vendidos utilizavam pelo menos um processador ARM. Em 2010, os produtores de chips baseados em arquiteturas ARM relataram remessas de 6,1 bilhões de processadores baseados em ARM, representando 95% dos smartphones, 35% das televisões digitais e decodificadores e 10% dos computadores móveis. Em 2011, a arquitetura ARM de 32 bits foi a arquitetura mais utilizada em dispositivos móveis e a de 32 bits mais popular em sistemas embarcados. Em 2013, foram produzidos 10 mil milhões e “os chips baseados em ARM são encontrados em quase 60% dos dispositivos móveis do mundo”.

Licenciamento

Licença principal

O principal negócio da Arm Ltd. é a venda de núcleos IP, que os licenciados usam para criar microcontroladores (MCUs), CPUs e sistemas em chips baseados nesses núcleos. O fabricante do projeto original combina o núcleo ARM com outras peças para produzir um dispositivo completo, normalmente um que pode ser construído em fábricas (fábricas) de fabricação de semicondutores existentes a baixo custo e ainda oferecer desempenho substancial. A implementação de maior sucesso foi o ARM7TDMI, com centenas de milhões de unidades vendidas. Atmel tem sido um centro de design precursor no sistema embarcado baseado em ARM7TDMI.

As arquiteturas ARM usadas em smartphones, PDAs e outros dispositivos móveis variam de ARMv5 a ARMv8-A.

Em 2009, alguns fabricantes lançaram netbooks baseados em CPUs de arquitetura ARM, em concorrência direta com netbooks baseados em Intel Atom.

Arm Ltd. oferece uma variedade de termos de licenciamento, variando em custo e resultados. Arm Ltd. fornece a todos os licenciados uma descrição de hardware integrável do núcleo ARM, bem como um conjunto completo de ferramentas de desenvolvimento de software (compilador, depurador, kit de desenvolvimento de software) e o direito de vender silício fabricado contendo a CPU ARM.

Os pacotes SoC que integram os designs principais da ARM incluem as três primeiras gerações da Nvidia Tegra, a família Quatro da CSR plc, a Nova e NovaThor da ST-Ericsson, a família Quatro da Silicon Labs. Precision32 MCU, produtos OMAP da Texas Instruments, produtos Hummingbird e Exynos da Samsung, A4, A5 e A5X da Apple e i.MX da NXP.

Os licenciados Fabless, que desejam integrar um núcleo ARM em seu próprio projeto de chip, geralmente só estão interessados em adquirir um núcleo de propriedade intelectual de semicondutor verificado, pronto para fabricação. Para esses clientes, a Arm Ltd. fornece uma descrição da lista de portas do núcleo ARM escolhido, juntamente com um modelo de simulação abstraído e programas de teste para auxiliar na integração e verificação do projeto. Clientes mais ambiciosos, incluindo fabricantes de dispositivos integrados (IDM) e operadores de fundição, optam por adquirir o IP do processador em formato RTL sintetizável (Verilog). Com o RTL sintetizável, o cliente tem a capacidade de realizar otimizações e extensões de nível arquitetônico. Isso permite que o projetista atinja objetivos de design exóticos que de outra forma não seriam possíveis com uma netlist não modificada (alta velocidade de clock, consumo de energia muito baixo, extensões de conjunto de instruções, etc.). Embora a Arm Ltd. não conceda ao licenciado o direito de revender a própria arquitetura ARM, os licenciados podem vender livremente produtos manufaturados, como dispositivos de chip, placas de avaliação e sistemas completos. As fundições comerciais podem ser um caso especial; eles não apenas têm permissão para vender silício acabado contendo núcleos ARM, mas geralmente detêm o direito de refabricar núcleos ARM para outros clientes.

A Arm Ltd. avalia sua propriedade intelectual com base no valor percebido. Núcleos ARM de desempenho inferior normalmente têm custos de licença mais baixos do que núcleos de desempenho superior. Em termos de implementação, um núcleo sintetizável custa mais do que um núcleo macro rígido (caixa preta). Para complicar a questão dos preços, uma fundição comercial que possua uma licença ARM, como a Samsung ou a Fujitsu, pode oferecer aos clientes fabulosos custos de licenciamento reduzidos. Em troca da aquisição do núcleo ARM por meio dos serviços internos de design da fundição, o cliente pode reduzir ou eliminar o pagamento da taxa de licença inicial da ARM.

Em comparação com fundições de semicondutores dedicadas (como TSMC e UMC) sem serviços de design internos, a Fujitsu/Samsung cobra de duas a três vezes mais por wafer fabricado. Para aplicações de baixo a médio volume, uma fundição de serviços de design oferece preços globais mais baixos (através do subsídio da taxa de licença). Para peças produzidas em massa de alto volume, a redução de custos a longo prazo alcançável através de preços mais baixos de wafer reduz o impacto dos custos de NRE (engenharia não recorrente) da ARM, tornando a fundição dedicada uma escolha melhor.

As empresas que desenvolveram chips com núcleos projetados pela Arm incluem a subsidiária Annapurna Labs da Amazon.com, Analog Devices, Apple, AppliedMicro (agora: MACOM Technology Solutions), Atmel, Broadcom, Cavium, Cypress Semiconductor, Freescale Semiconductor (agora NXP Semiconductors), Huawei, Intel, Maxim Integrated, Nvidia, NXP, Qualcomm, Renesas, Samsung Electronics, ST Microelectronics, Texas Instruments e Xilinx.

Construído com licença da tecnologia ARM Cortex

Em fevereiro de 2016, a ARM anunciou a licença Built on ARM Cortex Technology, muitas vezes abreviada para licença Built on Cortex (BoC). Esta licença permite que as empresas façam parceria com a ARM e façam modificações nos designs do ARM Cortex. Estas modificações de design não serão compartilhadas com outras empresas. Esses designs de núcleo semipersonalizados também têm liberdade de marca, por exemplo, Kryo 280.

As empresas que são atualmente licenciadas da tecnologia Built on ARM Cortex incluem a Qualcomm.

Licença de arquitetura

As empresas também podem obter uma licença de arquitetura ARM para projetar seus próprios núcleos de CPU usando os conjuntos de instruções ARM. Esses núcleos devem estar em total conformidade com a arquitetura ARM. As empresas que projetaram núcleos que implementam uma arquitetura ARM incluem Apple, AppliedMicro (agora: Ampere Computing), Broadcom, Cavium (agora: Marvell), Digital Equipment Corporation, Intel, Nvidia, Qualcomm, Samsung Electronics, Fujitsu e NUVIA Inc. adquirida pela Qualcomm em 2021).

Acesso flexível ARM

Em 16 de julho de 2019, a ARM anunciou o ARM Flexible Access. O ARM Flexible Access fornece acesso ilimitado à propriedade intelectual (IP) incluída no ARM para desenvolvimento. Taxas de licença por produto são exigidas quando o cliente chega à fita de fundição ou à prototipagem.

75% dos IPs mais recentes da ARM nos últimos dois anos estão incluídos no ARM Flexible Access. Em outubro de 2019:

- CPUs: Cortex-A5, Cortex-A7, Cortex-A32, Cortex-A34, Cortex-A35, Cortex-A53, Cortex-R5, Cortex-R8, Cortex-R52, Cortex-M0, Cortex-M0+, Cortex-M3, Cortex-M4, Cortex-M7, Cortex-M23, Cortex-M33

- GPUs: Mali-G52, Mali-G31. Inclui kits de desenvolvimento de drivers Mali (DDK).

- Interconexão: CoreLink NIC-400, CoreLink NIC-450, CoreLink CCI-400, CoreLink CCI-500, CoreLink CCI-550, ADB-400 AMBA, XHB-400 AXI-AHB

- Controladores do Sistema: CoreLink GIC-400, CoreLink GIC-500, PL192 VIC, BP141 Trust Zone Memory Wrapper, CoreLink TZC-400, CoreLink L2C-310, CoreLink MMU-500, BP140 Memory Interface

- IP de segurança: CryptoCell-312, CryptoCell-712, confiança Gerador de números aleatórios

- Controladores periféricos: PL011 UART, PL022 SPI, PL031 RTC

- Debug & Trace: CoreSight SoC-400, CoreSight SDC-600, CoreSight STM-500, CoreSight System Trace Macrocell, CoreSight Trace Memory Controller

- Kits de Design: Corstone-101, Corstone-201

- IP físico: Artisan PIK para Cortex-M33 TSMC 22ULL incluindo compiladores de memória, bibliotecas lógicas, GPIOs e documentação

- Ferramentas e Materiais: Socrates IP ToolingARM Design Studio, Modelos de Sistema Virtual

- Suporte: ARM padrão Suporte técnico, treinamento online ARM, atualizações de manutenção, créditos para treinamento no local e avaliações de design

Núcleos

| Arquitetura | Núcleo bit-largura | Núcleos | Perfil | Refe... rences | |

|---|---|---|---|---|---|

| Arm Ltd. | Terceiros | ||||

ARMv1 | 32 | ARM1 | Clássico | ||

ARMv2 | 32 | ARM2, ARM250, ARM3 | Amber, STORM Open Soft Core | Clássico | |

ARMv3 | 32 | ARM6, ARM7 | Clássico | ||

ARMV4 | 32 | ARM8 | StrongARM, FA526, ZAP Open Source Processor Core | Clássico | |

ARMV4T | 32 | ARM7TDMI, ARM9TDMI, SecurCore SC100 | Clássico | ||

ARMv5TE | 32 | ARM7EJ, ARM9E, ARM10E | XScale, FA626TE, Feroceon, PJ1/Mohawk | Clássico | |

ARMV6 | 32 | ARM11 | Clássico | ||

ARMv6-M | 32 | ARM Cortex-M0, ARM Cortex-M0+, ARM Cortex-M1, SecurCore SC000 | Microcontrolador | ||

ARMv7-M | 32 | ARM Cortex-M3, SecurCore SC300 | Coprocessador de movimento Apple M7 | Microcontrolador | |

ARMv7E-M | 32 | ARM Cortex-M4, ARM Cortex-M7 | Microcontrolador | ||

ARMv8-M | 32 | ARM Cortex-M23, ARM Cortex-M33 | Microcontrolador | ||

ARMv8.1-M | 32 | ARM Cortex-M55, ARM Cortex-M85 | Microcontrolador | ||

ARMv7-R | 32 | ARM Cortex-R4, ARM Cortex-R5, ARM Cortex-R7, ARM Cortex-R8 | Em tempo real | ||

ARMv8-R | 32 | ARM Cortex-R52 | Em tempo real | ||

64 | ARM Cortex-R82 | Em tempo real | |||

ARMv7-A | 32 | ARM Cortex-A5, ARM Cortex-A7, ARM Cortex-A8, ARM Cortex-A9, ARM Cortex-A12, ARM Cortex-A15, ARM Cortex-A17 | Qualcomm Scorpion/Krait, PJ4/Sheeva, Apple Swift (A6, A6X) | Aplicação | |

ARMv8-A | 32 | ARM Cortex-A32 | Aplicação | ||

64/32 | ARM Cortex-A35, ARM Cortex-A53, ARM Cortex-A57, ARM Cortex-A72, ARM Cortex-A73 | X-Gene, Nvidia Denver 1/2, Cavium ThunderX, AMD K12, Apple Cyclone (A7)/Typhoon (A8, A8X)/Twister (A9, A9X)/Hurricane+Zephyr (A10, A10X), Qualcomm Kryo, Samsung M1/M2 ("Mongoose") /M3 ("Meerkat") | Aplicação | ||

64 | ARM Cortex-A34 | Aplicação | |||

ARMv8.1-A | 64/32 | TBA | Cavium ThunderX2 | Aplicação | |

ARMv8.2-A | 64/32 | ARM Cortex-A55, ARM Cortex-A75, ARM Cortex-A76, ARM Cortex-A77, ARM Cortex-A78, ARM Cortex-X1, ARM Neoverse N1 | Nvidia Carmel, Samsung M4 ("Cheetah"), Fujitsu A64FX (ARMv8 SVE 512-bit) | Aplicação | |

64 | ARM Cortex-A65, ARM Neoverse E1 com multithreading simultâneo (SMT), ARM Cortex-A65AE (também tendo, por exemplo, ARMv8.4 Dot Product; feito para tarefas críticas de segurança, tais como sistemas avançados de assistência ao condutor (ADAS)) | Apple Monsoon+Mistral (A11) (Setembro 2017) | Aplicação | ||

ARMv8.3-A | 64/32 | TBA | Aplicação | ||

64 | TBA | Apple Vortex+Tempest (A12, A12X, A12Z), Marvell ThunderX3 (v8.3+) | Aplicação | ||

ARMv8.4-A | 64/32 | TBA | Aplicação | ||

64 | ARM Neoverse V1 | Apple Lightning+Thunder (A13), Apple Firestorm+Icestorm (A14, M1) | Aplicação | ||

ARMv8.5-A | 64/32 | TBA | Aplicação | ||

64 | TBA | Aplicação | |||

ARMv8.6-A | 64 | TBA | Apple Avalanche+Blizzard (A15, M2), Apple Everest+Sawtooth (A16) | Aplicação | |

ARMv8.7-A | 64 | TBA | Aplicação | ||

ARMv8.8-A | 64 | TBA | Aplicação | ||

ARMv8.9-A | 64 | TBA | Aplicação | ||

ARMv9.0-A | 64 | ARM Cortex-A510, ARM Cortex-A710, ARM Cortex-A715, ARM Cortex-X2, ARM Cortex-X3, ARM Neoverse E2, ARM Neoverse N2, ARM Neoverse V2 | Aplicação | ||

ARMv9.1-A | 64 | TBA | Aplicação | ||

ARMv9.2-A | 64 | ARM Cortex-A520, ARM Cortex-A720, ARM Cortex-X4 | Aplicação | ||

ARMv9.3-A | 64 | TBA | Aplicação | ||

ARMv9.4-A | 64 | TBA | Aplicação | ||

- ↑ a b Embora a maioria dos datapaths e registros de CPU nos processadores ARM iniciais fossem de 32 bits, a memória endereçável foi limitada a 26 bits; com bits superiores, então, usado para bandeiras de status no registro do contador do programa.

- ↑ a b c ARMv3 incluiu um modo de compatibilidade para suportar os endereços de 26 bits de versões anteriores da arquitetura. Este modo de compatibilidade opcional em ARMv4, e removido inteiramente em ARMv5.

Arm fornece uma lista de fornecedores que implementam núcleos ARM em seu design (produtos padrão específicos de aplicativos (ASSP), microprocessadores e microcontroladores).

Exemplos de aplicações de núcleos ARM

Os núcleos ARM são usados em vários produtos, principalmente em PDAs e smartphones. Alguns exemplos de computação são os dispositivos Surface, Surface 2 e Pocket PC de primeira geração da Microsoft (após 2002), os iPads da Apple e os tablets Eee Pad Transformer da Asus e vários laptops Chromebook. Outros incluem os smartphones iPhone da Apple e os reprodutores de mídia portáteis iPod, as câmeras digitais Canon PowerShot, o híbrido Nintendo Switch, o processador de segurança Wii e os consoles de jogos portáteis 3DS e os sistemas de navegação passo a passo da TomTom.

Em 2005, Arm participou do desenvolvimento do computador SpiNNaker da Universidade de Manchester, que usava núcleos ARM para simular o cérebro humano.

Os chips ARM também são usados em Raspberry Pi, BeagleBoard, BeagleBone, PandaBoard e outros computadores de placa única porque são muito pequenos, baratos e consomem muito pouca energia.

Arquitetura de 32 bits

A arquitetura ARM de 32 bits (ARM32), como Armv7-A (implementando AArch32; veja a seção sobre Armv8-A para mais informações), foi a arquitetura mais amplamente usada em dispositivos móveis em 2011.

Desde 1995, várias versões do Manual de referência da arquitetura ARM (ver § Links externos) têm sido a principal fonte de documentação sobre a arquitetura e o conjunto de instruções do processador ARM, distinguindo as interfaces que todos os processadores ARM são necessário para dar suporte (como semântica de instrução) a partir de detalhes de implementação que podem variar. A arquitetura evoluiu ao longo do tempo, e a versão sete da arquitetura, ARMv7, define três “perfis” de arquitetura:

- A-profile, o perfil "Aplicação", implementado por núcleos de 32 bits na série Cortex-A e por alguns núcleos não-ARM

- R-profile, o perfil "Real-time", implementado por núcleos na série Cortex-R

- M-profile, o perfil "Microcontroller", implementado pela maioria dos núcleos na série Cortex-M

Embora os perfis de arquitetura tenham sido definidos primeiro para ARMv7, a ARM posteriormente definiu a arquitetura ARMv6-M (usada pelo Cortex M0/M0+/M1) como um subconjunto do perfil ARMv7-M com menos instruções.

Modos de CPU

Exceto no perfil M, a arquitetura ARM de 32 bits especifica vários modos de CPU, dependendo dos recursos da arquitetura implementada. A qualquer momento, a CPU pode estar em apenas um modo, mas pode alternar entre modos devido a eventos externos (interrupções) ou programaticamente.

- Modo de utilização: O único modo não privilegiado.

- Modo FIQ: Um modo privilegiado que é inserido sempre que o processador aceita um pedido de interrupção rápida.

- Modo IRQ: Um modo privilegiado que é inserido sempre que o processador aceita uma interrupção.

- Modo de supervisão (svc): Um modo privilegiado entrou sempre que a CPU é reiniciada ou quando uma instrução SVC é executada.

- Modo de aborto: Um modo privilegiado que é inserido sempre que ocorre um aborto pré-envio ou uma exceção de abortamento de dados.

- Modo indefinido: Um modo privilegiado que é inserido sempre que ocorre uma exceção de instrução indefinida.

- Modo de sistema (ARMv4 e acima): O único modo privilegiado que não é inserido por uma exceção. Ele só pode ser inserido executando uma instrução que escreve explicitamente para os bits de modo do Registro de Estado do Programa atual (CPSR) de outro modo privilegiado (não do modo de usuário).

- Modo de monitor (extensões de segurança ARMv6 e ARMv7, ARMv8 EL3): Um modo de monitor é introduzido para suportar a extensão TrustZone em núcleos ARM.

- Modo Hyp (ARMv7 Virtualization Extensions, ARMv8 EL2): Um modo hipervisor que suporta os requisitos de virtualização Popek e Goldberg para a operação não segura da CPU.

- Modo de rosca (ARMv6-M, ARMv7-M, ARMv8-M): Um modo que pode ser especificado como privilegiado ou não privilegiado. Se o principal Stack Pointer (MSP) ou Process Stack Pointer (PSP) é usado também pode ser especificado no registro CONTROL com acesso privilegiado. Este modo é projetado para tarefas de usuário no ambiente RTOS, mas é tipicamente usado em bare-metal para super-loop.

- Modo de manuseador (ARMv6-M, ARMv7-M, ARMv8-M): Um modo dedicado ao manuseio de exceção (exceto o RESET que são tratados no modo Thread). Modo de manuseador sempre usa MSP e trabalha em nível privilegiado.

Conjunto de instruções

A implementação ARM original (e subsequente) foi conectada sem microcódigo, como o processador 6502 de 8 bits, muito mais simples, usado nos microcomputadores Acorn anteriores.

A arquitetura ARM de 32 bits (e a arquitetura de 64 bits em sua maior parte) inclui os seguintes recursos RISC:

- Arquitetura de armazenamento de carga.

- Não há suporte para acessos de memória não solicitados na versão original da arquitetura. ARMv6 e mais tarde, exceto algumas versões de microcontrolador, suportam acessos não solicitados para instruções de meia-palavra e de simples-palavra com algumas limitações, como nenhuma atômica garantida.

- Uniforme 16 × arquivo de registro de 32 bits (incluindo o contador do programa, ponteiro de pilha e o registro de link).

- Largura de instrução fixa de 32 bits para facilitar a decodificação e pipelining, ao custo da densidade de código diminuída. Mais tarde, o conjunto de instruções Thumb adicionou instruções de 16 bits e aumento da densidade de código.

- Principalmente execução de ciclo de relógio único.

Para compensar o design mais simples, em comparação com processadores como o Intel 80286 e o Motorola 68020, foram utilizados alguns recursos de design adicionais:

- A execução condicional da maioria das instruções reduz a sobrecarga de ramo e compensa a falta de um preditor de ramo em fichas iniciais.

- As instruções aritméticas alteram códigos de condição apenas quando desejado.

- O interruptor de barril de 32 bits pode ser usado sem penalidade de desempenho com a maioria das instruções aritméticas e cálculos de endereço.

- Tem modos de endereçamento indexados poderosos.

- Um registro de link suporta chamadas de função de folha rápida.

- Um subsistema de interrupção de nível de 2 prioridade, simples, mas rápido, comutou bancos de registro.

Instruções aritméticas

ARM inclui operações aritméticas inteiras para somar, subtrair e multiplicar; algumas versões da arquitetura também suportam operações de divisão.

O ARM suporta multiplicações de 32 bits × 32 bits com um resultado de 32 bits ou de 64 bits, embora os núcleos Cortex-M0 / M0+ / M1 não suportem resultados de 64 bits. Alguns núcleos ARM também suportam multiplicações de 16 bits × 16 bits e 32 bits × 16 bits.

As instruções de divisão estão incluídas apenas nas seguintes arquiteturas ARM:

- As arquiteturas Armv7-M e Armv7E-M sempre incluem instruções de divisão.

- A arquitetura Armv7-R sempre inclui instruções de divisão no conjunto de instruções Thumb, mas opcionalmente em seu conjunto de instruções de 32 bits.

- Armv7-A arquitetura opcionalmente inclui as instruções de divisão. As instruções podem não ser implementadas, ou implementadas apenas no conjunto de instruções Thumb, ou implementadas nos conjuntos de instruções Thumb e ARM, ou implementadas se as extensões de virtualização forem incluídas.

Registros

| Wer | sys | Svc | Abdt | Não. | Ir. | Fiq |

|---|---|---|---|---|---|---|

| R0 | ||||||

| R1 | ||||||

| R2 | ||||||

| R3 | ||||||

| R4 | ||||||

| R5 | ||||||

| R6 | ||||||

| R7 | ||||||

| R8 | R8_fiq | |||||

| R9 | R9_fiq | |||||

| R10 | R10_fiq | |||||

| R11 | R11_fiq | |||||

| R12 | R12_fiq | |||||

| R13 | R13_svc | R13_abt | R13_und | R13_irq | R13_fiq | |

| R14 | R14_svc | R14_abt | R14_und | R14_irq | R14_fiq | |

| R15 | ||||||

| CPSR | ||||||

| SPSR-svc | SPSR_abt | SPSR_und | SPSR_irq | SPSR_fiq | ||

Os registros R0 a R7 são iguais em todos os modos de CPU; eles nunca são bancarizados.

Os registros R8 a R12 são iguais em todos os modos de CPU, exceto no modo FIQ. O modo FIQ possui seus próprios registros R8 a R12 distintos.

R13 e R14 são armazenados em todos os modos de CPU privilegiados, exceto no modo de sistema. Ou seja, cada modo que pode ser acessado devido a uma exceção possui seu próprio R13 e R14. Esses registradores geralmente contêm o ponteiro da pilha e o endereço de retorno das chamadas de função, respectivamente.

Alias:

- R13 também é referido como SP, o ponteiro da pilha.

- R14 também é referido como LR, o registro de link.

- R15 também é referido como PC, o contador do programa.

O Registro de Status do Programa Atual (CPSR) tem os seguintes 32 bits.

- M (bits 0–4) é o modo de bits do processador.

- T (bit 5) é a parte do estado de Thumb.

- F (bit 6) é o FIQ desabilitar bit.

- I (bit 7) é o IRQ desabilitar bit.

- A (bit 8) é os dados imprecisos abortar o bit de desabilitar.

- E (bit 9) é o bit de endianness dos dados.

- A TI (bits 10–15 e 25–26) é os bits do estado if-then.

- GE (bits 16–19) é o maior do que igual a bits.

- DNM (bits 20–23) é o não modificar bits.

- J (bit 24) é o bit de estado Java.

- Q (bit 27) é o bit de transbordamento pegajoso.

- V (bit 28) é o bit de transbordamento.

- C (bit 29) é o carreg/borrow/extend bit.

- Z (bit 30) é o zero bit.

- N (bit 31) é o negativo/menos do que o bit.

Execução condicional

Quase todas as instruções ARM possuem um recurso de execução condicional chamado predicação, que é implementado com um seletor de código de condição de 4 bits (o predicado). Para permitir a execução incondicional, um dos códigos de quatro bits faz com que a instrução seja sempre executada. A maioria das outras arquiteturas de CPU possui apenas códigos de condição em instruções de ramificação.

Embora o predicado ocupe quatro dos 32 bits em um código de instrução e, portanto, reduza significativamente os bits de codificação disponíveis para deslocamentos em instruções de acesso à memória, ele evita instruções de desvio ao gerar código para instruções if pequenas. Além de eliminar as próprias instruções de desvio, isso preserva o pipeline de busca/decodificação/execução ao custo de apenas um ciclo por instrução ignorada.

Um algoritmo que fornece um bom exemplo de execução condicional é o algoritmo euclidiano baseado em subtração para calcular o máximo divisor comum. Na linguagem de programação C, o algoritmo pode ser escrito como:

- Não. Gcd(- Não. um, - Não. b)) ( enquanto (um ! b)) // Entramos no loop quando um < b ou a > b, mas não quando a == b se (um > b)) // Quando um > b o fizermos um - Sim. b); mais // Quando um < b nós fazemos isso (nenhum "se (a < b)" necessário desde um != b é verificado durante a condição) b) - Sim. um; retorno um;?O mesmo algoritmo pode ser reescrito de uma forma mais próxima das instruções ARM alvo como:

loop: // Comparar a e b GT = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = um > b); LT = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = um < b); N. = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = um ! b); // Executar operações com base nos resultados da bandeira se (GT) um - Sim. b); // Subtrair *apenas* se maior do que se (LT) b) - Sim. um; // Subtrair *apenas* se menos do que se (N.) Goto loop; // Loop *only* se os valores comparados não forem iguais retorno um;e codificado em linguagem assembly como:

; atribuir um registo r0, b a r1loop: CMP R0, ) ; condição definida "NE" se (a ≠ b), ; "GT" se (a > b), ; ou "LT" se (a < b) ASSUNTO R0, R0, ) ; se "GT" (Greater Than), então a = a − b ASSUNTOS ), ), R0 ; se "LT" (Less Than), então b = b − a BNE loop ; se "NE" (não igual), então loop B Ir. ; retornoque evita as ramificações em torno das cláusulas then e else. Se r0 e r1 forem iguais então nenhuma das instruções SUB será executada, eliminando a necessidade de uma ramificação condicional para implementar o while verifica no topo do loop, por exemplo, se SUBLE (menor ou igual) foi usado.

Uma das maneiras pelas quais o código Thumb fornece uma codificação mais densa é remover o seletor de quatro bits das instruções que não são de ramificação.

Outros recursos

Outra característica do conjunto de instruções é a capacidade de incorporar deslocamentos e rotações nas instruções de processamento de dados (aritmética, lógica e movimento de registro-registro), de modo que, por exemplo, a instrução em Linguagem C:

um - Sim. (JJ < < 2);pode ser renderizado como uma instrução de uma palavra e um ciclo:

ADD Ra, Ra, RJ, LSL #2Isso faz com que o programa ARM típico seja mais denso do que o esperado, com menos acessos à memória; assim, o pipeline é usado de forma mais eficiente.

O processador ARM também possui recursos raramente vistos em outras arquiteturas RISC, como endereçamento relativo ao PC (na verdade, no ARM de 32 bits o PC é um de seus 16 registros) e modos de endereçamento pré e pós-incremento.

O conjunto de instruções ARM aumentou com o tempo. Alguns processadores ARM anteriores (antes do ARM7TDMI), por exemplo, não possuem instruções para armazenar uma quantidade de dois bytes.

Pipelines e outros problemas de implementação

O ARM7 e implementações anteriores têm um pipeline de três estágios; os estágios são buscar, decodificar e executar. Projetos de alto desempenho, como o ARM9, possuem pipelines mais profundos: o Cortex-A8 possui treze estágios. Mudanças adicionais de implementação para maior desempenho incluem um somador mais rápido e uma lógica de previsão de ramificação mais extensa. A diferença entre os núcleos ARM7DI e ARM7DMI, por exemplo, foi um multiplicador melhorado; daí o "M" adicionado.

Coprocessadores

A arquitetura ARM (pré-Armv8) fornece uma maneira não intrusiva de estender o conjunto de instruções usando "coprocessadores" que podem ser abordados usando MCR, MRC, MRRC, MCRR e instruções semelhantes. O espaço do coprocessador é dividido logicamente em 16 coprocessadores com números de 0 a 15, sendo o coprocessador 15 (cp15) reservado para algumas funções de controle típicas, como gerenciamento de caches e operação de MMU em processadores que possuem um.

Em máquinas baseadas em ARM, os dispositivos periféricos geralmente são conectados ao processador mapeando seus registros físicos no espaço de memória ARM, no espaço do coprocessador ou conectando-se a outro dispositivo (um barramento) que, por sua vez, se conecta ao processador. Os acessos ao coprocessador têm latência mais baixa, portanto, alguns periféricos — por exemplo, um controlador de interrupção XScale — são acessíveis de duas maneiras: através da memória e através de coprocessadores.

Em outros casos, os projetistas de chips apenas integram o hardware usando o mecanismo do coprocessador. Por exemplo, um mecanismo de processamento de imagem pode ser um pequeno núcleo ARM7TDMI combinado com um coprocessador que possui operações especializadas para suportar um conjunto específico de primitivas de transcodificação de HDTV.

Depuração

Todos os processadores ARM modernos incluem recursos de depuração de hardware, permitindo que depuradores de software executem operações como parada, revisão e ponto de interrupção de código a partir da redefinição. Essas instalações são construídas usando suporte JTAG, embora alguns núcleos mais novos suportem opcionalmente o próprio "SWD" protocolo. Nos núcleos ARM7TDMI, o "D" representou suporte para depuração JTAG e o "I" representou a presença de um "EmbeddedICE" módulo de depuração. Para as gerações principais ARM7 e ARM9, EmbeddedICE sobre JTAG era um padrão de depuração de fato, embora não fosse garantido arquitetonicamente.

A arquitetura ARMv7 define recursos básicos de depuração em nível arquitetônico. Isso inclui pontos de interrupção, pontos de controle e execução de instruções em um "modo de depuração"; instalações semelhantes também estavam disponíveis com o EmbeddedICE. Tanto o "modo de parada" e "monitorar" depuração de modo são suportadas. O mecanismo de transporte real usado para acessar os recursos de depuração não é especificado arquitetonicamente, mas as implementações geralmente incluem suporte JTAG.

Existe um ARM "CoreSight" arquitetura de depuração, que não é exigida arquitetonicamente pelos processadores ARMv7.

Porta de acesso de depuração

A porta de acesso de depuração (DAP) é uma implementação de uma interface de depuração ARM. Existem duas implementações diferentes suportadas, a porta de depuração JTAG de fio serial (SWJ-DP) e a porta de depuração de fio serial (SW-DP). CMSIS-DAP é uma interface padrão que descreve como vários softwares de depuração em um PC host podem se comunicar por USB com o firmware executado em um depurador de hardware, que por sua vez se comunica por SWD ou JTAG com uma CPU ARM Cortex habilitada para CoreSight.

Instruções de aprimoramento de DSP

Para melhorar a arquitetura ARM para processamento de sinais digitais e aplicações multimídia, instruções DSP foram adicionadas ao conjunto. Estes são representados por um "E" em nome das arquiteturas ARMv5TE e ARMv5TEJ. As variantes E também implicam T, D, M e I.

As novas instruções são comuns em arquiteturas de processadores de sinais digitais (DSP). Eles incluem variações de multiplicação-acumulação com sinal, adição e subtração saturada e contagem de zeros à esquerda.

Extensões SIMD para multimídia

Introduzido na arquitetura ARMv6, foi um precursor do Advanced SIMD, também chamado Neon.

Jazelle

Jazelle DBX (Direct Bytecode eXecution) é uma técnica que permite que o bytecode Java seja executado diretamente na arquitetura ARM como um terceiro estado de execução (e conjunto de instruções) junto com o ARM e o modo Thumb existentes. O apoio para este estado é representado pelo símbolo "J" na arquitetura ARMv5TEJ e nos nomes principais ARM9EJ-S e ARM7EJ-S. O suporte para este estado é necessário a partir do ARMv6 (exceto para o perfil ARMv7-M), embora os núcleos mais recentes incluam apenas uma implementação trivial que não fornece aceleração de hardware.

Polegar

Para melhorar a densidade do código compilado, os processadores desde o ARM7TDMI (lançado em 1994) apresentam o conjunto de instruções Thumb, que possuem seu próprio estado. (O "T" em "TDMI" indica o recurso Thumb.) Quando neste estado, o processador executa o conjunto de instruções Thumb, uma codificação compacta de 16 bits para um subconjunto do ARM conjunto de instruções. A maioria das instruções Thumb são mapeadas diretamente para instruções ARM normais. A economia de espaço vem de tornar implícitos alguns dos operandos de instrução e limitar o número de possibilidades em comparação com as instruções ARM executadas no estado do conjunto de instruções ARM.

No Thumb, os opcodes de 16 bits têm menos funcionalidade. Por exemplo, apenas ramificações podem ser condicionais e muitos opcodes são restritos a acessar apenas metade de todos os registradores de uso geral da CPU. Os opcodes mais curtos proporcionam uma densidade geral de código melhorada, embora algumas operações exijam instruções extras. Em situações em que a porta de memória ou a largura do barramento são restritas a menos de 32 bits, os opcodes Thumb mais curtos permitem maior desempenho em comparação com o código ARM de 32 bits, pois pode ser necessário carregar menos código de programa no processador através da largura de banda de memória restrita.

Ao contrário das arquiteturas de processador com instruções de comprimento variável (16 ou 32 bits), como Cray-1 e Hitachi SuperH, os conjuntos de instruções ARM e Thumb existem independentemente um do outro. Hardware incorporado, como o Game Boy Advance, normalmente possui uma pequena quantidade de RAM acessível com um caminho de dados completo de 32 bits; a maioria é acessada por meio de um caminho de dados secundário de 16 bits ou mais estreito. Nessa situação, geralmente faz sentido compilar o código Thumb e otimizar manualmente algumas das seções que exigem mais uso da CPU usando instruções ARM completas de 32 bits, colocando essas instruções mais amplas na memória acessível pelo barramento de 32 bits.

O primeiro processador com um decodificador de instruções Thumb foi o ARM7TDMI. Todas as famílias ARM9 e posteriores, incluindo XScale, incluíram um decodificador de instruções Thumb. Inclui instruções adotadas do Hitachi SuperH (1992), licenciado pela ARM. As menores famílias de processadores ARM (Cortex M0 e M1) implementam apenas o conjunto de instruções Thumb de 16 bits para desempenho máximo em aplicativos de menor custo.

Polegar-2

A tecnologiaThumb-2 foi introduzida no núcleo ARM1156, anunciado em 2003. Thumb-2 estende o conjunto limitado de instruções de 16 bits do Thumb com 32 bits adicionais instruções para dar mais amplitude ao conjunto de instruções, produzindo assim um conjunto de instruções de comprimento variável. Um objetivo declarado do Thumb-2 era alcançar densidade de código semelhante ao Thumb com desempenho semelhante ao conjunto de instruções ARM na memória de 32 bits.

Thumb-2 estende o conjunto de instruções Thumb com manipulação de campos de bits, ramificações de tabelas e execução condicional. Ao mesmo tempo, o conjunto de instruções ARM foi estendido para manter funcionalidade equivalente em ambos os conjuntos de instruções. Uma nova 'Linguagem Assembly Unificada' (UAL) suporta a geração de instruções Thumb ou ARM a partir do mesmo código-fonte; versões do Thumb vistas em processadores ARMv7 são essencialmente tão capazes quanto o código ARM (incluindo a capacidade de escrever manipuladores de interrupção). Isso requer um pouco de cuidado e o uso de uma nova "TI" (se-então) instrução, que permite a execução de até quatro instruções sucessivas com base em uma condição testada ou em seu inverso. Ao compilar em código ARM, isso é ignorado, mas ao compilar em Thumb gera uma instrução real. Por exemplo:

; se (r0 == r1)CMP R0, )ITE EQ ; ARM: nenhum código... Thumb: instrução de TI; então r0 = r2;MOVIMENTO R0, R2 ; ARM: condicional; Thumb: condição via ITE 'T' (então); outros r0 = r3;MOVIMENTO R0, R3 ; ARM: condicional; Thumb: condição via ITE 'E' (else); lembre-se que a instrução Thumb MOV não tem bits para codificar "EQ" ou "NE".Todos os chips ARMv7 suportam o conjunto de instruções Thumb. Todos os chips da série Cortex-A, série Cortex-R e série ARM11 suportam tanto o "estado do conjunto de instruções ARM" e 'Estado do conjunto de instruções Thumb', enquanto os chips da série Cortex-M suportam apenas o conjunto de instruções Thumb.

Ambiente de execução de polegar (ThumbEE)

ThumbEE (erroneamente chamado de Thumb-2EE em algumas documentações ARM), que foi comercializado como Jazelle RCT (Runtime Compilation Target), foi anunciado em 2005 e descontinuado em 2011 Ele apareceu pela primeira vez no processador Cortex-A8. ThumbEE é um quarto estado do conjunto de instruções, fazendo pequenas alterações no conjunto de instruções estendido do Thumb-2. Essas mudanças tornam o conjunto de instruções particularmente adequado para código gerado em tempo de execução (por exemplo, por compilação JIT) em ambientes de execução gerenciados. ThumbEE é um alvo para linguagens como Java, C#, Perl e Python e permite que compiladores JIT produzam código compilado menor sem reduzir o desempenho.

Novos recursos fornecidos pelo ThumbEE incluem verificações automáticas de ponteiro nulo em cada instrução de carregamento e armazenamento, uma instrução para realizar uma verificação de limites de array e instruções especiais que chamam um manipulador. Além disso, por utilizar a tecnologia Thumb-2, o ThumbEE fornece acesso aos registradores r8–r15 (onde o estado Jazelle/DBX Java VM é mantido). Manipuladores são pequenas seções de código frequentemente chamadas, comumente usadas para implementar linguagens de alto nível, como alocação de memória para um novo objeto. Essas mudanças vêm do reaproveitamento de alguns opcodes e do conhecimento de que o núcleo está no novo estado ThumbEE.

Em 23 de novembro de 2011, Arm descontinua qualquer uso do conjunto de instruções ThumbEE e Armv8 remove o suporte para ThumbEE.

Ponto flutuante (VFP)

A tecnologiaVFP (Vector Floating Point) é uma extensão do coprocessador de unidade de ponto flutuante (FPU) para a arquitetura ARM (implementada de forma diferente no Armv8 – coprocessadores não definidos lá). Ele fornece computação de ponto flutuante de precisão simples e dupla de baixo custo, totalmente compatível com o Padrão ANSI/IEEE Std 754-1985 para aritmética de ponto flutuante binário. O VFP fornece computação de ponto flutuante adequada para um amplo espectro de aplicações, como PDAs, smartphones, compressão e descompressão de voz, gráficos tridimensionais e áudio digital, impressoras, decodificadores e aplicações automotivas. A arquitetura VFP foi projetada para suportar a execução de "modo vetorial" instruções, mas estas operavam em cada elemento do vetor sequencialmente e, portanto, não ofereciam o desempenho do verdadeiro paralelismo vetorial de instrução única e dados múltiplos (SIMD). Este modo vetorial foi, portanto, removido logo após sua introdução, para ser substituído pelo muito mais poderoso SIMD Avançado, também denominado Neon.

Alguns dispositivos, como o ARM Cortex-A8, possuem um módulo VFPLite reduzido em vez de um módulo VFP completo e exigem cerca de dez vezes mais ciclos de clock por operação flutuante. A arquitetura pré-Armv8 implementou ponto flutuante/SIMD com a interface do coprocessador. Outras unidades de ponto flutuante e/ou SIMD encontradas em processadores baseados em ARM usando a interface do coprocessador incluem FPA, FPE, iwMMXt, algumas das quais foram implementadas em software por interceptação, mas poderiam ter sido implementadas em hardware. Eles fornecem algumas das mesmas funcionalidades do VFP, mas não são compatíveis com opcode. O FPA10 também fornece precisão estendida, mas implementa o arredondamento correto (exigido pela IEEE 754) apenas em precisão única.

- VFPv1

- Obsoleto

- VFPv2

- Uma extensão opcional à instrução ARM definida nas arquiteturas ARMv5TE, ARMv5TEJ e ARMv6. VFPv2 tem 16 registros FPU de 64 bits.

- VFPv3 ou VFPv3-D32

- Implementado na maioria dos processadores Cortex-A8 e A9 ARMv7. É compatível com VFPv2, exceto que não pode prender exceções de ponto flutuante. VFPv3 tem 32 registros FPU de 64 bits como padrão, adiciona instruções VCVT para converter entre escalar, flutuar e duplo, adiciona modo imediato para VMOV tal que as constantes podem ser carregadas em registros FPU.

- VFPv3-D16

- Como acima, mas com apenas 16 registros FPU de 64 bits. Implementado em processadores Cortex-R4 e R5 e Tegra 2 (Cortex-A9).

- VFPv3-F16

- Incomun; suporta ponto flutuante de meia-precisão IEEE754-2008 (16-bit) como um formato de armazenamento.

- VFPv4 ou VFPv4-D32

- Implementado em processadores Cortex-A12 e A15 ARMv7, Cortex-A7 opcionalmente tem VFPv4-D32 no caso de uma FPU com Neon. VFPv4 tem 32 registros FPU de 64 bits como padrão, adiciona suporte de meia precisão como um formato de armazenamento e instruções multiply-acumuladas fundidos para as características de VFPv3.

- VFPv4-D16

- Como acima, mas tem apenas 16 64-bit FPU registrados. Implementado em processadores Cortex-A5 e A7 no caso de uma FPU sem Neon.

- VFPv5-D16-M

- Implementado no Cortex-M7 quando existe uma opção de núcleo de ponto flutuante única e de dupla precisão.

No Debian Linux e derivados como Ubuntu e Linux Mint, armhf (ARM hard float) refere-se à arquitetura ARMv7 incluindo o hardware adicional de ponto flutuante VFP3-D16 extensão (e Thumb-2) acima. Pacotes de software e ferramentas de compilador cruzado usam os sufixos armhf vs. arm/armel para diferenciar.

SIMD avançado (néon)

A extensão Advanced SIMD (também conhecida como Neon ou "MPE" Media Processing Engine) é uma instrução SIMD combinada de 64 e 128 bits conjunto que fornece aceleração padronizada para aplicações de processamento de mídia e sinal. Neon está incluído em todos os dispositivos Cortex-A8, mas é opcional em dispositivos Cortex-A9. O Neon pode executar decodificação de áudio MP3 em CPUs rodando a 10 MHz e pode executar o codec de voz GSM adaptativo multitaxa (AMR) a 13 MHz. Possui um conjunto abrangente de instruções, arquivos de registro separados e hardware de execução independente. Neon oferece suporte a números inteiros de 8, 16, 32 e 64 bits e dados de ponto flutuante de precisão simples (32 bits) e operações SIMD para lidar com processamento de áudio e vídeo, bem como processamento de gráficos e jogos. No Neon, o SIMD suporta até 16 operações ao mesmo tempo. O hardware Neon compartilha os mesmos registros de ponto flutuante usados no VFP. Dispositivos como ARM Cortex-A8 e Cortex-A9 suportam vetores de 128 bits, mas serão executados com 64 bits por vez, enquanto os dispositivos Cortex-A15 mais recentes podem executar 128 bits por vez.

Uma peculiaridade do Neon nos dispositivos Armv7 é que ele libera todos os números subnormais para zero e, como resultado, o compilador GCC não o usará, a menos que -funsafe-math-optimizations, que permite a perda de denormais, está ativado. "Aprimorado" O Neon definido desde o Armv8 não tem essa peculiaridade, mas a partir do GCC 8.2 o mesmo sinalizador ainda é necessário para ativar as instruções do Neon. Por outro lado, o GCC considera o Neon seguro no AArch64 para Armv8.

ProjectNe10 é o primeiro projeto de código aberto da ARM (desde o seu início; enquanto eles adquiriram um projeto mais antigo, agora denominado Mbed TLS). A biblioteca Ne10 é um conjunto de funções úteis e comuns escritas em Neon e C (para compatibilidade). A biblioteca foi criada para permitir que os desenvolvedores usem otimizações do Neon sem aprender o Neon, mas também serve como um conjunto de exemplos de código intrínseco e assembly do Neon altamente otimizados para rotinas comuns de DSP, aritmética e processamento de imagem. O código-fonte está disponível no GitHub.

Tecnologia ARM Hélio

Hélio é a extensão vetorial M-Profile (MVE). Adiciona mais de 150 instruções escalares e vetoriais.

Extensões de segurança

TrustZone (para perfil Cortex-A)

As extensões de segurança, comercializadas como tecnologia TrustZone, estão em ARMv6KZ e em arquiteturas de perfil de aplicativo posteriores. Ele fornece uma alternativa de baixo custo para adicionar outro núcleo de segurança dedicado a um SoC, fornecendo dois processadores virtuais apoiados por controle de acesso baseado em hardware. Isso permite que o núcleo do aplicativo alterne entre dois estados, chamados de mundos (para reduzir a confusão com outros nomes de domínios de capacidade), para evitar o vazamento de informações do mundo mais confiável para o mundo menos confiável. Essa mudança de mundo é geralmente ortogonal a todos os outros recursos do processador, portanto, cada mundo pode operar independentemente do outro enquanto usa o mesmo núcleo. A memória e os periféricos são então informados sobre o mundo operacional do núcleo e podem usar isso para fornecer controle de acesso a segredos e códigos no dispositivo.

Normalmente, um sistema operacional rico é executado no mundo menos confiável, com códigos menores especializados em segurança no mundo mais confiável, com o objetivo de reduzir a superfície de ataque. As aplicações típicas incluem funcionalidade DRM para controlar o uso de mídia em dispositivos baseados em ARM e impedir qualquer uso não aprovado do dispositivo.

Na prática, como os detalhes específicos de implementação de implementações proprietárias do TrustZone não foram divulgados publicamente para revisão, não está claro qual nível de garantia é fornecido para um determinado modelo de ameaça, mas eles não estão imunes a ataques.

Open Virtualization é uma implementação de código aberto da arquitetura mundial confiável do TrustZone.

A AMD licenciou e incorporou a tecnologia TrustZone em sua tecnologia de processador seguro. Habilitadas em alguns produtos, mas não em todos, as APUs da AMD incluem um processador Cortex-A5 para lidar com processamento seguro. Na verdade, o núcleo Cortex-A5 TrustZone foi incluído em produtos AMD anteriores, mas não foi habilitado devido a limitações de tempo.

O Samsung Knox usa o TrustZone para fins como detectar modificações no kernel, armazenar certificados e atestar chaves.

TrustZone para Armv8-M (para perfil Cortex-M)

A extensão de segurança, comercializada como TrustZone para tecnologia Armv8-M, foi introduzida na arquitetura Armv8-M. Embora contenha conceitos semelhantes ao TrustZone para Armv8-A, ele possui um design arquitetônico diferente, já que a comutação mundial é realizada usando instruções de ramificação em vez de exceções. Ele também oferece suporte ao tratamento seguro de interrupções intercaladas de qualquer um dos mundos, independentemente do estado de segurança atual. Juntos, esses recursos fornecem chamadas de baixa latência para o mundo seguro e tratamento de interrupções responsivo. ARM fornece uma pilha de referência de código mundial seguro na forma de Trusted Firmware for M e PSA Certified.

Proteção de página sem execução

A partir do ARMv6, a arquitetura ARM suporta proteção de página sem execução, que é chamada de XN, para eXecute Never.

Extensão de endereço físico grande (LPAE)

A Large Physical Address Extension (LPAE), que estende o tamanho do endereço físico de 32 bits para 40 bits, foi adicionada à arquitetura Armv7-A em 2011.

O tamanho do endereço físico pode ser ainda maior em processadores baseados na arquitetura de 64 bits (Armv8-A). Por exemplo, são 44 bits no Cortex-A75 e no Cortex-A65AE.

Armv8-R e Armv8-M

As arquiteturas Armv8-R e Armv8-M, anunciadas após a arquitetura Armv8-A, compartilham alguns recursos com Armv8-A. No entanto, o Armv8-M não inclui nenhuma instrução AArch64 de 64 bits e o Armv8-R originalmente não incluía nenhuma instrução AArch64; essas instruções foram adicionadas ao Armv8-R posteriormente.

Armv8.1-M

A arquitetura Armv8.1-M, anunciada em fevereiro de 2019, é um aprimoramento da arquitetura Armv8-M. Ele traz novos recursos, incluindo:

- Uma nova instrução vetorial estabeleceu extensão. A extensão vetorial M-Profile (MVE), ou hélio, é para processamento de sinais e aplicações de aprendizado de máquina.

- Melhorias adicionais do conjunto de instrução para loops e ramos (Low Overhead Branch Extension).

- Instruções para suporte de ponto flutuante de meia precisão.

- Melhoria do conjunto de instruções para gestão TrustZone para unidade de ponto flutuante (FPU).

- Novo atributo de memória na unidade de proteção de memória (MPU).

- Melhorias em depurrão, incluindo Unidade de Monitoramento de Desempenho (PMU), Extensão de Depuração Não Privilegiada e foco de suporte de depuração adicional em desenvolvimentos de aplicativos de processamento de sinais.

- Confiabilidade, disponibilidade e manutenção (RAS) extensão.

Arquitetura de 64/32 bits

Armv8

Armv8-A

Anunciado em outubro de 2011, o Armv8-A (muitas vezes chamado de ARMv8, embora o Armv8-R também esteja disponível) representa uma mudança fundamental na arquitetura ARM. Ele adiciona uma arquitetura opcional de 64 bits chamada "AArch64" e o novo "A64" conjunto de instruções. AArch64 fornece compatibilidade de espaço de usuário com Armv7-A, a arquitetura de 32 bits, aqui referida como "AArch32" e o antigo conjunto de instruções de 32 bits, agora denominado "A32". O conjunto de instruções Thumb é referido como "T32" e não tem equivalente de 64 bits. Armv8-A permite que aplicativos de 32 bits sejam executados em um sistema operacional de 64 bits e que um sistema operacional de 32 bits esteja sob o controle de um hipervisor de 64 bits. A ARM anunciou seus núcleos Cortex-A53 e Cortex-A57 em 30 de outubro de 2012. A Apple foi a primeira a lançar um núcleo compatível com Armv8-A em um produto de consumo (Apple A7 no iPhone 5S). AppliedMicro, usando um FPGA, foi o primeiro a demonstrar o Armv8-A. O primeiro SoC Armv8-A da Samsung é o Exynos 5433 usado no Galaxy Note 4, que apresenta dois clusters de quatro núcleos Cortex-A57 e Cortex-A53 em uma configuração big.LITTLE; mas será executado apenas no modo AArch32.

Para AArch32 e AArch64, Armv8-A torna VFPv3/v4 e padrão SIMD (Neon) avançado. Ele também adiciona instruções de criptografia com suporte para AES, SHA-1/SHA-256 e aritmética de campo finito. AArch64 foi introduzido no Armv8-A e sua revisão subsequente. AArch64 não está incluído nas arquiteturas Armv8-R e Armv8-M de 32 bits.

Armv8-R

O suporte opcional AArch64 foi adicionado ao perfil Armv8-R, com o primeiro núcleo ARM implementando-o sendo o Cortex-R82. Ele adiciona o conjunto de instruções A64.

Armv9

Armv9-A

Anunciada em março de 2021, a arquitetura atualizada concentra-se na execução segura e na compartimentação.

Armar SystemReady

Arm SystemReady, anteriormente denominado Arm ServerReady, é um programa de certificação que ajuda a implantar sistemas operacionais e hipervisores genéricos prontos para uso em sistemas baseados em Arm, desde servidores de datacenter até dispositivos de borda industrial e IoT. Os principais blocos de construção do programa são as especificações dos requisitos mínimos de hardware e firmware nos quais os sistemas operacionais e hipervisores podem confiar. Essas especificações são:

- Arquitetura do Sistema Base (BSA) e os suplementos específicos do segmento de mercado (por exemplo, suplemento Server BSA)

- Requisitos de inicialização base (BBR) e requisitos de segurança de inicialização base (BBR)

Essas especificações são desenvolvidas em conjunto pela Arm e seus parceiros no System Architecture Advisory Committee (SystemArchAC).

Architecture Compliance Suite (ACS) são as ferramentas de teste que ajudam a verificar a conformidade dessas especificações. A Especificação de Requisitos Arm SystemReady documenta os requisitos das certificações.

Este programa foi apresentado pela Arm em 2020 no primeiro evento DevSummit. Seu antecessor Arm ServerReady foi apresentado em 2018 no evento Arm TechCon. Este programa inclui atualmente quatro bandas:

- SystemReady SR: esta banda é para servidores e estações de trabalho que suportam sistemas operacionais e hipervisores que esperam interfaces UEFI, ACPI e SMBIOS. Windows, Red Hat Enterprise Linux e VMware ESXi-Arm exigem essas interfaces enquanto outras distros Linux e BSD também podem suportar.

- SystemReady LS (LinuxBoot System): esta banda é para servidores que os hiperscalers usam para suportar sistemas operacionais Linux que esperam firmware LinuxBoot junto com as interfaces ACPI e SMBIOS.

- SistemaReady ES (Sistema Integrado): esta banda é para os dispositivos de borda industrial e IoT que suportam sistemas operacionais e hipervisores que esperam interfaces UEFI, ACPI e SMBIOS. O Windows IoT Enterprise, o Red Hat Enterprise Linux e o VMware ESXi-Arm exigem essas interfaces enquanto outras distros Linux e BSD também podem suportar.

- SystemReady IR (IoT Ready): esta banda é para os dispositivos de borda industrial e IoT que suportam sistemas operacionais que esperam interfaces UEFI e devicetree. Linux incorporado (por exemplo, Yocto) e algumas distros Linux/BSD (por exemplo, Fedora, Ubuntu, Debian e OpenSUSE) também podem suportar.

Certificado PSA

PSA Certified, anteriormente chamada de Platform Security Architecture, é uma estrutura de segurança e esquema de avaliação independente de arquitetura. O objetivo é ajudar a proteger dispositivos da Internet das Coisas (IoT) construídos em processadores System-on-a-chip (SoC). Foi introduzido para aumentar a segurança onde um ambiente de execução totalmente confiável é muito grande ou complexo.

A arquitetura foi apresentada pela Arm em 2017 no evento anual TechCon. Embora o esquema seja independente de arquitetura, ele foi implementado pela primeira vez em núcleos de processador Arm Cortex-M destinados ao uso de microcontroladores. A certificação PSA inclui modelos de ameaças e análises de segurança disponíveis gratuitamente que demonstram o processo de decisão sobre recursos de segurança em produtos IoT comuns. Ele também fornece pacotes de interface de programação de aplicativos (API) para download gratuito, especificações de arquitetura, implementações de firmware de código aberto e conjuntos de testes relacionados.

Após o desenvolvimento da estrutura de segurança da arquitetura em 2017, o esquema de garantia PSA Certified foi lançado dois anos depois na Embedded World em 2019. O PSA Certified oferece um esquema de avaliação de segurança em vários níveis para fornecedores de chips, fornecedores de sistemas operacionais e fabricantes de dispositivos IoT. A apresentação do Embedded World apresentou aos fornecedores de chips a Certificação de Nível 1. Um projeto de proteção de Nível 2 foi apresentado ao mesmo tempo. A certificação de nível 2 tornou-se um padrão utilizável em fevereiro de 2020.

A certificação foi criada pelas partes interessadas conjuntas da PSA para permitir uma abordagem de segurança desde o design para um conjunto diversificado de produtos IoT. As especificações certificadas pela PSA são independentes de implementação e arquitetura e, como resultado, podem ser aplicadas a qualquer chip, software ou dispositivo. A certificação também elimina a fragmentação da indústria para fabricantes e desenvolvedores de produtos IoT.

Suporte ao sistema operacional

Sistemas operacionais de 32 bits

Sistemas operacionais históricos

O primeiro computador pessoal de 32 bits baseado em ARM, o Acorn Archimedes, foi originalmente planejado para rodar um ambicioso sistema operacional chamado ARX. As máquinas foram fornecidas com o sistema operacional RISC, que também foi usado em sistemas posteriores baseados em ARM da Acorn e de outros fornecedores. Algumas das primeiras máquinas Acorn também eram capazes de executar uma porta Unix chamada RISC iX. (Nenhum dos dois deve ser confundido com RISC/os, uma variante Unix contemporânea para a arquitetura MIPS.)

Sistemas operacionais incorporados

A arquitetura ARM de 32 bits é suportada por um grande número de sistemas operacionais integrados e de tempo real, incluindo:

- A2

- Android

- ChibiOS/RT

- Deos

- DRYOS

- e Cos

- embriões

- FreeBSD

- FreeRTOS

- INTEGRAÇÃO

- Linux

- Micro-Controlador Sistemas Operacionais

- Mbed

- MINIX 3

- MQX

- Nucleus PLUS

- Não!

- Sistema Operacional Incorporado (OSE)

- OS-9

- Pharos

- Plano 9

- Pikeos

- QNX

- RIOT

- RTEMS

- RTXC Quadros

- SCIOPTA

- Linha de produção

- Tizentular

- T-Kernel

- VxWorks

- Compacto embutido do Windows

- Núcleo de IoT do Windows 10

- Zephyr

Sistemas operacionais de dispositivos móveis

A arquitetura ARM de 32 bits é o principal ambiente de hardware para a maioria dos sistemas operacionais de dispositivos móveis, como:

- Android

- BlackBerry OS/BlackBerry 10

- ChromeOS

- Mobian

- Peixe-marinho

- pós-venda

- Tizen

- Toque em Ubuntu

- WebOS

Anteriormente, mas agora descontinuado:

- Bada.

- Firefox OS

- MeeGo

- Newton OS

- iOS 10 e mais cedo

- Symbian

- Windows 10 móvel

- NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT1 NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT NT

- Telefone do Windows

- Windows Mobile

Sistemas operacionais para desktops e servidores

A arquitetura ARM de 32 bits é suportada pelo sistema operacional RISC e por vários sistemas operacionais do tipo Unix, incluindo:

- FreeBSD

- NetBSD

- OpenBSD

- OpenSolaris

- vários distribuições Linux, como:

- Debian

- Armbian

- Gento!

- Ubuntu

- Raspberry Pi OS (anteriormente Raspbian)

- Slackware

Sistemas operacionais de 64 bits

Sistemas operacionais incorporados

- INTEGRAÇÃO

- OSE

- SCIOPTA

- SeL4

- Pharos

- FreeRTOS

- QNX

- VxWorks

- Zephyr

Sistemas operacionais de dispositivos móveis

- Android suporta Armv8-A no Android Lollipop (5.0) e mais tarde.

- O iOS suporta o Armv8-A no iOS 7 e mais tarde em Apple SoCs de 64 bits. O iOS 11 e posterior, e o iPadOS, suportam apenas processadores e aplicações de ARM de 64 bits.

- Mobian

- PostmarketOS

- Arch Linux ARM

- Manjaro

Sistemas operacionais para desktops e servidores

- O suporte para Armv8-A foi mesclado na versão 3.7 do kernel do Linux no final de 2012. Armv8-A é suportado por uma série de distribuições Linux, tais como:

- Debian

- Armbian

- Alpine Linux

- Ubuntu

- Fedora

- Abertura

- SUSE Linux Enterprise

- RH

- Raspberry Pi OS (anteriormente Raspbian)

- O suporte para Armv8-A foi fundido no FreeBSD no final de 2014.

- OpenBSD tem suporte Armv8 a partir de 2023.

- O NetBSD tem suporte ao Armv8 desde o início de 2018.

- Windows - Windows 10 é executado 32-bit "x86 e 32-bit aplicações ARM", bem como aplicações nativas de desktop ARM64; Windows 11 também. O suporte para aplicativos ARM de 64 bits na Microsoft Store está disponível desde novembro de 2018.

- O macOS tem suporte ao ARM desde o final de 2020; a primeira versão para suportar o ARM é o macOS Big Sur. Rosetta 2 adiciona suporte para aplicações x86-64, mas não virtualização de plataformas de computadores x86-64.

Portagem para sistemas operacionais ARM de 32 ou 64 bits

Aplicativos Windows recompilados para ARM e vinculados ao Winelib, do projeto Wine, podem ser executados em ARM de 32 ou 64 bits no Linux, FreeBSD ou outros sistemas operacionais compatíveis. Binários x86, por ex. quando não compilados especialmente para ARM, foram demonstrados no ARM usando QEMU com Wine (no Linux e mais), mas não funcionam em velocidade total ou com a mesma capacidade do Winelib.

Contenido relacionado

Fax

Álgebra elementar

KornShellGenericName