DEC Alfa

Alpha (nome original Alpha AXP) é uma arquitetura de conjunto de instruções (ISA) de computador com conjunto de instruções reduzido de 64 bits (RISC) desenvolvida pela Digital Equipment Corporation (DEC). O Alpha foi projetado para substituir os computadores com conjunto de instruções complexas VAX de 32 bits (CISC) e para ser um processador RISC altamente competitivo para estações de trabalho Unix e mercados semelhantes.

O Alpha é implementado em uma série de microprocessadores originalmente desenvolvidos e fabricados pela DEC. Esses microprocessadores são usados com mais destaque em uma variedade de estações de trabalho e servidores DEC, que eventualmente formaram a base para quase toda a sua linha de escala média a alta. Vários fornecedores terceirizados também produziram sistemas Alpha, incluindo placas-mãe de fator de forma de PC.

Sistemas operacionais que suportam Alpha incluem OpenVMS (anteriormente denominado OpenVMS AXP), Tru64 UNIX (anteriormente denominado DEC OSF/1 AXP e Digital UNIX), Windows NT (descontinuado após NT 4.0; e pré-lançamento do Windows 2000 RC2), Linux (Debian, SUSE, Gentoo e Red Hat), BSD UNIX (NetBSD, OpenBSD e FreeBSD até 6.x), Plan 9 da Bell Labs e o kernel L4Ka::Pistachio. Uma porta de Ultrix para Alpha foi realizada durante o desenvolvimento inicial da arquitetura Alpha, mas nunca foi lançada como um produto.

A arquitetura Alpha foi vendida, junto com a maior parte do DEC, para a Compaq em 1998. A Compaq, já um cliente Intel x86, anunciou que eliminaria gradualmente o Alpha em favor da futura arquitetura Hewlett-Packard/Intel Itanium e vendeu toda a propriedade intelectual da Alpha para a Intel, em 2001, efetivamente matando o produto. A Hewlett-Packard comprou a Compaq em 2002, continuando o desenvolvimento da linha de produtos existente até 2004 e vendendo sistemas baseados em Alpha, principalmente para a base de clientes existente, até abril de 2007.

História

PRISM

O Alpha surgiu de um projeto RISC anterior chamado Parallel Reduced Instruction Set Machine (PRISM), produto de vários projetos anteriores. O PRISM foi concebido para ser um projeto flexível, suportando aplicativos do tipo Unix e o software VAX/VMS existente da Digital, após uma pequena conversão. Um novo sistema operacional chamado MICA suportaria as interfaces ULTRIX e VAX/VMS em um kernel comum, permitindo que o software para ambas as plataformas fosse facilmente portado para a arquitetura PRISM.

Iniciado em 1985, o design do PRISM foi continuamente alterado durante seu desenvolvimento em resposta às mudanças no mercado de computadores, levando a longos atrasos em sua introdução. Não foi até o verão de 1987 que foi decidido que seria um projeto de 64 bits, entre os primeiros projetos desse tipo em formato de microprocessador. Em outubro de 1987, a Sun Microsystems apresentou o Sun-4, sua primeira estação de trabalho usando seu novo processador SPARC. O Sun-4 roda cerca de três a quatro vezes mais rápido que seus designs mais recentes do Sun-3 usando o Motorola 68020 e qualquer oferta Unix da DEC. Os planos mudaram novamente; O PRISM foi realinhado mais uma vez como uma parte de 32 bits e voltado diretamente para o mercado Unix. Isso atrasou ainda mais o projeto.

Tendo visto a data de entrega do PRISM continuar atrasada e enfrentando a possibilidade de mais atrasos, uma equipe no escritório de Palo Alto decidiu projetar sua própria estação de trabalho usando outro processador RISC. Após a devida diligência, eles selecionaram o MIPS R2000 e construíram uma estação de trabalho funcionando executando o Ultrix em um período de 90 dias. Isso desencadeou um acalorado debate dentro da empresa, que chegou ao auge em uma reunião administrativa em julho de 1988. O PRISM parecia ser mais rápido que o R2000, mas as máquinas R2000 poderiam estar no mercado em janeiro de 1989, um ano antes do PRISM. Quando esta proposta foi aceita, uma das duas funções originais do PRISM desapareceu. A decisão de fazer um VMS PRISM já havia terminado neste ponto, então não havia função restante. O PRISM foi cancelado na reunião.

RISCy VAX

Quando a reunião terminou, Bob Supnik foi abordado por Ken Olsen, que afirmou que os chips RISC pareciam ser uma ameaça futura à sua linha VAX. Ele pediu a Supnik que considerasse o que poderia ser feito com o VAX para mantê-lo competitivo com os futuros sistemas RISC.

Isso levou à formação do "RISCy VAX" equipe. Eles inicialmente consideraram três conceitos. Uma era uma versão reduzida da arquitetura do conjunto de instruções VAX (ISA) que seria executada em um sistema semelhante ao RISC e deixaria as instruções VAX mais complexas para as sub-rotinas do sistema. Outro conceito era um sistema RISC puro que traduziria o código VAX existente em seu próprio ISA on-the-fly e o armazenaria em um cache da CPU. Por fim, ainda havia a possibilidade de um processador CISC muito mais rápido executando o VAX ISA completo. Infelizmente, todas essas abordagens introduziram sobrecarga e não seriam competitivas com uma máquina RISC pura executando código RISC nativo.

O grupo então considerou sistemas híbridos que combinavam uma de suas soluções existentes de um chip VAX e um chip RISC como um coprocessador usado para necessidades de alto desempenho. Esses estudos sugeriram que o sistema seria inevitavelmente prejudicado pela parte de baixo desempenho e não ofereceria nenhuma vantagem convincente. Foi nesse ponto que Nancy Kronenberg apontou que as pessoas executavam o VMS, não o VAX, e que o VMS tinha apenas algumas dependências de hardware com base em sua modelagem de interrupções e paginação de memória. Parecia não haver nenhuma razão convincente para que o VMS não pudesse ser portado para um chip RISC, desde que esses pequenos pedaços do modelo fossem preservados. Trabalhos adicionais sobre esse conceito sugeriram que essa era uma abordagem viável.

Supnik levou o relatório resultante à Força-Tarefa de Estratégia em fevereiro de 1989. Duas questões foram levantadas: o design RISC resultante também poderia ser um líder de desempenho no mercado Unix e a máquina deveria ser um padrão aberto? E com isso, foi tomada a decisão de adotar a arquitetura PRISM com as devidas modificações. Isso se tornou o "EVAX" conceito, uma continuação da implementação bem-sucedida do CMOS CVAX. Quando a administração aceitou as descobertas, eles decidiram dar ao projeto um nome mais neutro, removendo "VAX", eventualmente estabelecendo-se como Alpha. Logo depois, começaram os trabalhos em uma porta de VMS para a nova arquitetura.

Alfa

O novo design usa a maioria dos conceitos básicos do PRISM, mas foi reajustado para permitir que os programas VMS e VMS sejam executados em velocidade razoável sem nenhuma conversão. Os principais arquitetos do conjunto de instruções Alpha foram Richard L. Sites e Richard T. Witek. O Epicode do PRISM foi desenvolvido no Alpha's PALcode, fornecendo uma interface abstrata para recursos específicos de implementação de plataforma e processador.

A principal contribuição do Alpha para a indústria de microprocessadores, e o principal motivo de seu desempenho, não é tanto a arquitetura, mas sim sua implementação. Naquela época (como é agora), a indústria de microchips era dominada por ferramentas automatizadas de design e layout. Os projetistas de chips da Digital continuaram buscando projetos de circuitos manuais sofisticados para lidar com a complexa arquitetura VAX. Os chips Alpha mostram que o projeto de circuito manual aplicado a uma arquitetura mais simples e limpa permite frequências operacionais muito mais altas do que aquelas possíveis com os sistemas de projeto mais automatizados. Esses chips causaram um renascimento do design de circuitos personalizados dentro da comunidade de design de microprocessadores.

Originalmente, os processadores Alpha foram designados como a série DECchip 21x64, com "DECchip" substituído em meados da década de 1990 por "Alpha". Os dois primeiros dígitos, "21" significa o século 21, e os dois últimos dígitos, "64" significa 64 bits. O Alpha foi projetado como 64 bits desde o início e não há versão de 32 bits. O dígito do meio corresponde à geração da arquitetura Alpha. Internamente, os processadores Alpha também foram identificados por números EV, EV significando oficialmente "Extended VAX" mas tendo um significado humorístico alternativo de "Electric Vlasic", homenageando o experimento Electric Pickle no Western Research Lab.

Em maio de 1997, a DEC processou a Intel por supostamente infringir suas patentes Alpha ao projetar os chips originais Pentium, Pentium Pro e Pentium II. Como parte de um acordo, grande parte dos negócios de design e fabricação de chips da DEC foi vendida para a Intel. Isso incluiu a implementação StrongARM da DEC da arquitetura de computador ARM, que a Intel comercializou como os processadores XScale comumente usados em Pocket PCs. O núcleo da Digital Semiconductor, o grupo de microprocessadores Alpha, permaneceu com a DEC, enquanto os prédios de escritórios associados foram para a Intel como parte da fábrica Hudson.

Modelos aprimorados

As primeiras gerações de chips Alpha foram algumas das mais inovadoras de seu tempo.

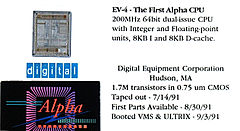

- A primeira versão, a Alfa 21064 ou EV4, é o primeiro microprocessador CMOS cuja frequência operacional rivalizou com minicomputadores ECL de maior potência e mainframes.

- O segundo, 21164 ou EV5, é o primeiro microprocessador a colocar um grande cache secundário no chip.

- O terceiro, 2164 ou EV6, é o primeiro microprocessador a combinar a alta frequência operacional e a mais complicada microarquitetura de execução fora de ordem.

- O 213 ou EV7 é o primeiro processador de alto desempenho a ter um controlador de memória no chip.

- O não produzido 21464 ou EV8 teria sido o primeiro a incluir multithreading simultâneo, mas esta versão foi cancelada após a venda de DEC para Compaq. O Tarantula projeto de pesquisa, que provavelmente teria sido chamado EV9, teria sido o primeiro processador Alpha a apresentar uma unidade de processador vetorial.

Um relatório persistente atribuído a membros da DEC sugere que a escolha da tag AXP para o processador foi feita pelo departamento jurídico da DEC, que ainda estava sofrendo com o fiasco da marca registrada VAX. Após uma longa pesquisa, a tag "AXP" foi encontrado totalmente desimpedido. Dentro da indústria de computadores, começou uma piada de que o acrônimo AXP significava "Quase exatamente PRISM".

Princípios de design

A arquitetura Alpha foi projetada para ser um projeto de alto desempenho. A Digital pretendia que a arquitetura suportasse um aumento de mil vezes no desempenho ao longo de vinte e cinco anos. Para garantir isso, qualquer recurso de arquitetura que impedisse a emissão de várias instruções, taxa de clock ou multiprocessamento foi removido. Como resultado, o Alpha não possui:

- Slots de atraso do ramo

- Instruções supressas

- Instruções de carga ou armazenamento de byte (mais tarde adicionado com as extensões do Byte Word (BWX)))

Códigos de condição

O Alpha não possui códigos de condição para instruções inteiras para remover um possível gargalo no registro de status de condição. As instruções que resultam em um estouro, como adicionar dois números cujo resultado não cabe em 64 bits, escrevem os 32 ou 64 bits menos significativos no registrador de destino. O transporte é gerado executando uma comparação sem sinal no resultado com qualquer um dos operandos para ver se o resultado é menor do que qualquer um dos operandos. Se o teste for verdadeiro, o valor um é escrito no bit menos significativo do registrador de destino para indicar a condição.

Registros

A arquitetura define um conjunto de 32 registradores inteiros e um conjunto de 32 registradores de ponto flutuante, além de um contador de programa, dois registradores de bloqueio e um registrador de controle de ponto flutuante (FPCR). Também define registradores que eram opcionais, implementados apenas se a implementação os exigisse. Por fim, são definidos os registradores para PALcode.

Os registradores inteiros são indicados por R0 a R31 e os registradores de ponto flutuante são indicados por F0 a F31. Os registros R31 e F31 são conectados a zero e as gravações nesses registros por instruções são ignoradas. A Digital considerou o uso de um arquivo de registro combinado, mas um arquivo de registro dividido foi considerado melhor, pois permite que implementações de dois chips tenham um arquivo de registro localizado em cada chip e implementações somente de número inteiro para omitir o arquivo de registro de ponto flutuante contendo o registradores de ponto flutuante. Um arquivo de registro dividido também foi determinado como mais adequado para emissão de várias instruções devido ao número reduzido de portas de leitura e gravação. Também foi considerado o número de registros por arquivo de registro, sendo 32 e 64 contendores. A Digital concluiu que 32 registros era mais adequado, pois exigia menos espaço de matriz, o que melhora as frequências de clock. Esse número de registradores não foi considerado um grande problema em relação ao desempenho e ao crescimento futuro, pois trinta e dois registradores poderiam suportar pelo menos a emissão de instruções de oito vias.

O contador de programa é um registrador de 64 bits que contém um endereço de byte virtual alinhado por palavra longa, ou seja, os dois bits inferiores do contador de programa são sempre zero. O PC é incrementado em quatro para o endereço da próxima instrução quando uma instrução é decodificada. Um sinalizador de bloqueio e um registro de endereço físico bloqueado são usados pelas instruções load-locked e store-condicional para suporte a multiprocessador. O registro de controle de ponto flutuante (FPCR) é um registro de 64 bits definido pela arquitetura destinada ao uso por implementações Alpha com hardware de ponto flutuante compatível com IEEE 754.

Tipos de dados

Na arquitetura Alpha, um byte é definido como um dado de 8 bits (octeto), uma palavra como um dado de 16 bits, uma palavra longa como um dado de 32 bits, uma quadword como um dado de 64 bits e uma octaword como um dado de 128 bits.

A arquitetura Alpha originalmente definiu seis tipos de dados:

- Quadword (64-bit) inteiro

- Longword (32-bit) inteiro

- IEEE T-floating-point (precisão dupla, 64-bit)

- IEEE S-floating-point (precisão única, 32-bit)

Para manter um nível de compatibilidade com o VAX, a arquitetura de 32 bits que precedeu o Alpha, dois outros tipos de dados de ponto flutuante foram incluídos:

- VAX G-floating point (precisão dupla, 64-bit)

- VAX F-floating point (precisão única, 32-bit)

- VAX O ponto de flutuação H (precisão do portão, 128 bits) não foi suportado, mas outra opção de ponto flutuante de 128 bits, ponto de flutuação X, está disponível em Alpha, mas não VAX.

H e X foram descritos como semelhantes, mas não idênticos. Emulação de software para H-floating está disponível a partir de DEC, como é um conversor de nível de código-fonte chamado DECmigrate.

Memória

O Alpha tem um espaço de endereço virtual linear de 64 bits sem segmentação de memória. As implementações podem implementar um espaço de endereço virtual menor com um tamanho mínimo de 43 bits. Embora os bits não utilizados não tenham sido implementados em hardware como TLBs, a arquitetura exigia implementações para verificar se eles são zero para garantir a compatibilidade de software com implementações com um espaço de endereço virtual maior (ou completo).

Formatos de instrução

O Alpha ISA tem um comprimento de instrução fixo de 32 bits. Possui seis formatos de instrução.

| 31 | 30 | 29 de Março | 28 | 27 | 26 | 25 | 24. | 23 | 22 | 21 | 20. | 19 | 18. | 17. | 16. | 15 | 14 | 13 | 12 | 11 | 10. | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | Tipo |

| Código de acesso | Ra | Rb | Sem uso | 0 | Função | Rc | Integer opera | |||||||||||||||||||||||||

| Código de acesso | Ra | Literal | 1 | Função | Rc | Integer opera, literal | ||||||||||||||||||||||||||

| Código de acesso | Ra | Rb | Função | Rc | Operação de ponto flutuante | |||||||||||||||||||||||||||

| Código de acesso | Ra | Rb | Deslocamento | Formato de memória | ||||||||||||||||||||||||||||

| Código de acesso | Ra | Deslocamento | Formato de ramo | |||||||||||||||||||||||||||||

| Código de acesso | Função | CALL_PAL formato | ||||||||||||||||||||||||||||||

O formato de operação de inteiro é usado por instruções de inteiro. Ele contém um campo opcode de 6 bits, seguido pelo campo Ra, que especifica o registrador que contém o primeiro operando e o campo Rb, que especifica o registrador que contém o segundo operando. Em seguida, há um campo de 3 bits que não é usado e é reservado. Um campo de 1 bit contém um "0", que distingue esse formato do formato literal inteiro. Segue-se um campo de função de 7 bits, que é usado em conjunto com o opcode para especificar uma operação. O último campo é o campo Rc, que especifica o registrador no qual o resultado de uma computação deve ser escrito. Os campos de registro são todos de 5 bits, necessários para endereçar 32 localizações únicas, os 32 registros inteiros.

O formato literal inteiro é usado por instruções inteiras que usam um literal como um dos operandos. O formato é o mesmo que o formato de operação de número inteiro, exceto pela substituição do campo Rb de 5 bits e os 3 bits de espaço não utilizado por um campo literal de 8 bits que é estendido em zero para um operando de 64 bits.

O formato de operação de ponto flutuante é usado por instruções de ponto flutuante. É semelhante ao formato de operação de número inteiro, mas tem um campo de função de 11 bits possibilitado pelo uso de bits literais e não utilizados que são reservados no formato de operação de número inteiro.

O formato de memória é usado principalmente por instruções de carregamento e armazenamento. Ele possui um campo opcode de 6 bits, um campo Ra de 5 bits, um campo Rb de 5 bits e um campo de deslocamento de 16 bits.

As instruções de ramificação têm um campo de opcode de 6 bits, um campo Ra de 5 bits e um campo de deslocamento de 21 bits. O campo Ra especifica um registro a ser testado por uma instrução de ramificação condicional e, se a condição for atendida, o contador do programa é atualizado adicionando o conteúdo do campo de deslocamento com o contador do programa. O campo de deslocamento contém um inteiro com sinal e, se o valor do inteiro for positivo, se a ramificação for tomada, o contador do programa será incrementado. Se o valor do inteiro for negativo, o contador do programa será decrementado se a ramificação for tomada. O alcance de uma ramificação, portanto, é ±1 instruções Mi, ou ±4 MiB. A Alpha Architecture foi projetada com uma grande variedade como parte do objetivo da arquitetura voltada para o futuro.

O formato CALL_PAL é usado pela instrução CALL_PAL, que é usada para chamar sub-rotinas PALcode. O formato retém o campo opcode, mas substitui os outros por um campo de função de 26 bits, que contém um inteiro especificando uma sub-rotina PAL.

Conjunto de instruções

Instruções de controle

As instruções de controle consistem em desvios condicionais e incondicionais e saltos. As instruções de desvio condicional e incondicional usam o formato de instrução de desvio, enquanto as instruções de salto usam o formato de instrução de memória.

As ramificações condicionais testam se o bit menos significativo de um registrador está definido ou limpo, ou comparam um registrador como uma quadword com sinal a zero, e ramificam se a condição especificada for verdadeira. As condições disponíveis para comparar um registrador com zero são igualdade, desigualdade, menor que, menor que ou igual a, maior que ou igual a e maior que. O novo endereço é calculado pelo alinhamento de palavras longas e o sinal estendendo o deslocamento de 21 bits e adicionando-o ao endereço da instrução seguinte ao desvio condicional.

Os desvios incondicionais atualizam o contador do programa com um novo endereço calculado da mesma forma que os desvios condicionais. Eles também salvam o endereço da instrução após o desvio incondicional em um registrador. Existem duas dessas instruções e elas diferem apenas nas dicas fornecidas para o hardware de previsão de desvio.

Existem quatro instruções de salto. Todos eles executam a mesma operação, salvando o endereço da instrução seguinte ao salto e fornecendo ao contador de programa um novo endereço de um registrador. Eles diferem nas dicas fornecidas ao hardware de previsão de ramificação. O campo de deslocamento não utilizado é usado para essa finalidade.

Aritmética inteira

As instruções aritméticas inteiras executam adição, multiplicação e subtração em longwords e quadwords; e comparação em quadwords. Não há instrução(ões) para divisão, pois os arquitetos consideraram a implementação da divisão em hardware adversa à simplicidade. Além das instruções padrão de adição e subtração, existem versões em escala. Essas versões deslocam o segundo operando para a esquerda em dois ou três bits antes de adicionar ou subtrair. As instruções Multiply Longword e Multiply Quadword escrevem os 32 ou 64 bits menos significativos de um resultado de 64 ou 128 bits no registrador de destino, respectivamente. Uma vez que é útil obter a metade mais significativa, a instrução Unsigned Multiply Quadword High (UMULH) é fornecida. UMULH é usado para implementar algoritmos de divisão e aritmética de precisão múltipla. O conceito de uma instrução separada para multiplicação que retorna a metade mais significativa de um resultado foi retirado do PRISM.

As instruções que operam em longwords ignoram a metade mais significativa do registrador e o resultado de 32 bits é estendido em sinal antes de ser escrito no registrador de destino. Por padrão, as instruções de adição, multiplicação e subtração, com exceção de UMULH e versões em escala de adição e subtração, não interceptam em estouro. Quando essa funcionalidade é necessária, são fornecidas versões dessas instruções que executam a detecção de estouro e interceptam o estouro.

As instruções de comparação comparam dois registradores ou um registrador e um literal e escrevem '1' para o registrador de destino se a condição especificada for verdadeira ou '0' se não. As condições são igualdade, desigualdade, menor ou igual a e menor que. Com exceção das instruções que especificam as duas condições anteriores, existem versões que realizam comparações assinadas e não assinadas.

As instruções aritméticas inteiras usam os formatos de instrução de operação inteira.

Lógica e mudança

As instruções lógicas consistem naquelas para executar operações lógicas bit a bit e movimentos condicionais nos registradores inteiros. As instruções lógicas bit a bit executam AND, NAND, NOR, OR, XNOR e XOR entre dois registradores ou um registrador e literal. As instruções de movimentação condicional testam um registrador como uma quadword assinada para zero e movem se a condição especificada for verdadeira. As condições especificadas são igualdade, desigualdade, menor ou igual a, menor que, maior ou igual a e maior que. As instruções de deslocamento executam deslocamento aritmético à direita e deslocamentos lógicos à esquerda e à direita. A quantidade de deslocamento é dada por um registrador ou literal. As instruções lógicas e de deslocamento usam os formatos de instrução de operação inteira.

Extensões

Extensões de palavra de byte (BWX)

Alfas posteriores incluem extensões de palavra de byte, um conjunto de instruções para manipular tipos de dados de 8 e 16 bits. Essas instruções foram introduzidas pela primeira vez no microprocessador 21164A (EV56) e estão presentes em todas as implementações subsequentes. Essas instruções executam operações que anteriormente exigiam várias instruções para serem implementadas, o que melhora a densidade do código e o desempenho de determinados aplicativos. O BWX também facilita a emulação de código de máquina x86 e a gravação de drivers de dispositivo.

| Mnemónica | Instrução |

|---|---|

LDBU | Carga Zero-Extended Byte da Memória para Registar |

LDWU | Carregar Zero-Extended Word de Memória para Registar |

SEXTB | Adicionar ao cesto |

SEXTW | Adicionar ao cesto |

STB | Armazenar Byte de registro para memória |

STW | Armazenar o Word de Registro para Memória |

Instruções de vídeo em movimento (MVI)

Motion Video Instructions (MVI) era uma extensão do conjunto de instruções para o Alpha ISA que adicionava instruções para operações de instrução única e dados múltiplos (SIMD). As implementações Alpha que implementam MVI, em ordem cronológica, são Alpha 21164PC (PCA56 e PCA57), Alpha 21264 (EV6) e Alpha 21364 (EV7). Ao contrário da maioria dos outros conjuntos de instruções SIMD do mesmo período, como MIPS' MDMX ou SPARC's Visual Instruction Set, mas como PA-RISC's Multimedia Acceleration eXtensions (MAX-1, MAX-2), MVI era um conjunto de instruções simples composto de algumas instruções que operam em tipos de dados inteiros armazenados em registradores inteiros existentes.

A simplicidade do MVI se deve a dois motivos. Em primeiro lugar, a Digital havia determinado que o Alpha 21164 já era capaz de realizar a decodificação de DVD por meio de software, não exigindo, portanto, provisões de hardware para esse fim, mas era ineficiente na codificação MPEG-2. A segunda razão é a necessidade de manter os tempos de ciclo rápidos das implementações. Adicionar muitas instruções teria complicado e ampliado a lógica de decodificação da instrução, reduzindo a frequência de clock de uma implementação.

MVI consiste em 13 instruções:

| Mnemónica | Instrução |

|---|---|

MAXSB8 | Vector sinalizado Byte Máximo |

MAXSW4 | Vector Signed Word Máximo |

MAXUB8 | Vector Unsigned Byte Máximo |

MAXUW4 | Vector Unsigned Word Máximo |

MINSB8 | Vetor assinado Byte Mínimo |

MINSW4 | Vector Signed Word Mínimo |

MINUB8 | Vector Unsigned Byte Mínimo |

MINUW4 | Vector Unsigned Word Mínimo |

PERR | Erro do Pixel |

PKLB | Pacote Longwords para Bytes |

PKWB | Pacote de palavras para Bytes |

UNPKBL | Unpack Bytes to Longwords |

UNPKBW | Unpack Bytes to Words |

Extensões de ponto flutuante (FIX)

As extensões de ponto flutuante (FIX) são uma extensão da arquitetura Alpha. Ele apresenta nove instruções para raiz quadrada de ponto flutuante e para transferência de dados de e para registradores inteiros e registradores de ponto flutuante. O Alpha 21264 (EV6) é o primeiro microprocessador a implementar essas instruções.

| Mnemónica | Instrução |

|---|---|

FTOIS | Ponto flutuante para Integer Register Mover, S_floating |

FTOIT | Ponto flutuante para Integer Register Move, T_floating |

ITOFF | Integer para Floating-point Register Move, F_floating |

ITOFS | Integer para Floating-point Register Move, S_floating |

ITOFT | Integer para Floating-point Register Move, T_floating |

SQRTF | raiz quadrada F_floating |

SQRTG | Raiz quadrada G_floating |

SQRTS | raiz quadrada S_floating |

SQRTT | raiz quadrada T_floating |

Contagem de Extensões (CIX)

Count Extensions (CIX) é uma extensão da arquitetura que introduz três instruções para contagem de bits. Essas instruções são categorizadas como instruções aritméticas inteiras. Eles foram implementados pela primeira vez no Alpha 21264A (EV67).

| Mnemónica | Instrução |

|---|---|

CTLZ | Contagem Leading Zero |

CTPOP | População de contagem |

CTTZ | Count Trailing Zero |

Implementações

Na época de seu anúncio, Alpha foi anunciado como uma arquitetura para os próximos 25 anos. Embora isso não fosse acontecer, Alpha teve uma vida razoavelmente longa. A primeira versão, a Alpha 21064 (também chamada de EV4) foi lançada em novembro de 1992 rodando em até 192 MHz; um leve encolhimento da matriz (o EV4S, encolhido de 0,75 µm para 0,675 µm) funcionou a 200 MHz alguns meses depois. O processador de 64 bits era um projeto superpipelined e superescalar, como outros projetos RISC, mas, no entanto, superou todos eles e a DEC o divulgou como o processador mais rápido do mundo. A atenção cuidadosa ao design do circuito, uma marca registrada da equipe de design do Hudson, como um enorme circuito de relógio centralizado, permitiu que eles executassem a CPU em velocidades mais altas, embora a microarquitetura fosse bastante semelhante a outros chips RISC. Em comparação, o Intel Pentium mais barato rodava a 66 MHz quando foi lançado na primavera seguinte.

O Alpha 21164 ou EV5 tornou-se disponível em 1995 em frequências de processador de até 333 MHz. Em julho de 1996, a velocidade da linha aumentou para 500 MHz, em março de 1998 para 666 MHz. Também em 1998, o Alpha 21264 (EV6) foi lançado em 450 MHz, atingindo eventualmente (em 2001 com o 21264C/EV68CB) 1,25 GHz. Em 2003, foi lançado o Alpha 21364 ou EV7 Marvel, essencialmente um núcleo EV68 com quatro links de comunicação entre processadores de 1,6 GB/s para melhorar desempenho do sistema multiprocessador, rodando a 1 ou 1,15 GHz.

Em 1996, a produção dos chips Alpha foi licenciada para a Samsung Electronics Company. Após a compra da Digital pela Compaq, a maioria dos produtos Alpha foi colocada na API NetWorks, Inc. (anteriormente Alpha Processor Inc.), uma empresa privada financiada pela Samsung e pela Compaq. Em outubro de 2001, a Microway tornou-se a fornecedora exclusiva de vendas e serviços da API Networks' Linha de produtos baseada em alfa.

Em 25 de junho de 2001, a Compaq anunciou que o Alpha seria descontinuado em 2004 em favor do Itanium da Intel, cancelou o chip EV8 planejado e vendeu toda a propriedade intelectual do Alpha para a Intel. A Hewlett-Packard fundiu-se com a Compaq em 2002; A HP anunciou que o desenvolvimento da série Alpha continuaria por mais alguns anos, incluindo o lançamento de uma variante EV7 de 1,3 GHz chamada EV7z. Esta seria a iteração final do Alpha, o EV79 de 0,13 µm também sendo cancelado.

OAlpha também é implementado no Piranha, um protótipo de pesquisa desenvolvido pelos grupos de pesquisa corporativa e desenvolvimento de hardware contínuo da Compaq no Western Research Laboratory e no Systems Research Center. Piranha é um design multicore para cargas de trabalho de processamento de transações que contém oito núcleos simples. Foi descrito no 27º Simpósio Internacional Anual de Arquitetura de Computadores em junho de 2000.

Histórico do modelo

| Model | Model number | Year | Frequency [MHz] | Process [µm] | Transistors [millions] | Die size [mm2] | IO pins | Power [W] | Voltage | Dcache [KB] | Icache [KB] | Scache | Bcache | ISA | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| EV4 | 21064 | 1992 | 100–200 | 0.75 | 1.68 | 234 | 290 | 30 | 3.3 | 8 | 8 | – | 128 KB–16 MB | ||

| EV4S | 21064 | 1993 | 100–200 | 0.675 | 1.68 | 186 | 290 | 27 | 3.3 | 8 | 8 | – | 128 KB–16 MB | ||

| EV45 | 21064A | 1994 | 200–300 | 0.5 | 2.85 | 164 | 33 | 3.3 | 16 | 16 | – | 256 KB–16 MB | |||

| LCA4 | 21066 | 1993 | 100–166 | 0.675 | 1.75 | 209 | 21 | 3.3 | 8 | 8 | – | ||||

| LCA4 | 21068 | 1994 | 66 | 0.675 | 1.75 | 209 | 9 | 3.3 | 8 | 8 | – | ||||

| LCA45 | 21066A | 1994 | 100–266 | 0.5 | 1.8 | 161 | 23 | 3.3 | 8 | 8 | – | ||||

| LCA45 | 21068A | 1994 | 100 | 0.5 | 1.8 | 161 | 3.3 | 8 | 8 | – | |||||

| EV5 | 21164 | 1995 | 266–500 | 0.5 | 9.3 | 299 | 296 | 56 | 3.3/2.5 | 8 | 8 | 96 KB | Up to 64 MB | R | |

| EV56 | 21164A | 1996 | 366–666 | 0.35 | 9.66 | 209 | 31–55 | 3.3/2.5 | 8 | 8 | 96 KB | Up to 64 MB | R,B | ||

| PCA56 | 21164PC | 1997 | 400–533 | 0.35 | 3.5 | 141 | 264 | 26–35 | 3.3/2.5 | 8 | 16 | – | 512 KB–4 MB | R,B,M | |

| PCA57 | 21164PC | 600–666 | 0.28 | 5.7 | 101 | 283 | 18–23 | 2.5/2.0 | 16 | 32 | – | 512 KB–4 MB | R,B,M | ||

| EV6 | 21264 | 1998 | 450–600 | 0.35 | 15.2 | 314 | 389 | 73 | 2.0 | 64 | 64 | – | 2–8 MB | R,B,M,F | |

| EV67 | 21264A | 1999 | 600–750 | 0.25 | 15.2 | 210 | 389 | 2.0 | 64 | 64 | – | 2–8 MB | R,B,M,F,C | ||

| EV68AL | 21264B | 2001 | 800–833 | 0.18 | 15.2 | 125 | 1.7 | 64 | 64 | – | 2–8 MB | R,B,M,F,C,T | |||

| EV68CB | 21264C | 2001 | 1000–1250 | 0.18 | 15.2 | 125 | 65–75 | 1.65 | 64 | 64 | – | 2–8 MB | R,B,M,F,C,T | ||

| EV68CX | 21264D | 1.65 | 64 | 64 | – | 2–8 MB | R,B,M,F,C,T | ||||||||

| EV7 | 21364 | 2003 | 1000–1150 | 0.18 | 130 | 397 | 125 | 1.5 | 64 | 64 | 1.75 MB | – | R,B,M,F,C,T | ||

| EV7z | 21364 | 2004 | 1300 | 0.18 | 130 | 397 | 125 | 1.5 | 64 | 64 | 1.75 MB | – | R,B,M,F,C,T | ||

| Cancelled | |||||||||||||||

| EV78/EV79 | 21364A | Slated for 2004 | 1700 | 0.13 | 152 | 300 | 120 | 1.2 | 64 | 64 | 1.75 MB | – | R,B,M,F,C,T | ||

| EV8 | 21464 | Slated for 2003 | 1200–2000 | 0.125 | 250 | 420 | 1800 | ?? | 1.2 | 64 | 64 | 3 MB | – | R,B,M,F,C,T | |

- Extensões ISA

- R – Suporte de hardware para arredondamento para infinito e infinidade negativa.

- B – BWX, o "Byte/Word Extension", adicionando instruções para permitir operações de 8 e 16 bits da memória e I/O

- M – MVI, instruções "multimedia"

- F – FIX, instruções para mover dados entre inteiros e registros de ponto flutuante e para raiz quadrada

- C – CIX, instruções para contar e encontrar bits

- T – suporte para prefetch com intenção de modificar para melhorar o desempenho da primeira tentativa de adquirir um bloqueio

Desempenho

Para ilustrar o desempenho comparativo dos sistemas baseados em Alpha, alguns números de desempenho da Standard Performance Evaluation Corporation (SPEC) (SPECint95, SPECfp95) estão listados abaixo. Observe que os resultados do SPEC afirmam relatar o desempenho medido de todo um sistema de computador (CPU, barramento, memória, otimizador de compilador), não apenas da CPU. Observe também que o benchmark e a escala mudaram de 1992 a 1995. No entanto, os números dão uma impressão aproximada do desempenho da arquitetura Alpha (64 bits), em comparação com as ofertas contemporâneas baseadas em HP (64 bits) e Intel (32 bits). Talvez a tendência mais óbvia seja que, embora a Intel sempre pudesse chegar razoavelmente perto de Alpha no desempenho inteiro, no desempenho de ponto flutuante a diferença era considerável. Por outro lado, o HP (PA-RISC) também está razoavelmente próximo do Alpha, mas esses processadores estão trabalhando com freqüências significativamente mais baixas (MHz). As tabelas carecem de dois valores importantes: o consumo de energia e o preço de uma CPU.

|

|

Sistemas baseados em Alpha

A primeira geração de sistemas baseados em DEC Alpha inclui estações de trabalho e servidores de gama baixa da série DEC 3000 AXP, servidores de gama média da série DEC 4000 AXP e servidores de gama alta da série DEC 7000 AXP e 10000 AXP. Os sistemas DEC 3000 AXP usam o mesmo barramento TURBOchannel que os modelos DECstation baseados em MIPS anteriores, enquanto o 4000 é baseado no Futurebus+ e os 7000/10000 compartilham uma arquitetura com os modelos VAX correspondentes.

DEC também produziu uma estação de trabalho Alpha de configuração de computador pessoal (PC) com um barramento Extended Industry Standard Architecture (EISA), o DECpc AXP 150 (codinome Jensen, também chamado de DEC 2000 AXP). Este é o primeiro sistema Alpha a oferecer suporte ao Windows NT. Mais tarde, a DEC produziu versões Alpha de suas linhas Celebris XL e Digital Personal Workstation PC, com processadores 21164.

A Digital também produziu computadores de placa única baseados no VMEbus para uso industrial e embarcado. A primeira geração inclui o AXPvme 64 e o AXPvme 64LC baseados em 21068, e o AXPvme 160 baseado em 21066. Eles foram lançados em 1º de março de 1994., enquanto o Alpha VME 4/224 e o Alpha VME 4/288 são baseados no processador 21064A. Os últimos modelos, o Alpha VME 5/352 e o Alpha VME 5/480, são baseados no processador 21164.

O chip 21066 é usado na estação de trabalho compacta DEC Multia VX40/41/42 e no laptop ALPHAbook 1 da Tadpole Technology.

Em 1994, a DEC lançou uma nova gama de sistemas AlphaStation e AlphaServer. Eles usam processadores 21064 ou 21164 e introduziram o barramento PCI, buffers de quadro compatíveis com VGA e teclados e mouses estilo PS/2. A série AlphaServer 8000 substitui o DEC 7000/10000 AXP e também emprega barramentos XMI e FutureBus+.

O AlphaStation XP1000 é a primeira estação de trabalho baseada no processador 21264. Os modelos AlphaServer/Station posteriores baseados no 21264 são categorizados em DS (servidor departamental), ES (servidor empresarial) ou GS (servidor global) famílias.

O chip 21364 final é usado nos modelos AlphaServer ES47, ES80 e GS1280 e no AlphaStation ES47.

Várias placas-mãe OEM foram produzidas pela DEC, como a AXPpci 33 "NoName" baseada em 21066 e 21068, que foi parte de um grande impulso para o mercado OEM pela empresa, a 21164- baseado em AlphaPC 164 e AlphaPC 164LX, o AlphaPC 164SX e AlphaPC 164RX baseado em 21164PC e o AlphaPC 264DP baseado em 21264. Vários terceiros, como Samsung e API, também produziram placas-mãe OEM, como API UP1000 e UP2000.

Para auxiliar terceiros no desenvolvimento de hardware e software para a plataforma, a DEC produziu Placas de Avaliação, como EB64+ e EB164 para os microprocessadores Alpha 21064A e 21164, respectivamente.

Os processadores 21164 e 21264 foram usados pela NetApp em vários sistemas de armazenamento conectados à rede, enquanto os processadores 21064 e 21164 foram usados pela Cray em seus supercomputadores paralelos massivos T3D e T3E.

Supercomputadores

O supercomputador mais rápido baseado em processadores Alpha foi o ASCI Q no Los Alamos National Laboratory. A máquina foi construída como um Cluster HP AlphaServer SC45/GS. Ele tinha CPUs 4096 Alpha (21264 EV-68, 1,25 GHz) e atingiu um Rmax de 7,727 TFLOPS. É afirmado por vários cientistas que a arquitetura Sunway que alimenta o Sunway TaihuLight é um descendente licenciado da arquitetura Alpha. Se contado como um supercomputador Alpha, o TaihuLight seria o sistema Alpha mais poderoso já construído, com uma classificação LINPACK de 93 petaflops, em 40.960 núcleos.

Contenido relacionado

HTML

Galileo (navegação por satélite)

Carl Benz