Cirix 6x86

O Cyrix 6x86 é uma linha de microprocessadores x86 de 32 bits de sexta geração projetados e lançados pela Cyrix em 1995. Cyrix, sendo uma empresa fabless, tinha os chips fabricados pela IBM e SGS- Thomson. O 6x86 foi feito como um concorrente direto da linha de microprocessadores Pentium da Intel e era compatível com pinos. Durante o desenvolvimento do 6x86, a maioria dos aplicativos (software de escritório e também jogos) realizavam operações quase inteiras. Os projetistas previram que os aplicativos futuros provavelmente manteriam esse foco de instrução. Assim, para otimizar o desempenho do chip para o que eles acreditavam ser a aplicação mais provável da CPU, os recursos de execução inteira receberam a maior parte do orçamento do transistor. Mais tarde, isso provou ser um erro estratégico, já que a popularidade do P5 Pentium fez com que muitos desenvolvedores de software otimizassem manualmente o código em linguagem assembly, para aproveitar as vantagens do FPU de menor latência e pipeline do P5 Pentium. Por exemplo, o tão aguardado jogo de tiro em primeira pessoa Quake usou um código de montagem altamente otimizado projetado quase inteiramente em torno do FPU do P5 Pentium. Como resultado, o P5 Pentium superou significativamente outras CPUs no jogo.

História

O 6x86, anteriormente sob o codinome "M1" foi anunciado pela Cyrix em outubro de 1995. No lançamento, apenas a versão de 100 MHz (P120+) estava disponível, mas uma versão de 120 MHz (P150+) foi planejada para meados de 1995 com um modelo de 133 MHz (P166+) posteriormente. O 6x86 de 100 MHz (P120+) estava disponível para OEMs por um preço de US$ 450 por chip em grandes quantidades.

Em meados de fevereiro de 1996, a Cyrix anunciou que o P166+, P150+ e P133+ seriam adicionados à linha de modelos 6x86. A IBM, que produziu os chips, também anunciou que venderá suas próprias versões dos chips.

O 6x86 P200+ foi planejado para o final de 1996, e acabou sendo lançado em junho.

O M2 (6x86MX) foi anunciado pela primeira vez para estar em desenvolvimento em meados de 1996. Teria MMX e otimização de 32 bits. O M2 também teria alguns dos mesmos recursos do Intel Pentium Pro, como renomeação de registro, conclusão fora de ordem e execução especulativa. Além disso, teria 64 KB de cache sobre o 6x86 original e 16 KB do Pentium Pro. Em março de 1997, quando questionado sobre quando a linha de processadores M2 começaria a ser enviada, o diretor administrativo da Cyrix UK, Brendan Sherry, afirmou: "Eu li que será em maio, mas dissemos final do segundo trimestre o tempo todo e tenho certeza de que conseguiremos isso.

O 6x86L foi lançado pela primeira vez em janeiro de 1997 para resolver os problemas de calor com a linha 6x86 original. O 6x86L tinha uma tensão V-core mais baixa e exigia um regulador de tensão split powerplane.

Em abril de 1997, o primeiro laptop a usar o processador 6x86 foi colocado à venda. Eles foram vendidos pela TigerDirect e tinham uma tela DSTN de 12,1 polegadas, 16 MB de memória, CD-ROM 10x, unidade de disco rígido de 1,3 GB e custavam $ 1.899 pelo preço base.

Mais tarde, no final de maio de 1997, no dia 27, a Cyrix disse que anunciaria os detalhes da nova linha de chips (6x86MX) um dia antes da Computex em junho de 1997. Para a extremidade inferior da série, o PR166 6x86MX estava disponível para $ 190 com versões de ponta PR200 e PR233 disponíveis por $ 240 e $ 320. A IBM, sendo a produtora dos chips Cyrix, também venderia sua própria versão. A Cyrix esperava enviar dezenas de milhares em junho de 1997, com até 1 milhão até o final do ano. A Cyrix também esperava lançar um chip de 266 MHz até o final de 1997 e um de 300 MHz no primeiro trimestre de 1998. Eles tinham um desempenho de ponto flutuante um pouco melhor, que reduzia a adição e multiplicação de tempos em um terço, mas ainda era mais lento do que o processador Intel Pentium. O M2 também tinha instruções MMX completas, 64 KB de cache sobre os 16 KB originais e tinha uma tensão de núcleo inferior de 2,5 V sobre 3,3 V da linha 6x86 original.

A National Semiconductor adquiriu a Cyrix em julho de 1997. A National Semiconductor não estava interessada em processadores de alto desempenho, mas sim em dispositivos de sistema em um chip, e queria mudar o foco da Cyrix para a linha MediaGX.

Em janeiro de 1998, a National Semiconductors produziu um processador 6x86MX em uma tecnologia de processo de 0,25 mícron. Isso reduziu o tamanho do chip de 150 milímetros quadrados para 88. A National mudou sua produção do MII e MediaGX para 0,25 em agosto.

Em setembro de 1998, a parceria de licenciamento da IBM com a Cyrix foi encerrada pela National Semiconductors. Isso ocorreu porque a National queria aumentar a produção de chips Cyrix em suas próprias instalações e porque a IBM produzir chips Cyrix estava causando problemas como perdas de lucro devido ao fato de a IBM frequentemente precificar suas versões dos chips Cyrix mais baixas.. A National pagaria de US$ 50 a US$ 55 milhões à IBM para encerrar a parceria, que terminaria em abril seguinte. A National então transferiria a produção de chips para suas próprias instalações em South Portland, Maine.

O Cyrix MII foi lançado em maio de 1998. Esses chips não eram empolgantes como as pessoas esperavam, pois eram apenas um rebranding do 6x86MX. Em dezembro, esses chips custavam US$ 80 para um MII-333, US$ 59 para um MII-300, US$ 55 para um MII-266 e US$ 48 para um MII-233.

Em maio de 1999, a National Semiconductor decidiu deixar o mercado de chips para PC devido a perdas significativas e colocou à venda a divisão de CPUs Cyrix.

A VIA comprou a linha Cyrix em junho de 1999 e encerrou o desenvolvimento de processadores de alto desempenho. O MII-433GP seria o último processador produzido pela Cyrix. Além disso, após a aquisição da VIA, o 6x86/L foi descontinuado, mas a linha 6x86MX/MII continuou a ser vendida pela VIA.

A VIA continuaria a produzir o MII no início dos anos 2000. Esperava-se que fosse descontinuado quando o VIA Cyrix MII fosse lançado. No entanto, o MII ainda estava disponível para venda até meados/final de 2003, sendo apresentado no site da VIA como um produto até outubro, e ainda via uso em dispositivos como computadores em rede.

Arquitetura

O 6x86 é superescalar e superpipeline e realiza renomeação de registradores, execução especulativa, execução fora de ordem e remoção de dependência de dados. No entanto, continuou a usar a execução x86 nativa e apenas microcódigo comum, como o Winchip da Centaur, ao contrário dos concorrentes Intel e AMD, que introduziram o método de tradução dinâmica para micro-operações com Pentium Pro e K5. O 6x86 é compatível com o soquete do Intel P54C Pentium e foi oferecido em seis níveis de desempenho: PR 90+, PR 120+, PR 133+, PR 150+, PR 166+ e PR 200+. Esses níveis de desempenho não são mapeados para a velocidade do clock do próprio chip (por exemplo, um PR 133+ executado a 110 MHz, um PR 166+ executado a 133 MHz etc.).

No que diz respeito aos caches internos, ele possui um cache primário de 16 KB e um cache de linha de instrução totalmente associativo de 256 bytes está incluído ao lado do cache primário, que funciona como o cache primário de instruções.

O 6x86 e o 6x86L não eram totalmente compatíveis com o conjunto de instruções Intel P5 Pentium e não são compatíveis com multiprocessador. Por esse motivo, o chip se identificou como 80486 e desativou a instrução CPUID por padrão. O suporte a CPUID pode ser habilitado primeiro habilitando registros CCR estendidos e, em seguida, definindo o bit 7 em CCR4. A falta de compatibilidade total com o P5 Pentium causou problemas com alguns aplicativos porque os programadores começaram a usar instruções específicas do P5 Pentium. Algumas empresas lançaram patches para seus produtos para fazê-los funcionar no 6x86.

A compatibilidade com o Pentium foi melhorada no 6x86MX, adicionando um contador de carimbo de tempo para suportar a instrução RDTSC do Pentium P5. O suporte para as instruções CMOVcc do Pentium Pro também foi adicionado.

Desempenho

Da mesma forma que a AMD com seus processadores K5 e K6 anteriores, a Cyrix usou uma classificação PR (Performance Rating) para relacionar seu desempenho ao Intel P5 Pentium (pré-P55C), como o desempenho por clock mais alto do 6x86 em relação a um Pentium P5 pode ser quantificado em relação a um Pentium com clock mais alto. Por exemplo, um 133 MHz 6x86 igualará ou superará um P5 Pentium em 166 MHz e, como resultado, a Cyrix poderia comercializar o chip de 133 MHz como sendo um P5 Pentium 166' igual. No entanto, a classificação PR não era uma representação totalmente verdadeira do desempenho do 6x86.

Embora o desempenho inteiro do 6x86 fosse significativamente maior do que o do Pentium P5, seu desempenho de ponto flutuante era mais medíocre - entre 2 e 4 vezes o desempenho do 486 FPU por ciclo de clock (dependendo da operação e precisão). O FPU no 6x86 era basicamente o mesmo circuito desenvolvido para os coprocessadores compatíveis com 8087/80287/80387 de alto desempenho anteriores da Cyrix, que era muito rápido para a época - o Cyrix FPU era muito mais rápido que o 80387 e até mesmo o 80486 FPU. No entanto, ainda era consideravelmente mais lento do que os novos e completamente redesenhados FPUs P5 Pentium e P6 Pentium Pro-Pentium III. Uma das principais características dos FPUs P5/P6 é que eles suportam a intercalação de FPU e instruções inteiras em seu design, que os chips Cyrix não integram. Isso causou um desempenho muito ruim com as CPUs Cyrix em jogos e softwares que se aproveitaram disso.

Portanto, apesar de serem muito rápidos relógio a relógio, o 6x86 e o MII foram forçados a competir no segmento inferior do mercado, já que AMD K6 e Intel P6 Pentium II estavam sempre à frente em velocidade de relógio. O 6x86's e MII's velha geração "486 classe" unidade de ponto flutuante combinada com uma seção inteira que estava no máximo no mesmo nível dos chips P6 e K6 mais recentes significava que Cyrix não poderia mais competir em desempenho.

Modelos e variantes

6x86

O 6x86 (codinome M1) foi lançado pela Cyrix em 1996. A primeira geração do 6x86 apresentava problemas de aquecimento. Isso foi causado principalmente por sua maior produção de calor do que outras CPUs x86 da época e, como tal, os fabricantes de computadores às vezes não os equipavam com resfriamento adequado. As CPUs chegaram a cerca de 25 W de saída de calor (como o AMD K6), enquanto o P5 Pentium produziu cerca de 15 W de calor residual em seu pico. No entanto, ambos os números seriam uma fração do calor gerado por muitos processadores de alto desempenho, alguns anos depois. Logo após o M1 original, o M1R foi lançado. O M1R foi uma mudança do processo SGS-Thomson 3M para o processo IBM 5M, tornando os chips 6x86 50% menores.

6x86L

O 6x86L (codinome M1L) foi lançado posteriormente pela Cyrix para resolver problemas de calor; o L significa baixa potência. As tecnologias de fabricação aprimoradas permitiram o uso de um Vcore mais baixo. Assim como o Pentium MMX, o 6x86L exigia um regulador de tensão split powerplane com tensões separadas para E/S e núcleo da CPU.

6x86MX / MII

Outra versão do 6x86, o 6x86MX, adicionou compatibilidade MMX junto com o conjunto de instruções EMMI, melhorou a compatibilidade com o Pentium e o Pentium Pro adicionando um contador de registro de data e hora e instruções CMOVcc, respectivamente, e quadruplicou o tamanho do cache principal para 64 KB. O cache de linha de instrução de 256 bytes pode ser transformado em um cache de rascunho para fornecer suporte para operações multimídia. As revisões posteriores deste chip foram renomeadas como MII, para competir melhor com o processador Pentium II. Infelizmente, 6x86MX / MII chegou tarde ao mercado e não conseguiu escalar bem em velocidade de clock com os processos de fabricação usados na época.

Tabela de modelo

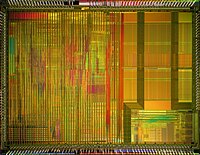

| Imagens | Modelo | Nome do núcleo | Tamanho do processo

(μm) | Área de morrer

(mm2) | Número de transistores

(milhões) | Soquete (s) | Pacote | Tensão do núcleo | TDP (W) | Velocidade do relógio | Velocidade do ônibus | L1 Cacheca | Preço (USD) | Lançamento |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| PR90+ | M1 | 0,65 | 394 | 3.0. | Soquete 7 | CPGA | 3.3 | 15.5 | 80 MHz | 40 MHz | 16 KB | $84 | Relatório 1995 | |

| PR120+ | M1 | 0,65 | 394 | 3.0. | Soquete 7 | CPGA | 3.3 | ? | 100 MHz | 50 MHz | 16 KB | $450 | Outubro 1995 | |

| PR133+ | M1R | 0,65 | 225 | 3.0. | Soquete 7 | CPGA | 3.3 | 19.1 | 110 MHz | 55 MHz | 16 KB | $326 | 2-5-1996 | |

| PR150+ | M1R | 0,65 | 225 | 3.0. | Soquete 7 | CPGA | 3.3/3.52 | 20.1 | 120 MHz | 60 MHz | 16 KB | $451 | 2-5-1996 | |

| PR166+ | M1R | 0,65 | 225 | 3.0. | Soquete 7 | CPGA | 3.3/3.52 | 21.8 | 133 MHz | 66 MHz | 16 KB | $621 | 2-5-1996 | |

| PR200+ | M1R | 0,44 | ? | 3.0. | Soquete 7 | CPGA | 3.52 | 17.13 | 150 MHz | 75 MHz | 16 KB | $499 | 6-6-1996 | |

| L-PR120+ | M1L | 0,35 | 169 | 3.0. | Soquete 7 | CPGA | 2,8/3.3 | ? | 100 MHz | 50 MHz | 16 KB | ? | Jan-1997 | |

| L-PR133+ | M1L | 0,35 | 169 | 3.0. | Soquete 7 | CPGA | 2,8/3.3 | ? | 110 MHz | 55 MHz | 16 KB | ? | Fev-1997 | |

| L-PR150+ | M1L | 0,35 | 169 | 3.0. | Soquete 7 | CPGA | 2,8/3.3 | ? | 120 MHz | 60 MHz | 16 KB | ? | Mar-1997 | |

| L-PR166+ | M1L | 0,35 | 169 | 3.0. | Soquete 7 | CPGA | 2,8/3.3 | 15.98 | 133 MHz | 66 MHz | 16 KB | ? | Abr/1997 | |

| L-PR200+ | M1L | 0,35 | 169 | 3.0. | Soquete 7 | CPGA | 2,8/3.3 | 17.13 | 150 MHz | 75 MHz | 16 KB | ? | Abr/1997 | |

| PR166-MMX | MII | 0,35 | 197 | 6. | Soquete 7 | CPGA | 2.9/3.3 | ?

? | 133 MHz

150 MHz | 66 MHz

60 MHz | 64 KB | $190

? | 5-30-97

Q2 1998 | |

| PR200-MMX | MII | 0,35 (IBM)

0,30 (NS) | 197

156 | 6. | Soquete 7 | CPGA | 2.9/3.3 | ?

? | 150 MHz

166 MHz | 75 MHz

66 MHz | 64 KB | $240

? | 5-30-97

Q2 1998 | |

| PR233-MMX | MII | 0,35 (IBM)

0,30 (NS) | 197

156 | 6. | Soquete 7 | CPGA | 2.9/3.3 | ?

? | 188 MHz

200 MHz | 75 MHz

66 MHz | 64 KB | $320

? | 5-30-97

Q2 1998 | |

| PR266-MMX | MII | 0,35 (IBM)

0,30 (NS) | 197

156 | 6. | Soquete 7 | CPGA | 2.9/3.3 | ? | 208 MHz | 83 MHz | 64 KB | $180

? | 3-19-98

Q2 1998 | |

| MII-300-MMX (*m) | MII | 0,30

0,25 | 156

88 | 6. | Super 7 | CPGA | 2.9/3.3

2.2 (*m) | ?

? | 233 MHz

225 MHz | 66 MHz

75 MHz | 64 KB | $180

? | 4-14-98

Q1 1999 | |

| MII-333-MMX (*m) | MII | 0,30

0,25 | 156

88 | 6. | Super 7 | CPGA | 2.9/3.3

2.2 (*m) | ?

? | 250 MHz | 100 MHz

83 MHz | 64 KB | $180

? | 6-15-98

Mar-1999 | |

| MII-350-MMX | MII | 0,25 | 88 | 6. | Super 7 | CPGA | 2.9/3.3 | ? | 270 MHz

250 MHz | 90 MHz

83 MHz | 64 KB | ?

? | ?

? | |

| MII-366-MMX | MII | 0,25 | 88 | 6. | Super 7 | CPGA | 2.9/3.3 | ? | 250 MHz | 100 MHz | 64 KB | ? | Mar-1999 | |

| MII-400-MMX (*m) | MII | 0,18 | 65 | 6. | Super 7 | CPGA | 2.2/3.3 | ? | 285 MHz | 95 MHz | 64 KB | ? | Jun-1999 | |

| MII-433-MMX (*m) | MII | 0,18 | 65 | 6. | Super 7 | CPGA | 2.2/3.3 | ? | 300 MHz | 100 MHz | 64 KB | ? | Jun-1999 | |

| ? | Modelos SGS-Thomson 6x86 | |||||||||||||

| ST6x86P90+HS | M1 | 0,65 | 394 | 3.0. | Soquete 7 | CPGA | 3.52 | 17.39 | 80 MHz | 40 MHz | 16 KB | ? | ? | |

| ST6x86P120+HS | M1 | 0,65 | 394 | 3.0. | Soquete 7 | CPGA | 3.52 | 19.98 | 100 MHz | 50 MHz | 16 KB | ? | 2-5-1996 | |

| ST6x86P133+HS | M1 | 0,65 | 394 | 3.0. | Soquete 7 | CPGA | 3.52 | 21.46 | 110 MHz | 55 MHz | 16 KB | ? | 2-5-1996 | |

| ST6x86P150+HS | M1 | 0,65 | 225 | 3.0. | Soquete 7 | CPGA | 3.52 | ? | 120 MHz | 60 MHz | 16 KB | ? | 2-5-1996 | |

| ST6x86P166+HS | M1 | 0,65 | 225 | 3.0. | Soquete 7 | CPGA | 3.52 | ? | 133 MHz | 66 MHz | 16 KB | ? | 2-5-1996 | |

| ST6x86P200+HS | M1 | 0,44 | ? | 3.0. | Soquete 7 | CPGA | 3.52 | ? | 150 MHz | 75 MHz | 16 KB | ? | ? | |

| Modelos IBM 6x86 | ||||||||||||||

| 2V2100GB | M1 | 0,65 | 394 | 3.0. | Soquete 7 | CPGA | 3.3 | ? | 80 MHz | 40 MHz | 16 KB | ? | ? | |

| 2V2P120GC | M1 | 0,65 | 394 | 3.0. | Soquete 7 | CPGA | 3.3 | ? | 100 MHz | 50 MHz | 16 KB | ? | ? | |

| 2V2120GB | M1R | 0,65 | 394 | 3.0. | Soquete 7 | CPGA | 3.33 | ? | 100 MHz | 50 MHz | 16 KB | ? | ? | |

| 2V2P150GE | M1R | 0,65 | 225 | 3.0. | Soquete 7 | CPGA | 3.3/3.52 | ? | 120 MHz | 60 MHz | 16 KB | ? | 2-5-1996 | |

| 2V2P166GE | M1R | 0,65 | 225 | 3.0. | Soquete 7 | CPGA | 3.3/3.52 | 21.8 | 133 MHz | 66 MHz | 16 KB | ? | 2-5-1996 | |

| 2V7P200E | M1R | 0,44 | ? | 3.0. | Soquete 7 | CPGA | 3.52 | 14 | 150 MHz | 75 MHz | 16 KB | ? | 2-5-1996 | |

| 2VAP120GB | M1L | 0,35 | 169 | 3.0. | Soquete 7 | CPGA | 2. | ? | 100 MHz | 50 MHz | 16 KB | ? | ? | |

| 2VAP150GB | M1L | 0,35 | 169 | 3.0. | Soquete 7 | CPGA | 2. | ? | 120 MHz | 60 MHz | 16 KB | ? | ? | |

| 2VAP166GB | M1L | 0,35 | 169 | 3.0. | Soquete 7 | CPGA | 2. | ? | 133 MHz | 66 MHz | 16 KB | ? | ? | |

| 2VAP200GB | M1L | 0,35 | 169 | 3.0. | Soquete 7 | CPGA | 2. | ? | 150 MHz | 75 MHz | 16 KB | ? | ? | |

| AVAPR166GB | MII | 0,35 | 197 | 6. | Soquete 7 | CPGA | 2.9/3.3 | ? | 133 MHz | 66 MHz | 64 KB | $202 | 5-30-97 | |

| ? | MII | 0,35 | 197 | 6. | Soquete 7 | CPGA | 2.9/3.3 | ? | 150 MHz | 60 MHz | 64 KB | ? | 5-30-97 | |

| BVAPR200GB | MII | 0,35 | ? | 6. | Soquete 7 | CPGA | 2.9/3.3 | ? | 150 MHz | 75 MHz | 64 KB | $369 | 5-30-97 | |

| AVAPR200GA | MII | 0,30 | ? | 6. | Soquete 7 | CPGA | 2.9/3.3 | ? | 166 MHz | 66 Mhz | 64 KB | ? | Q2 1998 | |

| BVAPR233GC | MII | 0,35 | ? | 6. | Soquete 7 | CPGA | 2.9/3.3 | ? | 166 MHz | 83 MHz | 64 KB | $477 | 5-30-97 | |

| AVAPR233GB | MII | 0,30 | ? | 6. | Soquete 7 | CPGA | 2.9/3.3 | ? | 188 MHz | 75 MHz | 64 KB | ? | Q2 1998 | |

| BVAPR233GD | MII | 0,30 | ? | 6. | Soquete 7 | CPGA | 2.9/3.3 | ? | 200 MHz | 66 MHz | 64 KB | ? | Q2 1998 | |

| BVAPR266 | MII | 0,35

0,30 | ? | 6. | Soquete 7 | CPGA | 2.9/3.3 | ? | 208 MHz | 83 MHz | 64 KB | ? | 3-19-98

Q2 1998 | |

| CVAPR300GF (*m) | MII | 0,25 | 119 | 6. | Super 7 | CPGA | 2.9/3.3 | ? | 225 MHz | 75 MHz | 64 KB | $217 | 3-19-98 | |

| DVAPR300GF (*m) | MII | 0,25 | 119 | 6. | Super 7 | CPGA | 2.9/3.3 | ? | 233 MHz | 66 MHz | 64 KB | ? | ? | |

| CVAPR333GF (*m) | MII | 0,25 | 119 | 6. | Super 7 | CPGA | 2.9/3.3

2.2 (*m) | ? | 250 MHz | 83 MHz | 64 KB | $299 | 3-19-98 | |

| ? | MII | 0,25 | 119 | 6. | Super 7 | CPGA | 2.9/3.3 | ? | 263 MHz | 75 MHz | 64 KB | ? | ? | |

| ? - Informações perdidas

*m -Disponível em versão móvel para laptops Informação de:

| ||||||||||||||

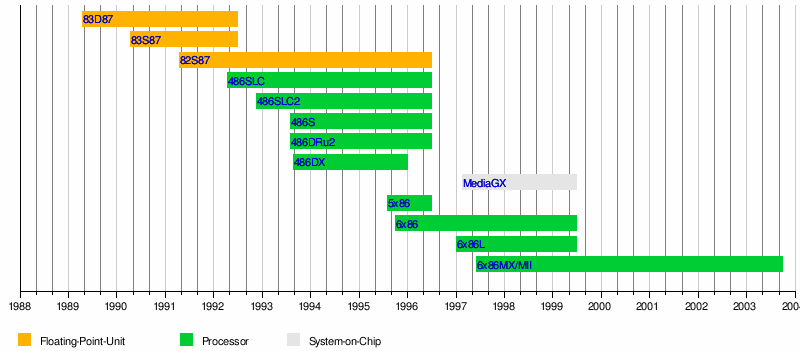

Cronograma

| Linha do tempo de produtos Cyrix |

|---|

|

Contenido relacionado

Hierarquia de Chomsky

Ferrovia do Pacífico Canadense

Complexidade de Kolmogorov