X86-64

x86-64 (también conocido como x64, x86_64, AMD64 e Intel 64 ) es una versión de 64 bits del conjunto de instrucciones x86, lanzado por primera vez en 1999. Introdujo dos nuevos modos de operación, el modo de 64 bits y el modo de compatibilidad, junto con un nuevo modo de paginación de 4 niveles.

Con el modo de 64 bits y el nuevo modo de paginación, admite cantidades mucho mayores de memoria virtual y memoria física de lo que era posible en sus predecesores de 32 bits, lo que permite que los programas almacenen mayores cantidades de datos en la memoria. x86-64 también amplía los registros de uso general a 64 bits y amplía el número de ellos de 8 (algunos de los cuales tenían una funcionalidad limitada o fija, por ejemplo, para la gestión de pilas) a 16 (totalmente generales) y proporciona muchas otras mejoras. La aritmética de punto flotante se admite a través de instrucciones obligatorias similares a SSE2, y los registros de estilo x87/MMX generalmente no se usan (pero aún están disponibles incluso en el modo de 64 bits); en su lugar, se utiliza un conjunto de 16 registros vectoriales, de 128 bits cada uno. (Cada registro puede almacenar uno o dos números de precisión doble o de uno a cuatro números de precisión simple, o varios formatos de enteros). En el modo de 64 bits, las instrucciones se modifican para admitir operandos de 64 bits y modo de direccionamiento de 64 bits.

El modo de compatibilidad definido en la arquitectura permite que las aplicaciones de usuario de 16 y 32 bits se ejecuten sin modificaciones, coexistiendo con aplicaciones de 64 bits si el sistema operativo de 64 bits las admite. Dado que los conjuntos completos de instrucciones x86 de 16 bits y 32 bits permanecen implementados en el hardware sin ninguna emulación intermedia, estos ejecutables más antiguos pueden ejecutarse con poca o ninguna penalización en el rendimiento, mientras que las aplicaciones más nuevas o modificadas pueden aprovechar las nuevas características del diseño del procesador para lograr mejoras en el rendimiento. Además, un procesador compatible con x86-64 todavía se enciende en modo real para una compatibilidad total con versiones anteriores del 8086, como lo han hecho los procesadores x86 compatibles con el modo protegido desde el 80286.

La especificación original, creada por AMD y lanzada en 2000, ha sido implementada por AMD, Intel y VIA. La microarquitectura AMD K8, en los procesadores Opteron y Athlon 64, fue la primera en implementarla. Esta fue la primera adición significativa a la arquitectura x86 diseñada por una empresa distinta de Intel. Intel se vio obligado a hacer lo mismo e introdujo una familia NetBurst modificada que era compatible con el software con la especificación de AMD. VIA Technologies introdujo x86-64 en su arquitectura VIA Isaiah, con VIA Nano.

La arquitectura x86-64 se adoptó rápidamente para servidores y computadoras personales de escritorio y portátiles que normalmente se configuraban para 16 GB de memoria o más. Ha reemplazado efectivamente la arquitectura Intel Itanium descontinuada (anteriormente IA-64), que originalmente estaba destinada a reemplazar la arquitectura x86. x86-64 e Itanium no son compatibles en el nivel de conjunto de instrucciones nativas, y los sistemas operativos y las aplicaciones compilados para una arquitectura no se pueden ejecutar en la otra.

AMD64

Historia

AMD64 (también denominado de diversas formas por AMD en su literatura y documentación como "Tecnología AMD de 64 bits" y "Arquitectura AMD x86-64") se creó como una alternativa a la arquitectura IA-64 radicalmente diferente diseñada por Intel y Hewlett-Packard, que era incompatible con versiones anteriores de IA-32, la versión de 32 bits de la arquitectura x86. AMD anunció originalmente AMD64 en 1999 con una especificación completa disponible en agosto de 2000. Como nunca se invitó a AMD a contribuir con la arquitectura IA-64 y cualquier tipo de licencia parecía poco probable, AMD posicionó la arquitectura AMD64 desde el principio como una forma evolutiva de agregar capacidades informáticas de 64 bits a la arquitectura x86 existente mientras se admite el código x86 heredado de 32 bits, a diferencia del enfoque de Intel de crear una arquitectura de 64 bits completamente nueva y completamente incompatible con x86 con IA- 64.

El primer procesador basado en AMD64, Opteron, se lanzó en abril de 2003.

Implementaciones

Los procesadores de AMD que implementan la arquitectura AMD64 incluyen Opteron, Athlon 64, Athlon 64 X2, Athlon 64 FX, Athlon II (seguidos de "X2", "X3", o "X4" para indicar el número de núcleos y modelos XLT), Turion 64, Turion 64 X2, Sempron ("Palermo" E6 stepping y todos los "Manila" modelos), Phenom (seguido de "X3" o "X4" para indicar el número de núcleos), Phenom II (seguido de "X2", " X3", "X4" o "X6" para indicar el número de núcleos), FX, Fusion/APU y Ryzen/Epyc.

Características arquitectónicas

La principal característica definitoria de AMD64 es la disponibilidad de registros de procesador de uso general de 64 bits (por ejemplo, rax), operaciones aritméticas y lógicas de enteros de 64 bits y Direcciones virtuales de 64 bits. Los diseñadores aprovecharon la oportunidad para realizar otras mejoras también.

Los cambios notables en las extensiones de 64 bits incluyen:

- Capacidad de entrada de 64 bits

- Todos los registros generales (GPRs) se expanden de 32 bits a 64 bits, y todas las operaciones aritméticas y lógicas, memoria a registro y operaciones de registro a memoria, etc., pueden operar directamente en enteros de 64 bits. Empuja y aparece en la pila predeterminada a los pasos de 8 bytes, y los punteros son de 8 bytes de ancho.

- Registros adicionales

- Además de aumentar el tamaño de los registros para fines generales, el número de registros para fines generales se incrementa de ocho (es decir, ocho). eax, ecx, edx, ebx, esp, ebp, esi, edi) en x86 a 16 (es decir. rax, rcx, rdx, rbx, rsp, rbp, rsi, rdi, r8, r9, r10, r11, r12, r13, r14, r15). Por lo tanto, es posible mantener más variables locales en registros en lugar de en la pila, y permitir que los registros mantengan constantes a menudo accedidas; los argumentos para pequeñas y rápidas subrutinas también pueden pasarse en registros en mayor medida.

- AMD64 todavía tiene menos registros que muchos conjuntos de instrucciones RISC (p. ej. PA-RISC, Power ISA y MIPS tienen 32 GPRs; Alpha, 64-bit ARM, y SPARC tienen 31) o máquinas similares a VLIW como el IA-64 (que tiene 128 registros). Sin embargo, una implementación de AMD64 puede tener registros mucho más internos que el número de registros arquitectónicos expuestos por el conjunto de instrucciones (ver renombramiento del registro). (Por ejemplo, los núcleos AMD Zen tienen 168 números enteros de 64 bits y 160 registros internos de 128 bits de punto flotante de vectores.)

- Registros adicionales de XMM (SSE)

- Asimismo, el número de registros XMM de 128 bits (utilizados para la transmisión de instrucciones SIMD) también se incrementa de 8 a 16.

- La pila de registro x87 FPU tradicional no está incluida en la extensión de tamaño de archivo registrado en modo de 64 bits, en comparación con los registros XMM utilizados por SSE2, que se extendió. La pila de registro x87 no es un simple archivo de registro, aunque permite el acceso directo a registros individuales por operaciones de intercambio de bajo costo.

- Espacio de dirección virtual más grande

- La arquitectura AMD64 define un formato de dirección virtual de 64 bits, de los cuales se utilizan 48 bits bajo pedido en implementaciones actuales. Esto permite hasta 256 TB (248 bytes) de espacio de dirección virtual. La definición de arquitectura permite que este límite se plantee en futuras implementaciones a los 64 bits completos, ampliando el espacio de dirección virtual a 16 EB (264 bytes). Esto se compara con sólo 4 GB (232 bytes) para el x86.

- Esto significa que los archivos muy grandes pueden ser operados mediante la asignación de todo el archivo en el espacio de dirección del proceso (que a menudo es mucho más rápido que trabajar con llamadas de lectura/escritura de archivos), en lugar de tener que mapear regiones del archivo dentro y fuera del espacio de la dirección.

- Espacio de dirección física más grande

- La aplicación original de la arquitectura AMD64 implementó direcciones físicas de 40 bits, por lo que podría abordar hasta 1 TB (240 bytes) de RAM. Las implementaciones actuales de la arquitectura AMD64 (a partir de la microarquitectura AMD 10h) extienden esto a direcciones físicas de 48 bits y por lo tanto pueden abordar hasta 256 TB (248 bytes) de RAM. La arquitectura permite extender esto a 52 bits en el futuro (limitado por el formato de entrada de la tabla de página); esto permitiría abordar hasta 4 PB de RAM. Para la comparación, los procesadores x86 de 32 bits se limitan a 64 GB de RAM en modo de extensión de dirección física (PAE), o 4 GB de RAM sin modo PAE.

- Espacio de dirección física más grande en el modo legado

- Al operar en modo legado, la arquitectura AMD64 admite Extensión de Dirección Física (PAE), al igual que la mayoría de procesadores x86 actuales, pero AMD64 extiende PAE de 36 bits a un límite arquitectónico de 52 bits de dirección física. Por lo tanto, cualquier aplicación permite el mismo límite de dirección física que en el modo largo.

- Instruction pointer relative data access

- Las instrucciones pueden ahora hacer referencia a datos relativos al puntero de instrucción (registro RIP). Esto hace que el código independiente de la posición, como se utiliza a menudo en bibliotecas compartidas y el código cargado a tiempo de ejecución, más eficiente.

- Instrucciones del SSE

- La arquitectura original de AMD64 adoptó SSE y SSE2 de Intel como instrucciones básicas. Estos conjuntos de instrucciones proporcionan un suplemento vectorial al escalar x87 FPU, para los tipos de datos de precisión y doble precisión. SSE2 también ofrece operaciones vectoriales enteros, para tipos de datos que van desde 8bit a 64bit de precisión. Esto hace que las capacidades vectoriales de la arquitectura a la par con las de los procesadores x86 más avanzados de su tiempo. Estas instrucciones también se pueden utilizar en modo de 32 bits. La proliferación de procesadores de 64 bits ha hecho que estas capacidades vectoriales ubicuas en las computadoras domésticas, permitiendo la mejora de los estándares de aplicaciones de 32 bits. La edición de 32 bits de Windows 8, por ejemplo, requiere la presencia de instrucciones SSE2. SSE3 instrucciones y posteriores Streaming SIMD Extensiones conjuntos de instrucciones no son características estándar de la arquitectura.

- No-Ejecutar bit

- El bit No-Execute o NX (bit 63 de la entrada de la tabla de página) permite al sistema operativo especificar qué páginas del espacio de dirección virtual pueden contener código ejecutable y que no puede. Un intento de ejecutar código de una página etiquetada "no ejecutar" resultará en una violación de acceso a la memoria, similar a un intento de escribir a una página de sólo lectura. Esto debe hacer que sea más difícil para el código malicioso tomar el control del sistema a través de ataques "sobrecostos de amortiguación" o "descontrolados de amortiguación". Una característica similar ha sido disponible en procesadores x86 desde el 80286 como atributo de descriptores de segmento; sin embargo, esto funciona sólo en un segmento entero a la vez.

- Segmented addressing ha sido considerado durante mucho tiempo un modo obsoleto de operación, y todos los sistemas operativos PC actuales en efecto lo superan, estableciendo todos los segmentos a una dirección base de cero y (en su implementación de 32 bits) un tamaño de 4 GB. AMD fue el primer proveedor de la familia x86 para implementar no ejecutar en modo de dirección lineal. La característica también está disponible en modo legado en procesadores AMD64, y procesadores Intel x86 recientes, cuando se utiliza PAE.

- Eliminación de características antiguas

- Algunas características de "programación del sistema" de la arquitectura x86 no se utilizaron o se subutilizaron en los sistemas operativos modernos y tampoco están disponibles en el modo AMD64 largo (64 bits y compatibilidad), o sólo existen en forma limitada. Estos incluyen el abordaje segmentado (aunque los segmentos de FS y GS se mantienen en forma vestigial para su uso como punteros extrabase a estructuras del sistema operativo), el mecanismo de conmutación del estado de tarea y el modo 8086 virtual. Estas características permanecen plenamente implementadas en "modo delegación", permitiendo a estos procesadores ejecutar sistemas operativos de 32 bits y 16 bits sin modificaciones. Algunas instrucciones que resultaron ser raramente útiles no se soportan en modo de 64 bits, incluyendo el ahorro/restauración de registros de segmentos en la pila, el ahorro/restauración de todos los registros (PUSHA/POPA), instrucciones de aritmética decimal, BOUND e INTO, y saltos de "far" y llamadas con operados inmediatos.

Detalles del espacio de direcciones virtuales

Direcciones de forma canónica

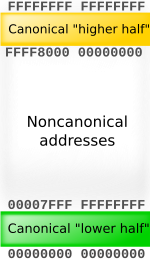

Aunque las direcciones virtuales tienen 64 bits de ancho en el modo de 64 bits, las implementaciones actuales (y todos los chips que se sabe que están en las etapas de planificación) no permiten el espacio completo de direcciones virtuales de 264 bytes (16 EB) que se utilizarán. Esto sería aproximadamente cuatro mil millones de veces el tamaño del espacio de direcciones virtuales en máquinas de 32 bits. La mayoría de los sistemas operativos y aplicaciones no necesitarán un espacio de direcciones tan grande en el futuro previsible, por lo que implementar direcciones virtuales tan amplias simplemente aumentaría la complejidad y el costo de la traducción de direcciones sin ningún beneficio real. Por lo tanto, AMD decidió que, en las primeras implementaciones de la arquitectura, solo los 48 bits menos significativos de una dirección virtual se utilizarían en la traducción de direcciones (búsqueda en la tabla de páginas).

Además, la especificación AMD requiere que los 16 bits más significativos de cualquier dirección virtual, los bits 48 a 63, deben ser copias del bit 47 (de manera similar a la extensión de signo). Si no se cumple este requisito, el procesador generará una excepción. Las direcciones que cumplen con esta regla se conocen como "forma canónica". Las direcciones de formulario canónico van desde 0 hasta 00007FFF'FFFFFFFF, y desde FFFF8000'00000000 hasta FFFFFFFF'FFFFFFFF, para un total de 256 TB de espacio de direcciones virtuales utilizable. Esto sigue siendo 65.536 veces más grande que el espacio de direcciones virtuales de 4 GB de las máquinas de 32 bits.

Esta función facilita la escalabilidad posterior al direccionamiento real de 64 bits. Muchos sistemas operativos (que incluyen, entre otros, la familia Windows NT) toman la mitad del espacio de direcciones con la dirección superior (denominado espacio del kernel) para sí mismos y dejan la mitad con la dirección inferior (espacio del usuario) para el código de la aplicación, el modo de usuario pilas, montones y otras regiones de datos. La "dirección canónica" El diseño garantiza que cada implementación compatible con AMD64 tenga, en efecto, dos mitades de memoria: la mitad inferior comienza en 00000000'00000000 y "crece hacia arriba" a medida que haya más bits de direcciones virtuales disponibles, mientras que la mitad superior está "acoplada" hasta la parte superior del espacio de direcciones y crece hacia abajo. Además, hacer cumplir la "forma canónica" de direcciones al verificar los bits de dirección no utilizados evita que el sistema operativo los use en punteros etiquetados como banderas, marcadores de privilegio, etc., ya que dicho uso podría volverse problemático cuando la arquitectura se extienda para implementar más bits de dirección virtual.

Las primeras versiones de Windows para x64 ni siquiera usaban los 256 TB completos; estaban restringidos a solo 8 TB de espacio de usuario y 8 TB de espacio de kernel. Windows no admitió todo el espacio de direcciones de 48 bits hasta Windows 8.1, que se lanzó en octubre de 2013.

Estructura de la tabla de páginas

El modo de direccionamiento de 64 bits ("modo largo") es un superconjunto de extensiones de direcciones físicas (PAE); por este motivo, los tamaños de página pueden ser de 4 KB (212 bytes) o 2 MB (221 bytes). El modo largo también admite tamaños de página de 1 GB (230 bytes). En lugar del sistema de tabla de páginas de tres niveles utilizado por los sistemas en modo PAE, los sistemas que se ejecutan en modo largo utilizan cuatro niveles de tabla de páginas: la tabla de punteros de directorio de páginas de PAE se amplía a partir de cuatro entradas a 512, y se agrega una tabla adicional de nivel de mapa de página 4 (PML4), que contiene 512 entradas en implementaciones de 48 bits. Una jerarquía de mapeo completa de páginas de 4 KB para todo el espacio de 48 bits requeriría un poco más de 512 GB de memoria (alrededor del 0,195 % del espacio virtual de 256 TB).

Intel ha implementado un esquema con una tabla de páginas de 5 niveles, que permite que los procesadores Intel 64 admitan un espacio de direcciones virtuales de 57 bits. Otras extensiones pueden permitir un espacio completo de direcciones virtuales y memoria física de 64 bits al expandir el tamaño de entrada de la tabla de páginas a 128 bits, y reducir los paseos por páginas en la jerarquía de 5 niveles al usar un tamaño de asignación de página mayor de 64 KB que aún admite 4 KB Operaciones de página para compatibilidad con versiones anteriores.

Límites del sistema operativo

El sistema operativo también puede limitar el espacio de direcciones virtuales. Los detalles, cuando corresponda, se proporcionan en la sección "Compatibilidad y características del sistema operativo" sección.

Detalles del espacio de direcciones físicas

Los procesadores AMD64 actuales admiten un espacio de direcciones físicas de hasta 248 bytes de RAM o 256 TB. Sin embargo, a partir de 2020, no se conocían placas base x86-64 que admitieran 256 TB de RAM. El sistema operativo puede imponer límites adicionales a la cantidad de RAM que se puede usar o admitir. Los detalles sobre este punto se proporcionan en la sección "Compatibilidad y características del sistema operativo" sección de este artículo.

Modos de funcionamiento

La arquitectura tiene dos modos principales de operación: modo largo y modo heredado.

| Funcionamiento | Sistema operativo necesario | Tipo de código que se está ejecutando | Tamaño (en bits) | Número de registros para fines generales | ||

|---|---|---|---|---|---|---|

| modo | submodo | direcciones | operandosdefault in italics) | |||

| Modo largo | Modo de 64 bits | Sistema operativo de 64 bits, firmware UEFI de 64 bits, o los dos anteriores interactuando a través de la interfaz UEFI de un firmware de 64 bits | 64-bit | 64 | 8, 16, 32, 64 | 16 |

| Modo de compatibilidad | Bootloader o sistema operativo de 64 bits | 32-bit | 32 | 8, 16, 32 | 8 | |

| Modo protegido de 16 bits | 16 | 8, 16, 32 | 8 | |||

| Modo de Legacy | Modo protegido | Bootloader, 32 bit OS, 32 bits de firmware de la UEFI, o los dos últimos interactuando a través de la interfaz de la UEFI del firmware | 32-bit | 32 | 8, 16, 32 | 8 |

| Sistema operativo del modo protegido de 16 bits | Modo protegido de 16 bits | 16 | 8, 16, 32 | 8 | ||

| Modo virtual 8086 | modo protegido de 16 bits o sistema operativo de 32 bits | subconjunto de modo real | 16 | 8, 16, 32 | 8 | |

| Modo irreal | Bootloader o modo real OS | modo real | 16, 20, 32 | 8, 16, 32 | 8 | |

| Modo real | Bootloader, modo real OS, o cualquier OS interfacing con la interfaz BIOS de un firmware | modo real | 16, 20, 21 | 8, 16, 32 | 8 | |

- ^ a b c d Tenga en cuenta que el código de 16 bits escrito para el 80286 y abajo no utiliza instrucciones de 32 bits. El código escrito para el 80386 y arriba puede utilizar el prefijo de anulación de tamaño operativo (0x66). Normalmente este prefijo es utilizado por código de modo protegido y largo con el propósito de utilizar 16 bits operandos, ya que ese código se ejecutaría en un segmento de código con un tamaño de operación predeterminado de 32 bits. En modo real, el tamaño de operand predeterminado es de 16 bits, por lo que el prefijo 0x66 se interpreta de manera diferente, cambiando el tamaño de operand a 32 bits.

Modo largo

El modo largo es el modo de funcionamiento principal previsto de la arquitectura; es una combinación del modo nativo de 64 bits del procesador y un modo de compatibilidad combinado de 32 y 16 bits. Lo utilizan los sistemas operativos de 64 bits. En un sistema operativo de 64 bits, los programas de 64 bits se ejecutan en modo de 64 bits y las aplicaciones en modo protegido de 32 y 16 bits (que no necesitan usar el modo real o el modo 8086 virtual para ejecutarse en cualquier momento). tiempo) se ejecutan en modo de compatibilidad. Los programas en modo real y los programas que usan el modo 8086 virtual en cualquier momento no se pueden ejecutar en modo largo a menos que esos modos se emulen en el software. Sin embargo, dichos programas pueden iniciarse desde un sistema operativo que se ejecuta en modo largo en procesadores compatibles con VT-x o AMD-V mediante la creación de un procesador virtual que se ejecuta en el modo deseado.

Dado que el conjunto de instrucciones básico es el mismo, casi no se penaliza el rendimiento al ejecutar código x86 en modo protegido. Esto es diferente al IA-64 de Intel, donde las diferencias en el conjunto de instrucciones subyacentes significan que la ejecución del código de 32 bits debe hacerse en emulación de x86 (lo que hace que el proceso sea más lento) o con un coprocesador x86 dedicado. Sin embargo, en la plataforma x86-64, muchas aplicaciones x86 podrían beneficiarse de una recompilación de 64 bits, debido a los registros adicionales en el código de 64 bits y la compatibilidad garantizada con FPU basada en SSE2, que un compilador puede usar para la optimización. Sin embargo, las aplicaciones que manejan regularmente números enteros de más de 32 bits, como los algoritmos criptográficos, necesitarán una reescritura del código que maneja los números enteros grandes para aprovechar los registros de 64 bits.

Modo heredado

El modo heredado es el modo en el que se encuentra el procesador cuando no está en modo largo. En este modo, el procesador actúa como un procesador x86 antiguo y solo se puede ejecutar código de 16 y 32 bits. El modo heredado permite un máximo de direccionamiento virtual de 32 bits, lo que limita el espacio de direcciones virtuales a 4 GB. Los programas de 64 bits no se pueden ejecutar desde el modo heredado.

Modo protegido

El modo protegido se convierte en un submodo del modo heredado. Es el submodo en el que operan los sistemas operativos de 32 bits y los sistemas operativos de modo protegido de 16 bits cuando se ejecutan en una CPU x86-64.

Modo real

El modo real es el modo de funcionamiento inicial cuando se inicializa el procesador y es un submodo del modo heredado. Es compatible con versiones anteriores de los procesadores Intel 8086 e Intel 8088 originales. El modo real se utiliza principalmente en la actualidad por los cargadores de arranque del sistema operativo, que la arquitectura requiere para configurar los detalles de la memoria virtual antes de pasar a modos superiores. Este modo también lo utiliza cualquier sistema operativo que necesite comunicarse con el firmware del sistema con una interfaz de estilo BIOS tradicional.

Intel 64

Intel 64 es la implementación de Intel de x86-64, utilizada e implementada en varios procesadores fabricados por Intel.

Historia

Históricamente, AMD ha desarrollado y producido procesadores con conjuntos de instrucciones modelados según los diseños originales de Intel, pero con x86-64, los roles se invirtieron: Intel se encontró en la posición de adoptar el ISA que AMD creó como una extensión. a la propia línea de procesadores x86 de Intel.

El proyecto de Intel originalmente tenía el nombre en código Yamhill (después del río Yamhill en el valle Willamette de Oregón). Después de varios años de negar su existencia, Intel anunció en el IDF de febrero de 2004 que el proyecto estaba en marcha. El presidente de Intel en ese momento, Craig Barrett, admitió que este era uno de sus secretos peor guardados.

El nombre de Intel para este conjunto de instrucciones ha cambiado varias veces. El nombre utilizado en las FDI fue CT (presumiblemente para Tecnología Clackamas, otro nombre en clave de un río de Oregón); en cuestión de semanas comenzaron a referirse a él como IA-32e (para extensiones IA-32) y en marzo de 2004 dieron a conocer el "oficial" nombre EM64T (tecnología de memoria extendida 64). A fines de 2006, Intel comenzó a usar el nombre Intel 64 para su implementación, en paralelo con el uso del nombre AMD64 por parte de AMD.

El primer procesador que implementó Intel 64 fue el procesador de múltiples zócalos Xeon con nombre en código Nocona en junio de 2004. Por el contrario, los chips Prescott iniciales (febrero de 2004) no permitían esta función. Posteriormente, Intel comenzó a vender Pentium 4 habilitados para Intel 64 utilizando la revisión E0 del núcleo Prescott, que se vende en el mercado OEM como Pentium 4, modelo F. La revisión E0 también agrega eXecute Disable (XD) (nombre de Intel para el bit NX) a Intel 64, y se ha incluido en el Xeon actual con nombre en código Irwindale. El lanzamiento oficial de Intel de Intel 64 (bajo el nombre EM64T en ese momento) en los procesadores de escritorio convencionales fue el paso N0 Prescott-2M.

El primer procesador móvil de Intel que implementa Intel 64 es la versión Merom del procesador Core 2, que se lanzó el 27 de julio de 2006. Ninguna de las CPU de portátiles anteriores de Intel (Core Duo, Pentium M, Celeron M, Mobile Pentium 4) implementar Intel 64.

Implementaciones

Los procesadores de Intel que implementan la arquitectura Intel64 incluyen el Pentium 4 F-series/5x1 series, 506 y 516, los modelos Celeron D 3x1, 3x6, 355, 347, 352, 360 y 365 y todos los Celeron posteriores, todos los modelos de Xeon desde "Nocona", todos los modelos de procesadores Pentium Dual-Core desde "Merom-2M", Atom 230, 330, D410, D425, D510, D525, N450, N455, N470, N475, N550, N570, N2600 y N2800, todas las versiones de los procesadores Pentium D, Pentium Extreme Edition, Core 2, Core i9, Core i7, Core i5 y Core i3, y los procesadores de la serie Xeon Phi 7200.

X86-S

x86-S es una simplificación planificada de Intel 64 anunciada en mayo de 2023. El nuevo modo eliminaría la compatibilidad con los sistemas operativos de 16 y 32 bits, pero los programas de 32 bits seguirán ejecutándose en un sistema operativo de 64 bits. La CPU ya no arrancaría en modo real de 16 bits, sino que comenzaría directamente en 64 bits. Habrá una forma de cambiar a la paginación de 5 niveles sin pasar por el modo no paginado. Las características eliminadas específicas incluyen:

- Puertas de separación

- Anillo de 32 bits 0

- VT-x ya no emulará esta característica

- Anillos 1 y 2

- Anillo 3 I/O puerto (INTRODUCCIÓN/Fuera.) acceso; véase I/O con mapa por puerto

- Puerto de cuerda I/OINS/Fuera)

- Modo real (incluyendo el modo real enorme), modo protegido de 16 bits, VM86

- Modo de tratamiento de 16 bits

- VT-x ya no proporcionará modo sin restricciones

- Apoyo 8259; el único soporte APIC sería X2APIC

- Algunos bits de modo de sistema operativo no utilizados

Intel cree que el cambio sigue lógicamente después de la eliminación de la puerta A20 en 2008 y el cese de la compatibilidad con SO de 16 bits y 32 bits en el firmware de Intel en 2020. La compatibilidad con los sistemas operativos heredados se lograría a través de la virtualización acelerada por hardware.

Implementación x86-64 de VIA

VIA Technologies presentó su primera implementación de la arquitectura x86-64 en 2008 después de cinco años de desarrollo por parte de su división de CPU, Centaur Technology. Con el nombre en código 'Isaiah', la arquitectura de 64 bits se presentó el 24 de enero de 2008 y se lanzó el 29 de mayo con la marca VIA Nano.

El procesador es compatible con varias extensiones x86 específicas de VIA diseñadas para aumentar la eficiencia en dispositivos de bajo consumo. Se espera que la arquitectura Isaiah sea el doble de rápida en rendimiento de números enteros y cuatro veces más rápida en rendimiento de punto flotante que la generación anterior de VIA Esther a una velocidad de reloj equivalente. También se espera que el consumo de energía esté a la par con las CPU VIA de la generación anterior, con una potencia de diseño térmico que oscila entre 5 W y 25 W. Al ser un diseño completamente nuevo, la arquitectura de Isaiah se creó con soporte para funciones como el conjunto de instrucciones x86-64 y la virtualización x86 que no estaban disponibles en sus predecesores, la línea VIA C7, pero conservando sus extensiones de cifrado.

Niveles de microarquitectura

En 2020, a través de una colaboración entre AMD, Intel, Red Hat y SUSE, se definieron tres niveles de microarquitectura además de la línea de base x86-64: x86-64-v2, x86-64-v3 y x86-64 -v4. Estos niveles definen características específicas a las que los programadores pueden apuntar para proporcionar optimizaciones en tiempo de compilación. Las características expuestas por cada nivel son las siguientes:

| Nivel | Características de la CPU | Ejemplo de instrucción |

|---|---|---|

| x86-64 (también x86-64-v1) (baseline: todas las CPU x86-64) | CMOV | cmov |

| CX8 | cmpxchg8 b | |

| FPU | fld | |

| FXSR | fxsave | |

| MMX | Emms | |

| OSFXSR | fxsave | |

| SCE | syscall | |

| SSE | cvts2si | |

| SSE2 | cvtpi2pd | |

| x86-64-v2 (circa 2009: Nehalem y Jaguar) También:

| CMPXCHG16B | cmpxchg16b |

| LAHF-SAHF | Lahf | |

| POPCNT | popcnt | |

| SSE3 | addsubpd | |

| SSE4_1 | blendpd | |

| SSE4_2 | pcmpestri | |

| SSSE3 | Phaddd | |

| x86-64-v3 (circa 2015: Haswell and Excavator) También:

| AVX | Vzeroall |

| AVX2 | vpermd | |

| BMI1 | andn | |

| BMI2 | bzhi | |

| F16C | vcvtph2ps | |

| FMA | vfmadd132pd | |

| LZCNT | lzcnt | |

| MOVBE | movbe | |

| OSXSAVE | xgetbv | |

| x86-64-v4 (Subconjunto para fines generales de AVX-512)

| AVX512F | kmovw |

| AVX512BW | vdbpsadbw | |

| AVX512CD | vplzcntd | |

| AVX512DQ | vpmullq | |

| AVX512VL | — |

Todos los niveles incluyen funciones que se encuentran en los niveles anteriores. Las extensiones del conjunto de instrucciones que no se relacionan con el cálculo de propósito general, incluidos AES-NI y RDRAND, están excluidas de los requisitos de nivel.

Diferencias entre AMD64 e Intel 64

Aunque son casi idénticos, existen algunas diferencias entre los dos conjuntos de instrucciones en la semántica de algunas instrucciones (o situaciones) de máquina que se utilizan con poca frecuencia y que se utilizan principalmente para la programación de sistemas. Los compiladores generalmente producen ejecutables (es decir, código de máquina) que evitan cualquier diferencia, al menos para los programas de aplicación ordinarios. Por lo tanto, esto es de interés principalmente para los desarrolladores de compiladores, sistemas operativos y similares, que deben tratar con instrucciones de sistema individuales y especiales.

Implementaciones recientes

- Las instrucciones de BSF y BSR de Intel 64 actúan de forma diferente a las de AMD64 cuando la fuente es cero y el tamaño de operación es de 32 bits. El procesador establece la bandera cero y deja sin definir los 32 bits superiores del destino. Tenga en cuenta que Intel documenta que el registro de destino tiene un valor indefinido en este caso, pero en la práctica en silicio implementa el mismo comportamiento que AMD (destinación no modificada). La afirmación separada sobre tal vez no preservar bits en la parte superior 32 no ha sido verificada, pero sólo se ha descartado para Core 2 y Skylake, no todas las microarquitecturas Intel como Pentium 4 de 64 bits o Atom de baja potencia.

- AMD64 requiere un formato de actualización de microcódigos diferente y MSR de control (registros específicos de modelo), mientras que Intel 64 implementa la actualización de microcódigos sin cambios de sus procesadores de sólo 32 bits.

- Intel 64 carece de algunos MSR que se consideran arquitectónicos en AMD64. These include

SYSCFG,TOP_MEM, yTOP_MEM2. - Intel 64 permite

SYSCALL/SYSRETsólo en modo 64-bit (no en modo compatibilidad), y permiteSYSENTER/SYSEXITen ambos modos. AMD64 faltaSYSENTER/SYSEXITen ambos sub-modes de largo modo. - En modo de 64 bits, las ramas cercanas con el prefijo del tamaño de la operación 66H se comportan de manera diferente. Intel 64 ignora este prefijo: la instrucción tiene un signo de 32 bits extendido, y el puntero de instrucción no es truncado. AMD64 utiliza un campo de compensación de 16 bits en la instrucción, y despeja los 48 primeros bits de puntero de instrucción.

- En Intel 64 pero no AMD64, el

REX.Wprefijo se puede utilizar con las instrucciones de punto lejano (LFS,LGS,LSS,JMP FAR,CALL FAR) para aumentar el tamaño de su argumento de puntero lejano a 80 bits (64-bit offset + 16-bit segment). - Los procesadores AMD elevan una Excepción Inválida de punto flotante al realizar una

FLDoFSTPde un NaN de señalización de 80 bits, mientras que los procesadores Intel no lo hacen. - Intel 64 carece de la capacidad de guardar y restaurar una versión reducida (y por lo tanto más rápida) del estado de punto flotante (volviendo la

FXSAVEyFXRSTORinstrucciones). - procesadores AMD desde Opteron Rev. E y Athlon 64 Rev. D han reintroducido soporte limitado para segmentación, a través del bit Limit Enable Long Mode (LMSLE), para facilitar la virtualización de invitados de 64 bits.

- Al regresar a una dirección no canónica utilizando

SYSRET, los procesadores AMD64 ejecutan el controlador de falla de protección general en nivel de privilegio 3, mientras que en los procesadores Intel 64 se ejecuta en nivel de privilegios 0.

Implementaciones anteriores

- Los procesadores AMD64 antes de la Revisión F (distinguidos por el cambio de memoria DDR a DDR2 y las nuevas tomas AM2, F y S1) de 2006 carecían de los

CMPXCHG16Binstrucción, que es una extensión de laCMPXCHG8Binstrucción presente en la mayoría de los procesadores post-80486. Similar aCMPXCHG8B,CMPXCHG16Bpermite operaciones atómicas en octa-palabras (128-bit). Esto es útil para algoritmos paralelos que utilizan comparar y cambiar datos más grandes que el tamaño de un puntero, común en algoritmos libres de bloqueo y sin espera. SinCMPXCHG16Buno debe utilizar soluciones de trabajo, como una sección crítica o enfoques alternativos libres de bloqueo. Su ausencia también evita que Windows de 64 bits antes de Windows 8.1 tenga un espacio de direcciones de usuario más grande que 8 TB. La versión de 64 bits de Windows 8.1 requiere la instrucción. - Early AMD64 e Intel 64 CPUs carecían

LAHFySAHFinstrucciones en modo 64-bit. AMD introdujo estas instrucciones (también en modo 64 bits) con sus procesadores 90 nm (revisión D), comenzando con Athlon 64 en octubre de 2004. Intel introdujo las instrucciones en octubre de 2005 con las revisiones 0F47h y posteriores de NetBurst. La versión de 64 bits de Windows 8.1 requiere esta función. - Early Intel CPUs con Intel 64 también carece de la parte NX de la arquitectura AMD64. Se añadió en el escalón E0 (0F41h) Pentium 4 en octubre de 2004. Esta función es requerida por todas las versiones de Windows 8.

- Las implementaciones de Early Intel 64 tenían un tratamiento físico de memoria de 36 bits (64 GB), mientras que las implementaciones originales de AMD64 tenían un tratamiento físico de 40 bits (1 TB). Intel utilizó el discurso físico de 40 bits primero en Xeon MP (Potomac), lanzado el 29 de marzo de 2005. La diferencia no es una diferencia de las ISA visibles por el usuario. En 2007 AMD 10h-based Opteron fue el primero en proporcionar un espacio de dirección física de 48 bits (256 TB). El tratamiento físico de Intel 64 se extendió a 44 bits (16 TB) en Nehalem-EX en 2010 y a 46 bits (64 TB) en Sandy Bridge E en 2011. Con los procesadores escalables Ice Lake 3rd gen Xeon, Intel aumentó la dirección virtual a 57 bits (128 PB) y física a 52 bits (4 PB) en 2021, lo que requiere una paging de 5 niveles. Al año siguiente AMD64 añadió lo mismo en la cuarta generación EPYC (Genoa). Las CPU no servidores conservan espacios de dirección más pequeños por más tiempo.

Adopción

En las supercomputadoras seguidas por TOP500, la aparición de extensiones de 64 bits para la arquitectura x86 permitió que los procesadores x86 de 64 bits de AMD e Intel reemplazaran la mayoría de las arquitecturas de procesadores RISC que se usaban anteriormente en dichos sistemas (incluidos PA-RISC, SPARC, Alpha y otros), así como x86 de 32 bits, aunque la propia Intel intentó inicialmente sin éxito reemplazar x86 con una nueva arquitectura incompatible de 64 bits en el procesador Itanium.

A partir de 2020, una supercomputadora basada en Fujitsu A64FX llamada Fugaku es la número uno. La primera supercomputadora basada en ARM apareció en la lista en 2018 y, en los últimos años, los coprocesadores de arquitectura sin CPU (GPGPU) también han jugado un papel importante en el rendimiento. Intel's Xeon Phi 'Knights Corner' Los coprocesadores, que implementan un subconjunto de x86-64 con algunas extensiones vectoriales, también se utilizan, junto con los procesadores x86-64, en la supercomputadora Tianhe-2.

Compatibilidad y características del sistema operativo

Los siguientes sistemas operativos y versiones admiten la arquitectura x86-64 en modo largo.

BSD

Libélula BSD

El trabajo de infraestructura preliminar se inició en febrero de 2004 para un puerto x86-64. Este desarrollo luego se estancó. El desarrollo comenzó de nuevo durante julio de 2007 y continuó durante Google Summer of Code 2008 y SoC 2009. El primer lanzamiento oficial que contenía soporte x86-64 fue la versión 2.4.

BSD gratuito

FreeBSD agregó por primera vez compatibilidad con x86-64 con el nombre "amd64" como arquitectura experimental en 5.1-RELEASE en junio de 2003. Se incluyó como arquitectura de distribución estándar a partir de 5.2-RELEASE en enero de 2004. Desde entonces, FreeBSD la ha designado como plataforma de nivel 1. La versión 6.0-RELEASE eliminó algunas peculiaridades con la ejecución de ejecutables x86 en amd64, y la mayoría de los controladores funcionan igual que en la arquitectura x86. Actualmente se está trabajando para integrar más completamente la interfaz binaria de aplicaciones (ABI) x86, de la misma manera que funciona actualmente la compatibilidad con Linux ABI de 32 bits.

NetBSD

La compatibilidad con la arquitectura x86-64 se comprometió por primera vez con el árbol fuente de NetBSD el 19 de junio de 2001. A partir de NetBSD 2.0, lanzado el 9 de diciembre de 2004, NetBSD/amd64 es un sistema completamente integrado y compatible puerto. El código de 32 bits aún se admite en el modo de 64 bits, con una capa de compatibilidad de kernel netbsd-32 para llamadas al sistema de 32 bits. El bit NX se utiliza para proporcionar pilas y pilas no ejecutables con granularidad por página (la granularidad de segmento se utiliza en x86 de 32 bits).

OpenBSD

OpenBSD es compatible con AMD64 desde OpenBSD 3.5, lanzado el 1 de mayo de 2004. La implementación completa en el árbol de la compatibilidad con AMD64 se logró antes del lanzamiento inicial del hardware porque AMD había prestado varias máquinas para el proyecto. s hackathon ese año. Los desarrolladores de OpenBSD han adoptado la plataforma debido a su compatibilidad con el bit NX, lo que permitió una fácil implementación de la función W^X.

El código para el puerto AMD64 de OpenBSD también se ejecuta en los procesadores Intel 64 que contiene el uso clonado de las extensiones AMD64, pero dado que Intel omitió el bit NX de la tabla de páginas en los primeros procesadores Intel 64, no hay capacidad W^X en esas CPU Intel; Los procesadores Intel 64 posteriores agregaron el bit NX con el nombre "bit XD". El multiprocesamiento simétrico (SMP) funciona en el puerto AMD64 de OpenBSD, a partir de la versión 3.6 del 1 de noviembre de 2004.

DOS

Es posible ingresar al modo largo en DOS sin un extensor de DOS, pero el usuario debe regresar al modo real para llamar a las interrupciones de BIOS o DOS.

También es posible ingresar al modo largo con un extensor de DOS similar a DOS/4GW, pero más complejo ya que x86-64 carece del modo 8086 virtual. DOS en sí mismo no es consciente de eso, y no se deben esperar beneficios a menos que se ejecute DOS en una emulación con un backend de controlador de virtualización adecuado, por ejemplo: la interfaz de almacenamiento masivo.

Linux

Linux fue el primer kernel de sistema operativo en ejecutar la arquitectura x86-64 en modo largo, comenzando con la versión 2.4 en 2001 (anterior a la disponibilidad del hardware). Linux también proporciona compatibilidad con versiones anteriores para ejecutar ejecutables de 32 bits. Esto permite que los programas se vuelvan a compilar en modo largo mientras se conserva el uso de programas de 32 bits. Las distribuciones actuales de Linux se envían con kernels y áreas de usuario nativos x86-64. Algunos, como Arch Linux, SUSE, Mandriva y Debian, permiten a los usuarios instalar un conjunto de componentes y bibliotecas de 32 bits cuando se instalan desde un medio de distribución de 64 bits, lo que permite que la mayoría de las aplicaciones de 32 bits existentes se ejecuten junto con las de 64 bits. SO de bits.

x32 ABI (Application Binary Interface), introducido en Linux 3.4, permite que los programas compilados para x32 ABI se ejecuten en el modo de 64 bits de x86-64 mientras solo usan punteros y campos de datos de 32 bits. Aunque esto limita el programa a un espacio de direcciones virtuales de 4 GB, también reduce la huella de memoria del programa y, en algunos casos, puede permitir que se ejecute más rápido.

Linux de 64 bits permite hasta 128 TB de espacio de direcciones virtuales para procesos individuales y puede gestionar aproximadamente 64 TB de memoria física, sujeto a las limitaciones del procesador y del sistema.

MacOS

Mac OS X 10.4.7 y versiones posteriores de Mac OS X 10.4 ejecutan herramientas de línea de comandos de 64 bits mediante POSIX y bibliotecas matemáticas en máquinas basadas en Intel de 64 bits, al igual que todas las versiones de Mac OS X 10.4 y 10.5 ejecútelos en máquinas PowerPC de 64 bits. Ninguna otra biblioteca o marco funciona con aplicaciones de 64 bits en Mac OS X 10.4. El kernel y todas las extensiones del kernel son solo de 32 bits.

Mac OS X 10.5 es compatible con aplicaciones GUI de 64 bits que utilizan Cocoa, Quartz, OpenGL y X11 en máquinas basadas en Intel de 64 bits, así como en máquinas PowerPC de 64 bits. Todas las bibliotecas y marcos que no son GUI también admiten aplicaciones de 64 bits en esas plataformas. El kernel y todas las extensiones del kernel son solo de 32 bits.

Mac OS X 10.6 es la primera versión de macOS compatible con un kernel de 64 bits. Sin embargo, no todas las computadoras de 64 bits pueden ejecutar el kernel de 64 bits, y no todas las computadoras de 64 bits que pueden ejecutar el kernel de 64 bits lo harán de forma predeterminada. El kernel de 64 bits, al igual que el kernel de 32 bits, admite aplicaciones de 32 bits; ambos núcleos también admiten aplicaciones de 64 bits. Las aplicaciones de 32 bits tienen un límite de espacio de direcciones virtuales de 4 GB en cualquiera de los kernels. El kernel de 64 bits no admite extensiones de kernel de 32 bits y el kernel de 32 bits no admite extensiones de kernel de 64 bits.

OS X 10.8 incluye solo el kernel de 64 bits, pero continúa admitiendo aplicaciones de 32 bits; sin embargo, no admite extensiones de kernel de 32 bits.

macOS 10.15 incluye solo el kernel de 64 bits y ya no admite aplicaciones de 32 bits. Esta eliminación del soporte ha presentado un problema para WineHQ (y la versión comercial CrossOver), ya que todavía necesita poder ejecutar aplicaciones de Windows de 32 bits. La solución, denominada wine32on64, fue agregar procesadores que hacen que la CPU entre y salga del modo de compatibilidad de 32 bits en la aplicación nominal de 64 bits.

macOS usa el formato binario universal para empaquetar versiones de 32 y 64 bits del código de la aplicación y la biblioteca en un solo archivo; la versión más adecuada se selecciona automáticamente en el momento de la carga. En Mac OS X 10.6, el formato binario universal también se usa para el kernel y para aquellas extensiones de kernel que admiten kernels de 32 y 64 bits.

Solaris

Solaris 10 y versiones posteriores son compatibles con la arquitectura x86-64.

Para Solaris 10, al igual que con la arquitectura SPARC, solo hay una imagen del sistema operativo, que contiene un kernel de 32 bits y un kernel de 64 bits; esto está etiquetado como "x64/x86" imagen de DVD-ROM. El comportamiento predeterminado es iniciar un kernel de 64 bits, lo que permite ejecutar ejecutables de 64 bits y existentes o nuevos de 32 bits. También se puede seleccionar manualmente un kernel de 32 bits, en cuyo caso solo se ejecutarán los ejecutables de 32 bits. El comando isainfo se puede utilizar para determinar si un sistema ejecuta un kernel de 64 bits.

Para Solaris 11, solo se proporciona el kernel de 64 bits. Sin embargo, el kernel de 64 bits admite ejecutables, bibliotecas y llamadas al sistema de 32 y 64 bits.

Ventanas

Las ediciones x64 del cliente y el servidor de Microsoft Windows (Windows XP Professional x64 Edition y Windows Server 2003 x64 Edition) se lanzaron en marzo de 2005. Internamente, en realidad son la misma compilación (5.2.3790.1830 SP1), ya que comparten la misma fuente binarios base y del sistema operativo, por lo que incluso las actualizaciones del sistema se publican en paquetes unificados, al igual que las ediciones Windows 2000 Professional y Server para x86. Windows Vista, que también tiene muchas ediciones diferentes, se lanzó en enero de 2007. Windows 7 se lanzó en julio de 2009. Windows Server 2008 R2 se vendió solo en ediciones x64 e Itanium; Las versiones posteriores de Windows Server solo ofrecen una edición x64.

Las versiones de Windows para x64 anteriores a Windows 8.1 y Windows Server 2012 R2 ofrecen lo siguiente:

- 8 TB de espacio de dirección virtual por proceso, accesible desde el modo de usuario y el modo kernel, denominado espacio de dirección del modo de usuario. Un programa x64 puede utilizar todo esto, sujeto a límites de la tienda de respaldo en el sistema, y siempre que esté vinculado con la opción "gran dirección consciente", que está presente por defecto. Este es un aumento de 4096 sobre el espacio de dirección virtual de 2 GB predeterminado ofrecido por Windows de 32 bits.

- 8 TB del modo de núcleo espacio de dirección virtual para el sistema operativo. Como con el espacio de dirección del modo de usuario, este es un aumento de 4096 veces más de 32 bits de Windows. El aumento del espacio beneficia principalmente al sistema de archivos cache y el modo kernel "heaps" (la piscina y la piscina de página). Windows sólo utiliza un total de 16 TB de la 256 TB implementada por los procesadores porque los procesadores AMD64 tempranos carecían de un

CMPXCHG16Binstrucción.

En Windows 8.1 y Windows Server 2012 R2, los espacios de direcciones virtuales tanto en modo de usuario como en modo kernel se han ampliado a 128 TB. Estas versiones de Windows no se instalarán en procesadores que carezcan de la instrucción CMPXCHG16B.

Las siguientes características adicionales se aplican a todas las versiones x64 de Windows:

- Capacidad para ejecutar aplicaciones existentes de 32 bits (

.exeprogramas) y bibliotecas dinámicas de enlace (.dlls) utilizando WoW64 si WoW64 es compatible con esa versión. Además, un programa de 32 bits, si estaba relacionado con la opción "grande dirección consciente", puede utilizar hasta 4 GB de espacio de dirección virtual en Windows de 64 bits, en lugar de 2 GB por defecto (opcional 3 GB con/3GBopción de arranque y "gran dirección consciente" opción de enlace) ofrecido por Windows de 32 bits. A diferencia del uso del/3GBopción de arranque en x86, esto no reduce el espacio de dirección virtual del modo kernel disponible para el sistema operativo. Por lo tanto, las aplicaciones de 32 bits pueden beneficiarse de ejecutarse en x64 Windows, incluso si no se recompilan para x86-64. - Tanto las aplicaciones de 32- y 64-bit, si no están vinculadas con "gran dirección consciente", se limitan a 2 GB de espacio de direcciones virtuales.

- Capacidad para utilizar hasta 128 GB (Windows XP/Vista), 192 GB (Windows 7), 512 GB (Windows 8), 1 TB (Windows Server 2003), 2 TB (Windows Server 2008/Windows 10), 4 TB (Windows Server 2012), o 24 TB (Windows Server 2016/2019) de memoria física de acceso aleatorio (RAM).

- Modelo de datos LLP64: en C/C++, "int" y "long" tipos son 32 bits de ancho, "long long" es de 64 bits, mientras que los punteros y los tipos derivados de punteros son 64 bits de ancho.

- Los controladores de dispositivo de modo Kernel deben ser versiones de 64 bits; no hay manera de ejecutar ejecutables de modo de kernel de 32 bits dentro del sistema operativo de 64 bits. Los controladores de dispositivo de modo de usuario pueden ser de 32 bits o 64 bits.

- Las aplicaciones de Windows de 16 bits (Win16) y DOS no se ejecutarán en versiones x86-64 de Windows debido a la eliminación del subsistema de máquinas DOS virtual (NTVDM) que se basó en la capacidad de utilizar el modo 8086 virtual. El modo 8086 virtual no puede entrar mientras se ejecuta en modo largo.

- Aplicación completa de la función de protección de páginas NX (No Ejecutar). Esto también se implementa en versiones recientes de 32 bits de Windows cuando se inician en modo PAE.

- En lugar de descriptor del segmento FS en versiones x86 de la familia NT de Windows, el descriptor del segmento GS se utiliza para apuntar a dos estructuras definidas del sistema operativo: Bloque de información de lectura (NT_TIB) en modo de usuario y Región de control del procesador (KPCR) en modo del núcleo. Así, por ejemplo, en modo de usuario

GS:0es la dirección del primer miembro del Thread Information Block. Mantener esta convención hizo el puerto x86-64 más fácil, pero requirió AMD para mantener la función de los segmentos de FS y GS en el modo largo – aunque se segmentó el tratamiento per se no es realmente utilizado por ningún sistema operativo moderno. - Los informes iniciales afirmaron que el programador del sistema operativo no ahorraría y restauraría el estado de la máquina x87 FPU a través de los interruptores del contexto del hilo. El comportamiento observado muestra que este no es el caso: el estado x87 es salvado y restaurado, excepto para los hilos solo del kernel (una limitación que existe en la versión de 32 bits también). La documentación más reciente disponible de Microsoft indica que el x87/MMX/3DNow! las instrucciones se pueden utilizar en modo largo, pero que están deprecatadas y pueden causar problemas de compatibilidad en el futuro. (3DNow! ya no está disponible en procesadores AMD, con excepción de los

PREFETCHyPREFETCHWinstrucciones, que también son compatibles con procesadores Intel como de Broadwell.) - Algunos componentes como Jet Database Engine y Data Access Objects no serán portados a arquitecturas de 64 bits como x86-64 e IA-64.

- Microsoft Visual Studio puede compilar aplicaciones nativas para apuntar la arquitectura x86-64, que sólo puede ejecutarse en Microsoft Windows de 64 bits, o la arquitectura IA-32, que puede funcionar como una aplicación de 32 bits en Microsoft Windows de 32 bits o Microsoft Windows de 64 bits en el modo de emulación WoW64. Las aplicaciones administradas se pueden compilar en modos IA-32, x86-64 o AnyCPU. El software creado en los dos primeros modos se comporta como sus contrapartes de código nativo IA-32 o x86-64 respectivamente; Al utilizar el modo AnyCPU, sin embargo, las aplicaciones en versiones de 32 bits de Microsoft Windows funcionan como aplicaciones de 32 bits, mientras que funcionan como una aplicación de 64 bits en ediciones de 64 bits de Microsoft Windows.

Consolas de videojuegos

Tanto PlayStation 4 como Xbox One, y todas las variantes de esas consolas, incorporan procesadores AMD x86-64, basados en la microarquitectura de Jaguar. El firmware y los juegos están escritos en código x86-64; no se trata de un código x86 heredado.

La generación actual, PlayStation 5 y Xbox Series X y Series S respectivamente, también incorporan procesadores AMD x86-64, basados en la microarquitectura Zen 2.

Aunque se considera una PC, Steam Deck utiliza una unidad de procesamiento acelerado (APU) AMD x86-64 personalizada, basada en la microarquitectura Zen 2.

Convenciones de nomenclatura de la industria

Dado que AMD64 e Intel 64 son sustancialmente similares, muchos productos de software y hardware utilizan un término independiente del proveedor para indicar su compatibilidad con ambas implementaciones. La designación original de AMD para esta arquitectura de procesador, "x86-64", todavía se usa para este propósito, al igual que la variante "x86_64". Otras empresas, como Microsoft y Sun Microsystems/Oracle Corporation, utilizan la contracción "x64" en material de marketing.

El término IA-64 se refiere al procesador Itanium y no debe confundirse con x86-64, ya que es un conjunto de instrucciones completamente diferente.

Muchos sistemas operativos y productos, especialmente aquellos que introdujeron la compatibilidad con x86-64 antes de la entrada de Intel en el mercado, utilizan el término "AMD64" o "amd64" para referirse tanto a AMD64 como a Intel 64.

- amd64

- La mayoría de los sistemas BSD como FreeBSD, MidnightBSD, NetBSD y OpenBSD se refieren tanto a AMD64 como a Intel 64 bajo el nombre de arquitectura "amd64".

- Algunas distribuciones de Linux como Debian, Ubuntu, Gentoo Linux se refieren tanto a AMD64 como a Intel 64 bajo el nombre de arquitectura "amd64".

- Las versiones x64 de Microsoft Windows utilizan el monitor AMD64 internamente para designar varios componentes que utilizan o son compatibles con esta arquitectura. Por ejemplo, la variable entorno PROCESSOR_ARCHITECTURE se asigna el valor "AMD64" en comparación con "x86" en versiones de 32 bits, y el directorio del sistema en una instalación de Windows x64 Edition CD-ROM se llama "AMD64", en contraste con "i386" en versiones de 32 bits.

- Sol de Solaris isalista comando identifica los sistemas basados en AMD64 e Intel 64 como "amd64".

- Java Development Kit (JDK): el nombre "amd64" se utiliza en nombres de directorios que contienen archivos x86-64.

- x86_64

- El núcleo Linux y la colección de compiladores GNU se refieren a la arquitectura de 64 bits como "x86_64".

- Algunas distribuciones de Linux, como Fedora, openSUSE, Arch Linux, Gentoo Linux se refieren a esta arquitectura de 64 bits como "x86_64".

- Apple macOS se refiere a la arquitectura de 64 bits como "x86-64" o "x86_64", como se ve en el comando Terminal

archy en su documentación de desarrolladores. - Breaking with most other BSD systems, Dragon Fly BSD se refiere a la arquitectura de 64 bits como "x86_64".

- Haiku se refiere a la arquitectura de 64 bits como "x86_64".

Licencias

x86-64/AMD64 fue desarrollado exclusivamente por AMD. AMD posee patentes sobre técnicas utilizadas en AMD64; esas patentes deben tener licencia de AMD para poder implementar AMD64. Intel celebró un acuerdo de licencias cruzadas con AMD, otorgando licencias a AMD para sus patentes sobre técnicas x86 existentes y otorgando licencias a AMD para sus patentes sobre técnicas utilizadas en x86-64. En 2009, AMD e Intel resolvieron varias demandas y desacuerdos sobre licencias cruzadas, extendiendo sus acuerdos de licencias cruzadas.

Contenido relacionado

Vóxel

Emulador de terminal

Blitz BÁSICO