X86

x86 (también conocido como 80x86 o la familia 8086) es una familia de arquitecturas de conjunto de instrucciones de computadora de conjunto de instrucciones complejas (CISC) inicialmente desarrollado por Intel basado en el microprocesador Intel 8086 y su variante 8088. El 8086 se introdujo en 1978 como una extensión completa de 16 bits del microprocesador 8080 de 8 bits de Intel, con la segmentación de memoria como una solución para direccionar más memoria de la que puede cubrir una dirección simple de 16 bits. El término "x86" surgió porque los nombres de varios sucesores del procesador 8086 de Intel terminan en '86', incluidos los procesadores 80186, 80286, 80386 y 80486.

El término no es sinónimo de compatibilidad con PC de IBM, ya que implica una multitud de otros hardware informáticos. Los sistemas integrados y las computadoras de propósito general usaban chips x86 antes de que comenzara el mercado compatible con PC, algunos de ellos antes del debut de IBM PC (1981).

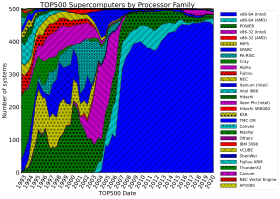

A partir de junio de 2022, la mayoría de las computadoras de escritorio y portátiles vendidas se basan en la familia de arquitectura x86, mientras que las categorías móviles, como los teléfonos inteligentes o las tabletas, están dominadas por ARM. En el extremo superior, x86 continúa dominando los segmentos de computación en la nube y estaciones de trabajo de computación intensiva. La supercomputadora más rápida en la lista TOP500 de junio de 2022 fue el primer sistema a exaescala, Frontier, construido con CPU AMD Epyc basadas en x86 ISA; rompió la barrera de 1 exaFLOPS en mayo de 2022.

Resumen

En la década de 1980 y principios de la de 1990, cuando el 8088 y el 80286 todavía eran de uso común, el término x86 generalmente representaba cualquier CPU compatible con 8086. Hoy, sin embargo, x86 generalmente implica una compatibilidad binaria también con el conjunto de instrucciones de 32 bits del 80386. Esto se debe al hecho de que este conjunto de instrucciones se ha convertido en el mínimo común denominador para muchos sistemas operativos modernos y probablemente también porque el El término se volvió común después de la introducción del 80386 en 1985.

Unos años después de la introducción del 8086 y el 8088, Intel agregó algo de complejidad a su esquema de nombres y terminología como el "iAPX" del ambicioso pero desafortunado procesador Intel iAPX 432 se probó en la familia de chips 8086 más exitosa, aplicada como una especie de prefijo a nivel de sistema. Un sistema 8086, que incluye coprocesadores como 8087 y 8089, y chips de sistema específicos de Intel más simples, se describió como un sistema iAPX 86. También había términos iRMX (para sistemas operativos), iSBC (para computadoras de placa única) e iSBX (para placas multimódulo basadas en el 8086-architecture), todos juntos bajo el título Microsystem 80. Sin embargo, este esquema de nombres fue bastante temporal y duró algunos años a principios de la década de 1980.

Aunque el 8086 se desarrolló principalmente para sistemas integrados y computadoras pequeñas multiusuario o de un solo usuario, en gran parte como respuesta al exitoso Zilog Z80 compatible con 8080, la línea x86 pronto creció en funciones y potencia de procesamiento. Hoy en día, x86 es omnipresente en computadoras personales estacionarias y portátiles, y también se usa en computadoras de gama media, estaciones de trabajo, servidores y la mayoría de los nuevos clústeres de supercomputadoras de la lista TOP500. Una gran cantidad de software, incluida una gran lista de sistemas operativos x86, utilizan hardware basado en x86.

Sin embargo, el x86 moderno es relativamente poco común en los sistemas integrados, y las aplicaciones pequeñas de bajo consumo (que usan baterías diminutas) y los mercados de microprocesadores de bajo costo, como los electrodomésticos y los juguetes, carecen de una presencia significativa de x86. Las arquitecturas simples basadas en 8 y 16 bits son comunes aquí, así como arquitecturas RISC más simples como RISC-V, aunque VIA C7 compatible con x86, VIA Nano, Geode de AMD, Athlon Neo e Intel Atom son ejemplos de Diseños de 32 y 64 bits utilizados en algunos segmentos de relativamente bajo consumo y bajo costo.

Ha habido varios intentos, incluso por parte de Intel, de acabar con el dominio del mercado de los "poco elegantes" Arquitectura x86 diseñada directamente a partir de los primeros microprocesadores simples de 8 bits. Ejemplos de esto son iAPX 432 (un proyecto originalmente llamado Intel 8800), Intel 960, Intel 860 y la arquitectura Intel/Hewlett-Packard Itanium. Sin embargo, el refinamiento continuo de las microarquitecturas x86, los circuitos y la fabricación de semiconductores dificultaría la sustitución de x86 en muchos segmentos. La extensión x86 de 64 bits de AMD (a la que Intel finalmente respondió con un diseño compatible) y la escalabilidad de los chips x86 en forma de modernas CPU multinúcleo, destaca x86 como un ejemplo de cómo el refinamiento continuo de los los estándares de la industria pueden resistir la competencia de arquitecturas completamente nuevas.

Cronología

La siguiente tabla enumera los modelos de procesadores y las series de modelos que implementan varias arquitecturas en la familia x86, en orden cronológico. Cada elemento de línea se caracteriza por diseños de microarquitectura de procesador significativamente mejorados o comercialmente exitosos.

| Era | Introducción | Modelos CPU prominentes | Address space | Características notables | |||

|---|---|---|---|---|---|---|---|

| Linear | Virtual | Física | |||||

| x86-16 | 1a | 1978 | Intel 8086, Intel 8088 (1979) | 16-bit | NA | 20-bit | 16-bit ISA, IBM PC (8088), IBM PC/XT (8088) |

| 1982 | Intel 80186, Intel 80188 NEC V20/V30 (1983) | 8086-2 ISA, incrustada (80186/80188) | |||||

| 2a | Intel 80286 y clones | 30-bit | 24-bit | modo protegido, IBM PC/XT 286, IBM PC/AT | |||

| IA-32 | 3a | 1985 | Intel 80386, AMD Am386 (1991) | 32-bit | 46-bit | 32-bit | 32-bit ISA, paging, IBM PS/2 |

| 4a (pipelining, cache) | 1989 | Intel 80486 Cyrix Cx486S, DLC (1992) AMD Am486 (1993), Am5x86 (1995) | pipelining, on-die x87 FPU (486DX), on-die cache | ||||

| 5a (Superscalar) | 1993 | Intel Pentium, Pentium MMX (1996) | Superscalar, 64-bit databus, más rápido FPU, MMX (Pentium MMX), APIC, SMP | ||||

| 1994 | NexGen Nx586 AMD 5k86/K5 (1996) | Microarquitectura discreta (μ-op traducción) | |||||

| 1995 | Cyrix Cx5x86 Cyrix 6x86/MX (1997)/MII (1998) | Ejecución dinámica | |||||

| 6a (PAE, μ-op traducción) | 1995 | Intel Pentium Pro | 36-bit (PAE) | μ-op traducción, instrucciones de movimiento condicional, ejecución dinámica, ejecución especulativa, 3-way x86 superscalar, superscalar FPU, PAE, caché L2 en chip | |||

| 1997 | Intel Pentium II, Pentium III (1999) Celeron (1998), Xeon (1998) | on-package (Pentium II) o on-die (Celeron) L2 Cache, SSE (Pentium III), Slot 1, Socket 370 o Slot 2 (Xeon) | |||||

| 1997 | AMD K6/K6-2 (1998)/K6-III (1999) | 32-bit | 3DNow!, sistema de caché de 3 niveles (K6-III) | ||||

| Plataforma mejorada | 1999 | AMD Athlon Athlon XP/MP (2001) Duron (2000) Sempron (2004) | 36-bit | MMX+, 3DNow!+, autobús doble bomba, Ranura A o Socket A | |||

| 2000 | Transmeta Crusoe | 32-bit | CMS procesador de plataforma x86, núcleo VLIW-128, controlador de memoria on-die, lógica de puente PCI | ||||

| Pentium Intel 4 | 36-bit | SSE2, HTT (Northwood), NetBurst, quad-pumped bus, Trace Cache, Socket 478 | |||||

| 2003 | Intel Pentium M Intel Core (2006) Pentium Dual-Core (2007) | μ-op fusión, bit XD (Dothan) (Intel Core "Yonah") | |||||

| Transmeta Efficeon | CMS 6.0.4, VLIW-256, NX bit, HT | ||||||

| IA-64 | Transición de 64 bits 1999-2005 | 2001 | Intel Itanium (2001-2017) | 52-bit | Arquitectura EPIC de 64 bits, paquete de instrucciones VLIW de 128 bits, hardware en-die IA-32 H/W que permite aplicaciones x86 OSes y x86 (generaciones iniciales), software IA-32 EL habilitando aplicaciones x86 (Itanium 2), Los archivos de registro de itanio se remapped a x86 registros | ||

| x86-64 | 64-bit Extended desde 2001 | x86-64 es la arquitectura extendida de 64 bits de x86, su modo Legacy preserva toda la arquitectura x86 sin alterar. La arquitectura nativa de procesadores x86-64: residente en el Modo de 64 bits, falta de modo de acceso en segmentación, presentando espacio de dirección lineal de 64 bits arquitectónico-permitir; una arquitectura IA-32 adaptada que reside en el Modo de Compatibilidad junto con el Modo de 64 bits se proporciona para apoyar la mayoría de las aplicaciones x86 | |||||

| 2003 | Athlon 64/FX/X2 (2005), Opteron Sempron (2004)/X2 (2008) Turión 64 (2005)/X2 (2006) | 40-bit | AMD64 (excepto algunos procesadores Sempron presentados como procesadores puramente x86), controlador de memoria on-die, HyperTransport, on-die dual-core (X2), AMD-V (Athlon 64 Orleans), Socket 754/939/940 o AM2 | ||||

| 2004 | Pentium 4 (Prescott) Celeron D, Pentium D (2005) | 36-bit | EM64T (disponible en modelos seleccionados de Pentium 4 y Celeron D), SSE3, 2o gen. NetBurst pipelining, dual-core (on-die: Pentium D 8xx, on-chip: Pentium D 9xx), Intel VT(Pentium 4 6x2), socket LGA 775 | ||||

| 2006 | Intel Core 2 Pentium Dual-Core (2007) Celeron Dual-Core (2008) | Intel 64 (realizados== EM64T), SSSE3(65 nm), ejecución dinámica amplia, fusión μ-op, fusión macro-op en modo 16-bit y 32-bit, quad-core on-chip(Core 2 Quad), Smart Shared L2 Cache (Intel Core 2 "Merom") | |||||

| 2007 | AMD Phenom/II (2008) Athlon II (2009) Turión II (2009) | 48-bit | Cuadrícula monolítica (X4)/triple-core (X3), SSE4a, Índice de Virtualización RVI, HyperTransport 3, AM2+ o AM3 | ||||

| 2008 | Intel Core 2 (45 nm) | 40-bit | SSE4.1 | ||||

| Intel Atom | netbook o procesador de dispositivo inteligente de baja potencia, núcleo P54C reutilizado | ||||||

| Intel Core i7 Core i5 (2009) Core i3 (2010) | QuickPath, on-chip GMCH (Clarkdale), SSE4.2, Extended Page Tables (EPT) para la virtualización, macro-op fusión en modo 64-bit, (Intel Xeon "Bloomfield" con Nehalem microarquitectura) | ||||||

| VIA Nano | encriptación basada en hardware; gestión de potencia adaptativa | ||||||

| 2010 | AMD FX | 48-bit | octa-core, CMT(Clustered Multi-Thread), FMA, OpenCL, AM3+ | ||||

| 2011 | AMD APU A y E Series (Llano) | 40-bit | on-die GPGPU, PCI Express 2.0, Socket FM1 | ||||

| AMD APU C, E y Z Series (Bobcat) | 36-bit | dispositivo inteligente de baja potencia APU | |||||

| Intel Core i3, Core i5 y Core i7 (Puente Sandy / Puente Ivy) | Conexión de anillo interno, caché de μ-op decodificado, toma LGA 1155 | ||||||

| 2012 | AMD APU A Series (Bulldozer, Trinity y más tarde) | 48-bit | AVX, APU basada en Bulldozer, Socket FM2 o Socket FM2+ | ||||

| Intel Xeon Phi (Knights Corner) | Coprocesador de tarjeta PCI-E para sistema basado en XEON, Manycore Chip, P54C en el orden, VPU muy ancho (512-bit SSE), instrucciones LRBni (8× 64-bit) | ||||||

| 2013 | AMD Jaguar (Athlon, Sempron) | SoC, consola de juego y procesador de dispositivo inteligente de baja potencia | |||||

| Intel Silvermont (Atom, Celeron, Pentium) | 36-bit | SoC, procesador de dispositivo inteligente de baja potencia/ultra-low | |||||

| Intel Core i3, Core i5 y Core i7 (Haswell/Broadwell) | 39-bit | Instrucciones AVX2, FMA3, TSX, BMI1, y BMI2, LGA 1150 socket | |||||

| 2015 | Intel Broadwell-U (Intel Core i3, Core i5, Core i7, Core M, Pentium, Celeron) | SoC, on-chip Broadwell-U PCH-LP (Multi-chip module) | |||||

| 2015-2020 | Intel Skylake/Kaby Lake/Cannon Lake/Coffee Lake/Rocket Lake (Intel Pentium/Celeron Gold, Core i3, Core i5, Core i7, Core i9) | 46-bit | AVX-512 (restricted to Cannon Lake-U and workstation/server variations of Skylake) | ||||

| 2016 | Intel Xeon Phi (Knights Landing) | 48-bit | Manycore CPU and coprocessor for Xeon systems, Airmont (Atom) based core | ||||

| 2016 | AMD Bristol Ridge (AMD (Pro) A6/A8/A10/A12) | FCH integrado en die, SoC, toma de AM4 | |||||

| 2017 | AMD Ryzen Series/AMD Epyc Series | Implementación de AMD SMT, en chip múltiples mueres | |||||

| 2017 | Zhaoxin WuDaoKou (KX-5000, KH-20000) | La primera arquitectura x86-64 de Zhaoxin | |||||

| 2018-2021 | Intel Sunny Cove (Ice Lake-U y Y), Cypress Cove (Rocket Lake) | 57-bit | La primera implementación de Intel de AVX-512 para el segmento de consumo. Addition of Vector Neural Network Instructions (VNNI) | ||||

| 2020 | Intel Willow Cove (Tiger Lake-Y/U/H) | Arquitectura de interconexión de doble anillo, actualizado Gaussian Neural Accelerator (GNA2), nuevas Instrucciones de Intersección Vector AVX-512, adición de Tecnología de Control-Flow Enforcement (CET) | |||||

| 2021 | Intel Alder Lake | Diseño híbrido con rendimiento (Golden Cove) y núcleos de eficiencia (Gracemont), soporte para PCIe Gen5 y DDR5, actualizado Gaussian Neural Accelerator (GNA3) | |||||

| Era | Introducción | Modelos CPU prominentes | Address space | Características notables | |||

Historia

Diseñadores y fabricantes

En varios momentos, empresas como IBM, VIA, NEC, AMD, TI, STM, Fujitsu, OKI, Siemens, Cyrix, Intersil, C&T, NexGen, UMC y DM&P comenzaron a diseñar o fabricar x86 procesadores (CPU) destinados a computadoras personales y sistemas integrados. Otras empresas que diseñaron o fabricaron procesadores x86 o x87 incluyen ITT Corporation, National Semiconductor, ULSI System Technology y Weitek.

Tales implementaciones x86 rara vez eran copias simples, pero a menudo empleaban diferentes microarquitecturas internas y diferentes soluciones a nivel electrónico y físico. Naturalmente, los primeros microprocesadores compatibles eran de 16 bits, mientras que los diseños de 32 bits se desarrollaron mucho más tarde. Para el mercado de las computadoras personales, las cantidades reales comenzaron a aparecer alrededor de 1990 con procesadores compatibles i386 e i486, a menudo con nombres similares a los chips originales de Intel.

Después del i486 completamente canalizado, en 1993 Intel presentó la marca Pentium (que, a diferencia de los números, podría ser una marca registrada) para su nuevo conjunto de diseños x86 superescalares. Con el esquema de nombres x86 legalmente aprobado, otros proveedores de x86 tuvieron que elegir diferentes nombres para sus productos compatibles con x86, e inicialmente algunos optaron por continuar con variaciones del esquema de numeración: IBM se asoció con Cyrix para producir el 5x86 y luego el muy eficiente Líneas 6x86 (M1) y 6x86MX (MII) de diseños Cyrix, que fueron los primeros microprocesadores x86 que implementaron el cambio de nombre de registro para permitir la ejecución especulativa.

Mientras tanto, AMD diseñó y fabricó el avanzado pero retrasado 5k86 (K5), que, internamente, se basaba en gran medida en el diseño RISC de 29K anterior de AMD; Al igual que el Nx586 de NexGen, utilizó una estrategia en la que las etapas de canalización dedicadas decodifican las instrucciones x86 en microoperaciones uniformes y fáciles de manejar, un método que sigue siendo la base para la mayoría de los diseños x86 hasta el día de hoy.

Algunas de las primeras versiones de estos microprocesadores tenían problemas de disipación de calor. El 6x86 también se vio afectado por algunos problemas menores de compatibilidad, el Nx586 carecía de una unidad de punto flotante (FPU) y (la entonces crucial) compatibilidad con pines, mientras que el K5 tuvo un rendimiento un tanto decepcionante cuando se introdujo (eventualmente).

La ignorancia de los clientes sobre las alternativas a la serie Pentium contribuyó aún más a que estos diseños fueran comparativamente infructuosos, a pesar de que el K5 tenía muy buena compatibilidad con Pentium y el 6x86 era significativamente más rápido que el Pentium en código entero. Más tarde, AMD logró convertirse en un competidor serio con el conjunto de procesadores K6, que dio paso a los muy exitosos Athlon y Opteron.

También hubo otros competidores, como Centaur Technology (anteriormente IDT), Rise Technology y Transmeta. Tecnologías VIA' Los procesadores C3 y C7 de bajo consumo, que fueron diseñados por la empresa Centaur, se vendieron durante muchos años después de su lanzamiento en 2005. El diseño de Centaur de 2008, el VIA Nano, fue su primer procesador con ejecución superescalar y especulativa. Se introdujo casi al mismo tiempo (en 2008) cuando Intel presentó el Intel Atom, su primer dispositivo "en orden" procesador posterior al P5 Pentium.

Se han agregado muchas adiciones y extensiones al conjunto de instrucciones x86 original a lo largo de los años, casi de manera consistente con total compatibilidad con versiones anteriores. La familia de arquitectura se ha implementado en procesadores de Intel, Cyrix, AMD, VIA Technologies y muchas otras empresas; también existen implementaciones abiertas, como la plataforma Zet SoC (actualmente inactiva). Sin embargo, de ellos, solo Intel, AMD, VIA Technologies y DM&P Electronics tienen licencias de arquitectura x86, y de estos, solo los dos primeros producen activamente diseños modernos de 64 bits, lo que lleva a lo que se ha llamado " duopolio" de Intel y AMD en procesadores x86.

Sin embargo, en 2014, la empresa china con sede en Shanghai Zhaoxin, una empresa conjunta entre una empresa china y VIA Technologies, comenzó a diseñar procesadores x86 basados en VIA para computadoras de escritorio y portátiles. El lanzamiento de su nuevo "7" la familia de procesadores x86 (p. ej., KX-7000), que no son tan rápidos como los chips AMD o Intel pero siguen siendo lo último en tecnología, se había planificado para 2021; Sin embargo, a marzo de 2022 no se había producido el lanzamiento.

De arquitectura de 16 y 32 bits a 64 bits

La arquitectura del conjunto de instrucciones se ha ampliado dos veces a un tamaño de palabra mayor. En 1985, Intel lanzó el 80386 de 32 bits (más tarde conocido como i386) que reemplazó gradualmente a los chips anteriores de 16 bits en las computadoras (aunque generalmente no en los sistemas integrados) durante los años siguientes; este modelo de programación extendido se denominó originalmente la arquitectura i386 (como su primera implementación), pero Intel más tarde lo denominó IA-32 al presentar su arquitectura (no relacionada) IA-64.

Entre 1999 y 2003, AMD amplió esta arquitectura de 32 bits a 64 bits y se refirió a ella como x86-64 en los primeros documentos y luego como AMD64. Intel pronto adoptó las extensiones arquitectónicas de AMD con el nombre IA-32e, más tarde usando el nombre EM64T y finalmente Intel 64. Microsoft y Sun Microsystems/Oracle también usan el término "x64", mientras que muchas distribuciones de Linux, y los BSD también usan el "amd64" término. Microsoft Windows, por ejemplo, designa sus versiones de 32 bits como "x86" y las versiones de 64 bits como "x64", mientras que los archivos de instalación de las versiones de Windows de 64 bits deben colocarse en un directorio llamado "AMD64".

Propiedades básicas de la arquitectura

La arquitectura x86 es una instrucción de longitud variable, principalmente "CISC" diseño con énfasis en la compatibilidad con versiones anteriores. Sin embargo, el conjunto de instrucciones no es el típico CISC, sino básicamente una versión extendida de las arquitecturas simples 8008 y 8080 de ocho bits. El direccionamiento de bytes está habilitado y las palabras se almacenan en la memoria con un orden de bytes little-endian. Se permite el acceso a la memoria a direcciones no alineadas para casi todas las instrucciones. El tamaño nativo más grande para números enteros aritméticos y direcciones de memoria (o compensaciones) es de 16, 32 o 64 bits según la generación de la arquitectura (los procesadores más nuevos también incluyen soporte directo para números enteros más pequeños). Se pueden manejar múltiples valores escalares simultáneamente a través de la unidad SIMD presente en generaciones posteriores, como se describe a continuación. Las compensaciones de direccionamiento inmediato y los datos inmediatos pueden expresarse como cantidades de 8 bits para los casos o contextos que ocurren con frecuencia donde un rango de -128 a 127 es suficiente. Por lo tanto, las instrucciones típicas tienen una longitud de 2 o 3 bytes (aunque algunas son mucho más largas y otras son de un solo byte).

Para conservar aún más el espacio de codificación, la mayoría de los registros se expresan en códigos de operación usando tres o cuatro bits, este último a través de un prefijo de código de operación en modo de 64 bits, mientras que como máximo un operando de una instrucción puede ser una ubicación de memoria. Sin embargo, este operando de memoria también puede ser el destino (o un origen combinado y destino), mientras que el otro operando, el origen, puede ser ya sea registro o inmediato. Entre otros factores, esto contribuye a un tamaño de código que compite con las máquinas de ocho bits y permite un uso eficiente de la memoria caché de instrucciones. El número relativamente pequeño de registros generales (también heredados de sus ancestros de 8 bits) ha hecho que el direccionamiento relativo al registro (usando pequeños desplazamientos inmediatos) sea un método importante para acceder a los operandos, especialmente en la pila. Por lo tanto, se ha invertido mucho trabajo en hacer que dichos accesos sean tan rápidos como los accesos de registro, es decir, un rendimiento de instrucción de un ciclo, en la mayoría de las circunstancias donde los datos accedidos están disponibles en el caché de nivel superior.

Coma flotante y SIMD

Se desarrolló un procesador de coma flotante dedicado con registros internos de 80 bits, el 8087, para el 8086 original. Este microprocesador se convirtió posteriormente en el 80387 ampliado, y los procesadores posteriores incorporaron una versión compatible con versiones anteriores de esta funcionalidad en el mismo microprocesador. como procesador principal. Además de esto, los diseños x86 modernos también contienen una unidad SIMD (ver SSE a continuación) donde las instrucciones pueden funcionar en paralelo en (una o dos) palabras de 128 bits, cada una con dos o cuatro números de coma flotante (cada uno de 64 o 32). bits de ancho respectivamente), o alternativamente, 2, 4, 8 o 16 enteros (cada uno de 64, 32, 16 u 8 bits de ancho respectivamente).

La presencia de registros SIMD anchos significa que los procesadores x86 existentes pueden cargar o almacenar hasta 128 bits de datos de memoria en una sola instrucción y también realizar operaciones bit a bit (aunque no aritmética de enteros) en cantidades completas de 128 bits en paralelo. Los procesadores Sandy Bridge de Intel agregaron las instrucciones Advanced Vector Extensions (AVX), ampliando los registros SIMD a 256 bits. Las instrucciones Intel Initial Many Core implementadas por los procesadores Knights Corner Xeon Phi y las instrucciones AVX-512 implementadas por los procesadores Knights Landing Xeon Phi y los procesadores Skylake-X utilizan registros SIMD de 512 bits de ancho.

Implementaciones actuales

Durante la ejecución, los procesadores x86 actuales emplean algunos pasos de decodificación adicionales para dividir la mayoría de las instrucciones en partes más pequeñas llamadas microoperaciones. Luego, estos se entregan a una unidad de control que los almacena en búfer y los programa de acuerdo con la semántica x86 para que puedan ser ejecutados, en parte en paralelo, por una de varias unidades de ejecución (más o menos especializadas). Estos diseños x86 modernos son, por lo tanto, canalizados, superescalares y también capaces de ejecución fuera de orden y especulativa (a través de predicción de bifurcación, cambio de nombre de registro y predicción de dependencia de memoria), lo que significa que pueden ejecutar varias instrucciones x86 (parciales o completas) simultáneamente, y no necesariamente en el mismo orden dado en el flujo de instrucciones. Algunas CPU Intel (Xeon Foster MP, algunos Pentium 4 y algunos Nehalem y procesadores Intel Core posteriores) y AMD CPU (a partir de Zen) también son capaces de multiproceso simultáneo con dos subprocesos por núcleo (Xeon Phi tiene cuatro subprocesos por núcleo). Algunas CPU Intel admiten memoria transaccional (TSX).

Cuando se introdujo, a mediados de la década de 1990, este método a veces se denominaba "núcleo RISC" o como "traducción RISC", en parte por razones de marketing, pero también porque estas microoperaciones comparten algunas propiedades con ciertos tipos de instrucciones RISC. Sin embargo, el microcódigo tradicional (utilizado desde la década de 1950) también comparte inherentemente muchas de las mismas propiedades; el nuevo método difiere principalmente en que la traducción a microoperaciones ahora ocurre de forma asincrónica. No tener que sincronizar las unidades de ejecución con los pasos de decodificación abre posibilidades para un mayor análisis del flujo de código (en búfer) y, por lo tanto, permite la detección de operaciones que se pueden realizar en paralelo, alimentando simultáneamente más de una unidad de ejecución.

Los últimos procesadores también hacen lo contrario cuando corresponde; combinan ciertas secuencias x86 (como una comparación seguida de un salto condicional) en una microoperación más compleja que se ajusta mejor al modelo de ejecución y, por lo tanto, se puede ejecutar más rápido o con menos recursos de máquina involucrados.

Otra forma de intentar mejorar el rendimiento es almacenar en caché las microoperaciones decodificadas, de modo que el procesador pueda acceder directamente a las microoperaciones decodificadas desde una memoria caché especial, en lugar de decodificarlas nuevamente. Intel siguió este enfoque con la función Execution Trace Cache en su microarquitectura NetBurst (para procesadores Pentium 4) y más tarde en Decoded Stream Buffer (para procesadores de la marca Core desde Sandy Bridge).

Transmeta usó un método completamente diferente en sus CPU compatibles con Crusoe x86. Utilizaron la traducción justo a tiempo para convertir las instrucciones x86 al conjunto de instrucciones VLIW nativas de la CPU. Transmeta argumentó que su enfoque permite diseños más eficientes desde el punto de vista energético, ya que la CPU puede prescindir del complicado paso de decodificación de las implementaciones x86 más tradicionales.

Modos de direccionamiento

Los modos de direccionamiento para modos de procesador de 16 bits se pueden resumir mediante la fórmula:

- CS:DS:SS:ES:()[BXBP]+[SIDI])+displacement{fnh} {fnh} {fnh} {fnh} {fnh} {fnh} {\fn}\fn}fn}fnh} {fn}fnh} {fn} {fnh} {f}fnfnh}f}fnh}f}f}fnh}}f}fnh} {fnh}f}f}f}f}f}fnh}f}fnh}fn}}f}fnh}f}f}f}f}fn}f}fnh}fnhnh}c}cH00} {fnh}fnh}fn}fn}cH0}fnh}cccH00}cH00}fnh}fn} {}fn}\\\\\\\fnK}\\fnK}\\\\\\fn}\\\\\\\\fn}\\\\fn}\\\\\\\\\\\\\\\\\\\\fn}\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ {displacement}}

Los modos de direccionamiento para los modos de procesador x86 de 32 bits se pueden resumir mediante la fórmula:

- CS:DS:SS:ES:FS:GS:[EAXEBXECXEDXESPEBPESIEDI]+()[EAXEBXECXEDXEBPESIEDI]Alternativa Alternativa [1248])+displacement{fnMittt {}:\\fnK}:\\\fnhtt {fnh}:\\\\\\\\\\shnhttt}:\\\\\\cHFF}\cH00}fnKfn}fnKfn}}fnKfnKfn}}fn}fnKfnKfnKfnKfnKfnKfnKfnKfnKfn}}}}}}}}}}fnKfn}}}}fn}fn}}fnfnKfnKfnKfnKfnKfnKfnKfnKfnKfnKfnKfn}}}}}}}}}} {fn} {fn} {fn} {fn} {fn}}} {fn}} {fn}} {fn}} {fn}}fn} {fn} {fn} {fn}}}} {fn}}}}}}} {f}}}}} {f} {f} {f}f}}}}}}}}}}}}f}}}}}}}}}}} {f} {f}}}}}f}f} {f} {f}}}f}}}}}}}}}}}}}}}}}}}}}}}}}}}}}}}}}}}}}}}}}} {f}}}}}}}}}} {f} {f} {f} {f} {f}}f}}}}}f}}}}}}}}}} {displacement}}

Los modos de direccionamiento para el modo de procesador de 64 bits se pueden resumir mediante la fórmula:

- {}FS:GS:[⋮ ⋮ GPR⋮ ⋮ ]+()[⋮ ⋮ GPR⋮ ⋮ ]Alternativa Alternativa [1248])RIP}+displacement{displaystyle {begin{begin{begin{matrix}{mathttt} {fnMicrosoft Sans Serif} {begin{bmatrix}vdots {fnMitt {fnMicrosoft Sans Serif}+{begin{pmatrix}\\\begin{bmatrix}vdots {fnh}\fnh}\cH00}fn}fn}\m}\mcH00\\cH00\\cH33}\\cH00}\m\cH00\\\\cH00}\cH00}\m}m}\mm}m}m}m}\m}m}m}\mmcH00}cH00}cH00}cH00}cH00}cH00}cH00}cH00}cH00}\\cH00}\cH00}cH00}\cH00}cH00}cH00}cH00}cH00}cH00}cH00}cH00}cH00}cH00}cH00}cH00} {displacement}}

El direccionamiento relativo de instrucciones en código de 64 bits (RIP + desplazamiento, donde RIP es el registro de puntero de instrucción) simplifica la implementación de código independiente de la posición (como se usa en bibliotecas compartidas en algunos sistemas operativos).

El 8086 tenía 64 KB de ocho bits (o alternativamente 32 palabras K de 16 bits) espacio de E/S y 64 KB (un segmento) pila en la memoria compatible con el hardware de la computadora. Solo las palabras (dos bytes) se pueden empujar a la pila. La pila crece hacia direcciones numéricamente más bajas, con SS:SP apuntando al elemento enviado más recientemente. Hay 256 interrupciones, que pueden ser invocadas tanto por hardware como por software. Las interrupciones pueden conectarse en cascada, utilizando la pila para almacenar la dirección de retorno.

Registros X86

16 bits

Los Intel 8086 y 8088 originales tienen catorce registros de 16 bits. Cuatro de ellos (AX, BX, CX, DX) son registros de propósito general (GPR), aunque cada uno puede tener un propósito adicional; por ejemplo, solo CX puede usarse como contador con la instrucción loop. Se puede acceder a cada uno como dos bytes separados (por lo tanto, se puede acceder al byte alto de BX como BH y al byte bajo como BL). Dos registros de puntero tienen funciones especiales: SP (puntero de pila) apunta al "superior" de la pila, y BP (puntero base) a menudo se usa para apuntar a algún otro lugar de la pila, normalmente por encima de las variables locales (ver puntero de marco). Los registros SI, DI, BX y BP son registros de direcciones y también se pueden usar para la indexación de matrices.

Se utilizan cuatro registros de segmento (CS, DS, SS y ES) para formar una dirección de memoria. El registro FLAGS contiene banderas como la bandera de acarreo, la bandera de desbordamiento y la bandera cero. Finalmente, el puntero de instrucción (IP) apunta a la siguiente instrucción que se obtendrá de la memoria y luego se ejecutará; este registro no puede ser accedido directamente (leído o escrito) por un programa.

Intel 80186 y 80188 son esencialmente una CPU 8086 u 8088 mejorada, respectivamente, con periféricos en chip agregados, y tienen los mismos registros de CPU que 8086 y 8088 (además de los registros de interfaz para los periféricos).

El 8086, 8088, 80186 y 80188 pueden usar un coprocesador de punto flotante opcional, el 8087. El 8087 aparece para el programador como parte de la CPU y agrega ocho registros de 80 bits de ancho, st(0) a st (7), cada uno de los cuales puede contener datos numéricos en uno de siete formatos: punto flotante de 32, 64 u 80 bits, entero (binario) de 16, 32 o 64 bits y empaquetado de 80 bits entero decimal. También tiene su propio registro de estado de 16 bits accesible a través de la instrucción fntsw, y es común usar simplemente algunos de sus bits para ramificar copiándolos en las BANDERAS normales.

En Intel 80286, para admitir el modo protegido, tres registros especiales contienen direcciones de tablas de descriptores (GDTR, LDTR, IDTR) y un cuarto registro de tareas (TR) se usa para el cambio de tareas. El 80287 es el coprocesador de coma flotante del 80286 y tiene los mismos registros que el 8087 con los mismos formatos de datos.

32 bits

Con la llegada del procesador 80386 de 32 bits, los registros de uso general, los registros base, los registros de índice, el puntero de instrucción y el registro FLAGS de 16 bits, pero no los registros de segmento, se ampliaron a 32 bits. La nomenclatura representaba esto con el prefijo "E" (para "extendido") a los nombres de registro en lenguaje ensamblador x86. Así, el registro AX corresponde a los 16 bits inferiores del nuevo registro EAX de 32 bits, SI corresponde a los 16 bits inferiores de ESI, y así sucesivamente. Los registros de propósito general, los registros base y los registros de índice se pueden usar como base en los modos de direccionamiento, y todos esos registros, excepto el puntero de pila, se pueden usar como índice en los modos de direccionamiento.

Se agregaron dos nuevos registros de segmento (FS y GS). Con un mayor número de registros, instrucciones y operandos, se amplió el formato del código máquina. Para proporcionar compatibilidad con versiones anteriores, los segmentos con código ejecutable se pueden marcar para que contengan instrucciones de 16 bits o de 32 bits. Los prefijos especiales permiten la inclusión de instrucciones de 32 bits en un segmento de 16 bits o viceversa.

El 80386 tenía un coprocesador de coma flotante opcional, el 80387; tenía ocho registros de 80 bits de ancho: st(0) a st(7), como el 8087 y el 80287. El 80386 también podía usar un coprocesador 80287. Con el 80486 y todos los modelos x86 posteriores, la unidad de procesamiento de coma flotante (FPU) está integrada en el chip.

El Pentium MMX agregó ocho registros vectoriales enteros MMX de 64 bits (MM0 a MM7, que comparten bits inferiores con la pila FPU de 80 bits de ancho). Con el Pentium III, Intel agregó un registro de control/estado (MXCSR) de Streaming SIMD Extensions (SSE) de 32 bits y ocho registros de punto flotante SSE de 128 bits (XMM0 a XMM7).

64 bits

Comenzando con el procesador AMD Opteron, la arquitectura x86 amplió los registros de 32 bits a registros de 64 bits de manera similar a como se llevó a cabo la extensión de 16 a 32 bits. Un prefijo R (para "registro") identifica los registros de 64 bits (RAX, RBX, RCX, RDX, RSI, RDI, RBP, RSP, RFLAGS, RIP), y también se introdujeron ocho registros generales adicionales de 64 bits (R8–R15) en la creación de x86-64. Además, se agregaron ocho registros vectoriales SSE más (XMM8–XMM15). Sin embargo, estas extensiones solo se pueden usar en el modo de 64 bits, que es uno de los dos modos que solo están disponibles en el modo largo. Los modos de direccionamiento no cambiaron drásticamente desde el modo de 32 bits, excepto que el direccionamiento se amplió a 64 bits, las direcciones virtuales ahora se extienden a 64 bits (para no permitir los bits de modo en las direcciones virtuales) y otros detalles del selector se redujeron drásticamente. Además, se agregó un modo de direccionamiento para permitir referencias de memoria relativas a RIP (el puntero de instrucción), para facilitar la implementación de código independiente de la posición, utilizado en bibliotecas compartidas en algunos sistemas operativos.

128 bits

SIMD registra XMM0–XMM15 (XMM0–XMM31 cuando se admite AVX-512).

256 bits

SIMD registra YMM0–YMM15 (YMM0–YMM31 cuando se admite AVX-512). La mitad inferior de cada uno de los registros YMM se asigna al registro XMM correspondiente.

512 bits

Registros SIMD ZMM0–ZMM31. La mitad inferior de cada uno de los registros ZMM se asigna al registro YMM correspondiente.

Varios/fines especiales

Los procesadores x86 que tienen un modo protegido, es decir, los procesadores 80286 y posteriores, también tienen tres registros descriptores (GDTR, LDTR, IDTR) y un registro de tareas (TR).

Los procesadores x86 de 32 bits (a partir del 80386) también incluyen varios registros especiales/misceláneos, como registros de control (CR0 a 4, CR8 solo para 64 bits), registros de depuración (DR0 a 3, más 6 y 7), registros de prueba (TR3 a 7; solo 80486) y registros específicos del modelo (MSR, que aparecen con el Pentium).

AVX-512 tiene ocho registros de máscara adicionales de 64 bits K0–K7 para seleccionar elementos en un registro vectorial. Según el registro vectorial y los anchos de los elementos, una instrucción dada solo puede usar un subconjunto de bits del registro de máscara.

Propósito

Aunque los registros principales (con la excepción del puntero de instrucción) son de "propósito general" en las versiones de 32 bits y 64 bits del conjunto de instrucciones y se puede usar para cualquier cosa, originalmente se previó que se usarían para los siguientes propósitos:

- AL/AH/AX/EAX/RAX: Acumulador

- CL/CH/CX/ECX/RCX: Contrata (para uso con bucles y cuerdas)

- DL/DH/DX/EDX/RDX: Extender la precisión del acumulador (por ejemplo, combinar 32 bits EAX y EDX para operaciones de entero de 64 bits en código de 32 bits)

- BL/BH/BX/EBX/RBX: Índice de base (para uso con arrays)

- SP/ESP/RSP: puntero para la dirección superior de la pila.

- BP/EBP/RBP: puntero base para sostener la dirección del marco de pila actual.

- SI/ESI/RSI: Índice de fuentes para operaciones de cadena.

- DI/EDI/RDI: Índice de destino para operaciones de cadena.

- IP/EIP/RIP: Indicador de instrucciones. Tiene el contador del programa, la dirección de la siguiente instrucción.

Registros de segmento:

- CS: Código

- DS: Datos

- SS: Stack

- ES: Datos extras

- FS: Datos extras #2

- GS: Datos extras #3

No se previeron propósitos particulares para los otros 8 registros disponibles solo en modo de 64 bits.

Algunas instrucciones se compilan y ejecutan de manera más eficiente cuando se usan estos registros para el propósito para el que fueron diseñadas. Por ejemplo, usar AL como un acumulador y agregarle un valor de byte inmediato produce el eficiente código de operación add to AL de 04h, mientras que usar el registro BL produce el genérico y más largo add to register código de operación de 80C3h. Otro ejemplo es la división y multiplicación de doble precisión que funciona específicamente con los registros AX y DX.

Los compiladores modernos se beneficiaron de la introducción del byte sib (scale-index-base byte) que permite que los registros se traten de manera uniforme (como una minicomputadora). Sin embargo, usar el byte sib universalmente no es óptimo, ya que produce codificaciones más largas que solo usarlo de forma selectiva cuando es necesario. (El principal beneficio del byte sib es la ortogonalidad y los modos de direccionamiento más potentes que proporciona, lo que hace posible guardar instrucciones y el uso de registros para cálculos de direcciones, como escalar un índice). Algunas instrucciones especiales perdieron prioridad en el diseño del hardware. y se volvió más lento que las secuencias de código pequeñas equivalentes. Un ejemplo notable es la instrucción LODSW.

Estructura

| 64 | 56 | 48 | 40 | 32 | 24 | 16 | 8 |

|---|---|---|---|---|---|---|---|

| ¿R?X | |||||||

| ¿E?X | |||||||

| ? X | |||||||

| ? H | ? L | ||||||

| 64 | 56 | 48 | 40 | 32 | 24 | 16 | 8 |

|---|---|---|---|---|---|---|---|

| ? | |||||||

| ? D | |||||||

| ? W | |||||||

| ? B | |||||||

| 16 | 8 |

|---|---|

| ? S | |

| 64 | 56 | 48 | 40 | 32 | 24 | 16 | 8 |

|---|---|---|---|---|---|---|---|

| ¿R?P | |||||||

| ¿E?P | |||||||

| ? P | |||||||

| ? PL | |||||||

Nota: Los registros ?PL solo están disponibles en el modo de 64 bits.

| 64 | 56 | 48 | 40 | 32 | 24 | 16 | 8 |

|---|---|---|---|---|---|---|---|

| ¿R? I | |||||||

| ¿E? I | |||||||

| ? I | |||||||

| ? IL | |||||||

Nota: Los registros ?IL solo están disponibles en el modo de 64 bits.

| 64 | 56 | 48 | 40 | 32 | 24 | 16 | 8 |

|---|---|---|---|---|---|---|---|

| RIP | |||||||

| EIP | |||||||

| IP | |||||||

Modos de funcionamiento

Modo real

El modo de dirección real, comúnmente llamado modo real, es un modo operativo de CPU 8086 y posteriores compatibles con x86. El modo real se caracteriza por un espacio de direcciones de memoria segmentado de 20 bits (lo que significa que solo se puede direccionar un poco más de 1 MiB de memoria), acceso directo de software a hardware periférico y ningún concepto de protección de memoria o multitarea a nivel de hardware. Todas las CPU x86 de la serie 80286 y posteriores se inician en modo real al encenderse; Las CPU 80186 y anteriores tenían solo un modo operativo, que es equivalente al modo real en chips posteriores. (En la plataforma de PC de IBM, el acceso de software directo a las rutinas del BIOS de IBM está disponible solo en modo real, ya que el BIOS está escrito para el modo real. Sin embargo, esto no es una propiedad de la CPU x86 sino del diseño del BIOS de IBM).

Para usar más de 64 KB de memoria, se deben usar los registros de segmento. Esto creó grandes complicaciones para los implementadores del compilador que introdujeron modos de puntero extraños como 'cerca', 'lejos'. y "enorme" para aprovechar la naturaleza implícita de la arquitectura segmentada en diferentes grados, con algunos punteros que contienen desplazamientos de 16 bits dentro de segmentos implícitos y otros punteros que contienen direcciones de segmento y desplazamientos dentro de segmentos. Es técnicamente posible usar hasta 256 KB de memoria para código y datos, con hasta 64 KB para código, configurando los cuatro registros de segmento una vez y luego solo usando compensaciones de 16 bits (opcionalmente con prefijos de anulación de segmento predeterminado) para direccionar la memoria, pero esto pone restricciones sustanciales en la forma en que se pueden direccionar los datos y se pueden combinar los operandos de la memoria, y viola la intención arquitectónica de los diseñadores de Intel, que es que los elementos de datos separados (por ejemplo, matrices, estructuras, unidades de código) sean contenidos en segmentos separados y direccionados por sus propias direcciones de segmento, en nuevos programas que no están portados desde procesadores anteriores de 8 bits con espacios de direcciones de 16 bits.

Modo irreal

El modo irreal lo utilizan algunos sistemas operativos de 16 bits y algunos cargadores de arranque de 32 bits.

Modo de gestión del sistema

El modo de administración del sistema (SMM) solo lo usa el firmware del sistema (BIOS/UEFI), no los sistemas operativos ni el software de aplicaciones. El código SMM se ejecuta en SMRAM.

Modo protegido

Además del modo real, Intel 80286 admite el modo protegido, expandiendo la memoria física direccionable a 16 MB y la memoria virtual direccionable a 1 GB, y brinda memoria protegida, lo que evita que los programas se dañen entre sí. Esto se hace utilizando los registros de segmento solo para almacenar un índice en una tabla de descriptores que se almacena en la memoria. Hay dos tablas de este tipo, la tabla de descriptores globales (GDT) y la tabla de descriptores locales (LDT), cada una de las cuales contiene hasta 8192 descriptores de segmento, y cada segmento da acceso a 64 KB de memoria. En el 80286, un descriptor de segmento proporciona una dirección base de 24 bits y esta dirección base se agrega a un desplazamiento de 16 bits para crear una dirección absoluta. La dirección base de la tabla cumple el mismo rol que cumple el valor literal del registro del segmento en modo real; los registros de segmento se han convertido de registros directos a registros indirectos. A cada segmento se le puede asignar uno de los cuatro niveles de anillo utilizados para la seguridad informática basada en hardware. Cada descriptor de segmento también contiene un campo de límite de segmento que especifica el desplazamiento máximo que se puede usar con el segmento. Debido a que las compensaciones son de 16 bits, los segmentos todavía están limitados a 64 KB cada uno en el modo protegido 80286.

Cada vez que se carga un registro de segmento en modo protegido, el 80286 debe leer un descriptor de segmento de 6 bytes de la memoria en un conjunto de registros internos ocultos. Por lo tanto, la carga de registros de segmento es mucho más lenta en modo protegido que en modo real, y se debe evitar cambiar de segmento con mucha frecuencia. Las operaciones de memoria reales que usan segmentos en modo protegido no se ralentizan mucho porque el 80286 y posteriores tienen hardware para verificar el desplazamiento contra el límite del segmento en paralelo con la ejecución de instrucciones.

Intel 80386 extendió las compensaciones y también el campo de límite de segmento en cada descriptor de segmento a 32 bits, lo que permite que un segmento abarque todo el espacio de memoria. También introdujo soporte en modo protegido para paginación, un mecanismo que hace posible usar memoria virtual paginada (con un tamaño de página de 4 KB). La paginación permite que la CPU asigne cualquier página del espacio de memoria virtual a cualquier página del espacio de memoria física. Para hacer esto, utiliza tablas de mapeo adicionales en la memoria llamadas tablas de páginas. El modo protegido en el 80386 puede funcionar con paginación habilitada o deshabilitada; el mecanismo de segmentación siempre está activo y genera direcciones virtuales que luego son mapeadas por el mecanismo de paginación si está habilitado. El mecanismo de segmentación también se puede deshabilitar de manera efectiva configurando todos los segmentos para que tengan una dirección base de 0 y un límite de tamaño igual a todo el espacio de direcciones; esto también requiere una tabla de descriptores de segmento de tamaño mínimo de solo cuatro descriptores (ya que no es necesario utilizar los segmentos FS y GS).

La paginación se utiliza ampliamente en los sistemas operativos multitarea modernos. Linux, 386BSD y Windows NT se desarrollaron para el 386 porque fue la primera CPU de arquitectura Intel que admitía paginación y compensaciones de segmento de 32 bits. La arquitectura 386 se convirtió en la base de todo el desarrollo posterior de la serie x86.

Los procesadores x86 que admiten el modo protegido se inician en modo real para lograr compatibilidad con versiones anteriores de la clase de procesadores 8086 más antigua. Al encender (también conocido como arranque), el procesador se inicializa en modo real y luego comienza a ejecutar instrucciones. El código de inicio del sistema operativo, que puede almacenarse en la memoria de solo lectura, puede colocar el procesador en el modo protegido para habilitar la paginación y otras funciones). no aplicar en modo protegido. Por el contrario, la aritmética de segmentos, una práctica común en código de modo real, no está permitida en modo protegido.

Modo virtual 8086

También hay un submodo de operación en modo protegido de 32 bits (también conocido como modo protegido 80386) llamado modo virtual 8086, también conocido como modo V86. Básicamente, se trata de un modo operativo híbrido especial que permite ejecutar programas y sistemas operativos en modo real bajo el control de un sistema operativo supervisor en modo protegido. Esto permite una gran flexibilidad en la ejecución simultánea de programas en modo protegido y programas en modo real. Este modo está disponible exclusivamente para la versión de 32 bits del modo protegido; no existe en la versión de 16 bits del modo protegido, ni en el modo largo.

Modo largo

A mediados de la década de 1990, era evidente que el espacio de direcciones de 32 bits de la arquitectura x86 limitaba su rendimiento en aplicaciones que requerían grandes conjuntos de datos. Un espacio de direcciones de 32 bits permitiría al procesador abordar directamente solo 4 GB de datos, un tamaño superado por aplicaciones como el procesamiento de video y los motores de bases de datos. Con direcciones de 64 bits, es posible abordar directamente 16 EiB de datos, aunque la mayoría de las arquitecturas de 64 bits no admiten el acceso al espacio completo de direcciones de 64 bits; por ejemplo, AMD64 solo admite 48 bits de una dirección de 64 bits, divididos en cuatro niveles de paginación.

En 1999, AMD publicó una especificación (casi) completa para una extensión de 64 bits de la arquitectura x86 a la que llamaron x86-64 con la intención de producirla. Ese diseño se usa actualmente en casi todos los procesadores x86, con algunas excepciones destinadas a sistemas integrados.

Los chips x86-64 producidos en masa para el mercado general estuvieron disponibles cuatro años más tarde, en 2003, después de que se dedicó el tiempo a probar y refinar los prototipos en funcionamiento; casi al mismo tiempo, el nombre inicial x86-64 se cambió a AMD64. El éxito de la línea de procesadores AMD64 junto con la tibia recepción de la arquitectura IA-64 obligó a Intel a lanzar su propia implementación del conjunto de instrucciones AMD64. Intel había implementado previamente la compatibilidad con AMD64, pero optó por no habilitarla con la esperanza de que AMD no lanzara AMD64 al mercado antes de que se adoptara ampliamente el nuevo conjunto de instrucciones IA-64 de Itanium. Denominó su implementación de AMD64 como EM64T y luego la renombró como Intel 64.

En su literatura y nombres de versiones de productos, Microsoft y Sun se refieren a AMD64/Intel 64 colectivamente como x64 en los sistemas operativos Windows y Solaris. Las distribuciones de Linux se refieren a él como "x86-64", su variante "x86_64" o "amd64". Los sistemas BSD utilizan "amd64" mientras que macOS usa "x86_64".

El modo largo es principalmente una extensión del conjunto de instrucciones de 32 bits, pero a diferencia de la transición de 16 a 32 bits, muchas instrucciones se eliminaron en el modo de 64 bits. Esto no afecta la compatibilidad inversa binaria real (que ejecutaría el código heredado en otros modos que conservan el soporte para esas instrucciones), pero cambia la forma en que deben funcionar el ensamblador y los compiladores para el código nuevo.

Esta fue la primera vez que una extensión importante de la arquitectura x86 fue iniciada y originada por un fabricante que no sea Intel. También fue la primera vez que Intel aceptó una tecnología de esta naturaleza de una fuente externa.

Extensiones

Unidad de coma flotante

Los primeros procesadores x86 podían ampliarse con hardware de punto flotante en forma de una serie de coprocesadores numéricos de punto flotante con nombres como 8087, 80287 y 80387, abreviado x87. Esto también se conocía como NPX (Extensión del procesador numérico), un nombre adecuado ya que los coprocesadores, aunque se usaban principalmente para cálculos de coma flotante, también realizaban operaciones con números enteros en formatos binarios y decimales. Con muy pocas excepciones, el 80486 y los procesadores x86 posteriores integraron esta funcionalidad x87 en el chip, lo que hizo que las instrucciones x87 fueran una parte integral de facto del conjunto de instrucciones x86.

Cada registro x87, conocido como ST(0) a ST(7), tiene 80 bits de ancho y almacena números en el formato de precisión extendida doble estándar de punto flotante IEEE. Estos registros están organizados como una pila con ST(0) en la parte superior. Esto se hizo para conservar el espacio del código de operación y, por lo tanto, los registros son accesibles aleatoriamente solo para cualquiera de los operandos en una instrucción de registro a registro; ST0 siempre debe ser uno de los dos operandos, ya sea el origen o el destino, independientemente de si el otro operando es ST(x) o un operando de memoria. Sin embargo, se puede obtener acceso aleatorio a los registros de la pila a través de una instrucción que intercambia cualquier ST(x) especificado por ST(0).

Las operaciones incluyen funciones aritméticas y trascendentales, incluidas funciones trigonométricas y exponenciales, e instrucciones que cargan constantes comunes (como 0, 1, e, la base del logaritmo natural, log2(10) y log10(2)) en uno de los registros de la pila. Si bien la capacidad de números enteros a menudo se pasa por alto, el x87 puede operar con números enteros más grandes con una sola instrucción que el 8086, 80286, 80386 o cualquier CPU x86 sin extensiones de 64 bits, y cálculos enteros repetidos incluso en valores pequeños (por ejemplo, 16 bits) se puede acelerar ejecutando instrucciones de enteros en la CPU x86 y x87 en paralelo. (La CPU x86 sigue funcionando mientras el coprocesador x87 calcula, y el x87 envía una señal al x86 cuando finaliza o interrumpe el x86 si necesita atención debido a un error).

MMX

MMX es un conjunto de instrucciones SIMD diseñado por Intel e introducido en 1997 para el microprocesador Pentium MMX. El conjunto de instrucciones MMX se desarrolló a partir de un concepto similar utilizado por primera vez en Intel i860. Es compatible con la mayoría de los procesadores IA-32 posteriores de Intel y otros proveedores. MMX se usa típicamente para el procesamiento de video (en aplicaciones multimedia, por ejemplo).

MMX agregó 8 nuevos registros a la arquitectura, conocidos como MM0 a MM7 (en adelante, MMn). En realidad, estos nuevos registros eran solo alias para los registros de pila FPU x87 existentes. Por lo tanto, cualquier cosa que se hiciera en la pila de coma flotante también afectaría a los registros MMX. A diferencia de la pila FP, estos registros MMn eran fijos, no relativos y, por lo tanto, eran accesibles aleatoriamente. El conjunto de instrucciones no adoptó la semántica similar a la pila, por lo que los sistemas operativos existentes aún podían guardar y restaurar correctamente el estado del registro cuando se realizaban múltiples tareas sin modificaciones.

Cada uno de los registros MMn son números enteros de 64 bits. Sin embargo, uno de los conceptos principales del conjunto de instrucciones MMX es el concepto de tipos de datos empaquetados, lo que significa que en lugar de usar el registro completo para un solo entero de 64 bits (palabra cuádruple), uno puede usarlo contener dos enteros de 32 bits (doble palabra), cuatro enteros de 16 bits (palabra) u ocho enteros de 8 bits (byte). Dado que los registros MMn de 64 bits del MMX tienen un alias en la pila FPU y cada uno de los registros de punto flotante tiene 80 bits de ancho, los 16 bits superiores de los registros de punto flotante no se utilizan en MMX. Cualquier instrucción MMX establece todos estos bits en unos, lo que corresponde a la representación de punto flotante de NaN o infinitos.

¡3D ahora!

En 1997, AMD presentó 3DNow!. La introducción de esta tecnología coincidió con el auge de las aplicaciones de entretenimiento en 3D y se diseñó para mejorar el rendimiento del procesamiento de vectores de la CPU de las aplicaciones con uso intensivo de gráficos. Los desarrolladores de videojuegos 3D y los proveedores de hardware de gráficos 3D utilizan 3DNow! para mejorar su rendimiento en las series de procesadores K6 y Athlon de AMD.

¡3D ahora! fue diseñado para ser la evolución natural de MMX de números enteros a punto flotante. Como tal, utiliza exactamente la misma convención de nomenclatura de registros que MMX, es decir, MM0 a MM7. La única diferencia es que en lugar de empaquetar números enteros en estos registros, se empaquetan dos números de punto flotante de precisión simple en cada registro. La ventaja de crear alias en los registros FPU es que las mismas instrucciones y estructuras de datos utilizadas para guardar el estado de los registros FPU también se pueden usar para guardar 3DNow! registrar estados. Por lo tanto, no es necesario realizar modificaciones especiales en los sistemas operativos que, de otro modo, no conocerían.

SSE y AVX

En 1999, Intel introdujo el conjunto de instrucciones Streaming SIMD Extensions (SSE), seguido en 2000 con SSE2. La primera adición permitió la descarga de operaciones básicas de punto flotante de la pila x87 y la segunda hizo que MMX quedara casi obsoleto y permitió que las instrucciones fueran dirigidas de manera realista por los compiladores convencionales. Presentado en 2004 junto con la revisión de Prescott del procesador Pentium 4, SSE3 agregó memoria específica e instrucciones de manejo de subprocesos para mejorar el rendimiento de la tecnología HyperThreading de Intel. AMD obtuvo la licencia del conjunto de instrucciones SSE3 e implementó la mayoría de las instrucciones SSE3 para sus procesadores Athlon 64 de revisión E y posteriores. El Athlon 64 no es compatible con HyperThreading y carece de las instrucciones SSE3 que se usan solo para HyperThreading.

SSE descartó todas las conexiones heredadas a la pila FPU. Esto también significó que este conjunto de instrucciones descartó todas las conexiones heredadas a generaciones anteriores de conjuntos de instrucciones SIMD como MMX. Pero liberó a los diseñadores, permitiéndoles usar registros más grandes, sin estar limitados por el tamaño de los registros FPU. Los diseñadores crearon ocho registros de 128 bits, denominados XMM0 a XMM7. (Nota: en AMD64, la cantidad de registros SSE XMM aumentó de 8 a 16). Sin embargo, la desventaja era que los sistemas operativos tenían que conocer este nuevo conjunto de instrucciones para poder guardar sus estados de registro. Entonces, Intel creó una versión ligeramente modificada del modo protegido, llamada modo mejorado, que permite el uso de instrucciones SSE, mientras que permanecen deshabilitadas en el modo protegido normal. Un sistema operativo que es consciente de SSE activará el modo mejorado, mientras que un sistema operativo que no lo sepa solo entrará en el modo protegido tradicional.

SSE es un conjunto de instrucciones SIMD que solo funciona en valores de punto flotante, como 3DNow!. Sin embargo, a diferencia de 3DNow! corta toda la conexión heredada a la pila FPU. Debido a que tiene registros más grandes que 3DNow!, SSE puede empaquetar el doble de flotadores de precisión simples en sus registros. El SSE original estaba limitado a números de precisión simple, como 3DNow!. El SSE2 también introdujo la capacidad de empaquetar números de doble precisión, que 3DNow! no tenía posibilidad de hacerlo ya que un número de doble precisión tiene un tamaño de 64 bits, que sería el tamaño completo de un solo 3DNow! registro MMn. A 128 bits, los registros SSE XMMn podrían empaquetar dos flotadores de doble precisión en un registro. Por lo tanto, SSE2 es mucho más adecuado para cálculos científicos que SSE1 o 3DNow!, que estaban limitados a una sola precisión. SSE3 no introduce ningún registro adicional.

Advanced Vector Extensions (AVX) duplicó el tamaño de los registros SSE a registros YMM de 256 bits. También introdujo el esquema de codificación VEX para adaptarse a los registros más grandes, además de algunas instrucciones para permutar elementos. AVX2 no introdujo registros adicionales, pero se destacó por la adición de instrucciones de enmascaramiento, recopilación y reproducción aleatoria.

AVX-512 presenta otra expansión a 32 registros ZMM de 512 bits y un nuevo esquema EVEX. A diferencia de sus predecesores que presentan una extensión monolítica, se divide en muchos subconjuntos que los modelos específicos de CPU pueden optar por implementar.

Extensión de dirección física (PAE)

La Extensión de dirección física o PAE se agregó por primera vez en Intel Pentium Pro y, más tarde, AMD en los procesadores Athlon, para permitir la dirección de hasta 64 GB de RAM. Sin PAE, la memoria RAM física en modo protegido de 32 bits suele estar limitada a 4 GB. PAE define una estructura de tabla de páginas diferente con entradas de tabla de páginas más amplias y un tercer nivel de tabla de páginas, lo que permite bits adicionales de dirección física. Aunque las implementaciones iniciales en los procesadores de 32 bits teóricamente admitían hasta 64 GB de RAM, el conjunto de chips y otras limitaciones de la plataforma a menudo restringían lo que realmente se podía usar. Los procesadores x86-64 definen estructuras de tablas de páginas que teóricamente permiten hasta 52 bits de dirección física, aunque nuevamente, el chipset y otras preocupaciones de la plataforma (como la cantidad de ranuras DIMM disponibles y la RAM máxima posible por DIMM) evitan una dirección física tan grande espacio a realizar. En los procesadores x86-64, el modo PAE debe estar activo antes de cambiar al modo largo y debe permanecer activo mientras el modo largo está activo, por lo que mientras está en modo largo no hay ningún mensaje "no PAE" modo. El modo PAE no afecta el ancho de las direcciones lineales o virtuales.

X86-64

Para la década de 2000, los procesadores x86 de 32 bits' los límites en el direccionamiento de la memoria eran un obstáculo para su uso en clústeres informáticos de alto rendimiento y potentes estaciones de trabajo de escritorio. El viejo x86 de 32 bits competía con arquitecturas RISC de 64 bits mucho más avanzadas que podían manejar mucha más memoria. Intel y todo el ecosistema x86 necesitaban direccionamiento de memoria de 64 bits para que x86 sobreviviera a la era informática de 64 bits, ya que las aplicaciones de software de estaciones de trabajo y de escritorio pronto comenzarían a alcanzar los límites del direccionamiento de memoria de 32 bits. Sin embargo, Intel sintió que era el momento adecuado para dar un paso audaz y utilizar la transición a las computadoras de escritorio de 64 bits para alejarse de la arquitectura x86 en general, un experimento que finalmente fracasó.

En 2001, Intel intentó introducir una arquitectura de 64 bits que no fuera x86 denominada IA-64 en su procesador Itanium, con el objetivo inicial de llegar al mercado de la informática de alto rendimiento, con la esperanza de que eventualmente reemplazaría al x86 de 32 bits. Si bien IA-64 era incompatible con x86, el procesador Itanium proporcionó capacidades de emulación para traducir instrucciones x86 a IA-64, pero esto afectó tanto el rendimiento de los programas x86 que rara vez, si alguna vez, fue realmente útil para los usuarios: programadores debería reescribir los programas x86 para la arquitectura IA-64 o su rendimiento en Itanium sería mucho peor que en un verdadero procesador x86. El mercado rechazó el procesador Itanium porque rompía la retrocompatibilidad y prefirió seguir usando chips x86, y se reescribieron muy pocos programas para IA-64.

AMD decidió tomar otro camino hacia el direccionamiento de memoria de 64 bits, asegurándose de que la compatibilidad con versiones anteriores no sufriera. En abril de 2003, AMD lanzó el primer procesador x86 con registros de propósito general de 64 bits, el Opteron, capaz de gestionar mucho más de 4 GB de memoria virtual utilizando la nueva extensión x86-64 (también conocida como AMD64 o x64). Las extensiones de 64 bits para la arquitectura x86 se habilitaron solo en el modo largo recientemente introducido, por lo tanto, las aplicaciones y los sistemas operativos de 32 bits y 16 bits podrían simplemente continuar usando un procesador AMD64 en modos protegidos u otros, sin el más mínimo sacrificio de rendimiento y con total compatibilidad con las instrucciones originales del Intel 8086 de 16 bits. El mercado respondió positivamente, adoptando los procesadores AMD de 64 bits tanto para aplicaciones de alto rendimiento como para computadoras comerciales o domésticas.

Al ver que el mercado rechazaba el procesador Itanium incompatible y que Microsoft admitía AMD64, Intel tuvo que responder e introdujo su propio procesador x86-64, el Prescott Pentium 4, en julio de 2004. Como resultado, el El procesador Itanium con su conjunto de instrucciones IA-64 rara vez se usa y x86, a través de su encarnación x86-64, sigue siendo la arquitectura de CPU dominante en las computadoras no integradas.

x86-64 también introdujo el bit NX, que ofrece cierta protección contra errores de seguridad causados por desbordamientos de búfer.

Como resultado de la contribución de AMD de 64 bits al linaje x86 y su posterior aceptación por parte de Intel, las arquitecturas RISC de 64 bits dejaron de ser una amenaza para el ecosistema x86 y casi desaparecieron del mercado de estaciones de trabajo. x86-64 comenzó a utilizarse en potentes superordenadores (en sus encarnaciones AMD Opteron e Intel Xeon), un mercado que anteriormente era el hábitat natural de los diseños RISC de 64 bits (como los microprocesadores IBM Power o los procesadores SPARC). El gran salto hacia la informática de 64 bits y el mantenimiento de la compatibilidad con software de 32 y 16 bits permitieron que la arquitectura x86 se convirtiera en una plataforma extremadamente flexible en la actualidad, con chips x86 que se utilizan desde pequeños sistemas de bajo consumo (por ejemplo, Intel Quark e Intel Atom) a veloces computadoras de escritorio para juegos (por ejemplo, Intel Core i7 y AMD FX/Ryzen), e incluso dominar grandes clústeres de supercomputación, dejando efectivamente solo la arquitectura ARM de 32 bits y 64 bits RISC como competidora en el mercado de los teléfonos inteligentes y las tabletas.

Virtualización

Antes de 2005, los procesadores de arquitectura x86 no podían cumplir con los requisitos de Popek y Goldberg, una especificación para la virtualización creada en 1974 por Gerald J. Popek y Robert P. Goldberg. Sin embargo, tanto los productos de hipervisor de virtualización x86 patentados como los de código abierto se desarrollaron utilizando virtualización basada en software. Los sistemas propietarios incluyen Hyper-V, Parallels Workstation, VMware ESX, VMware Workstation, VMware Workstation Player y Windows Virtual PC, mientras que los sistemas gratuitos y de código abierto incluyen QEMU, Kernel-based Virtual Machine, VirtualBox y Xen.

La introducción de los conjuntos de instrucciones AMD-V e Intel VT-x en 2005 permitió que los procesadores x86 cumplieran con los requisitos de virtualización de Popek y Goldberg.

AES

Contenido relacionado

Set de instrucciones arquitectura

ALOHAnet

Cray-1