Pentium pro

El Pentium Pro es un microprocesador x86 de sexta generación desarrollado y fabricado por Intel y presentado el 1 de noviembre de 1995. Presentó la microarquitectura P6 (a veces denominada i686) y originalmente estaba destinado a reemplazar el Pentium original en una amplia gama de aplicaciones. Mientras que el Pentium y el Pentium MMX tenían 3,1 y 4,5 millones de transistores, respectivamente, el Pentium Pro contenía 5,5 millones de transistores. Más tarde, se redujo a un papel más limitado como servidor y procesador de escritorio de alta gama y se usó en supercomputadoras como ASCI Red, la primera computadora en alcanzar el billón de operaciones de punto flotante por segundo (teraFLOPS) marca de desempeño El Pentium Pro era capaz de configuraciones de procesador doble y cuádruple. Solo vino en un factor de forma, el Socket 8 rectangular relativamente grande. El Pentium Pro fue reemplazado por el Pentium II Xeon en 1998.

Microarquitectura

El arquitecto principal de Pentium Pro fue Fred Pollack, que estaba especializado en superescalaridad y también había trabajado como ingeniero principal de Intel iAPX 432.

Resumen

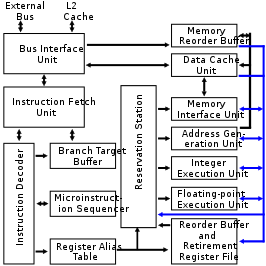

El Pentium Pro incorporó una nueva microarquitectura, diferente a la microarquitectura P5 del Pentium. Tiene una arquitectura superpipelined de 14 etapas desacoplada que utilizó un grupo de instrucciones. El Pentium Pro (P6) implementó muchas diferencias arquitectónicas radicales que reflejan otros diseños x86 contemporáneos como el NexGen Nx586 y Cyrix 6x86. La canalización de Pentium Pro tenía etapas de decodificación adicionales para traducir dinámicamente las instrucciones IA-32 en secuencias de microoperaciones almacenadas en búfer que luego podían analizarse, reordenarse y renombrarse para detectar operaciones paralelizables que pueden enviarse a más de una unidad de ejecución a la vez. Por lo tanto, el Pentium Pro se presentó fuera de la ejecución de órdenes, incluida la ejecución especulativa a través del cambio de nombre del registro. También tenía un bus de direcciones de 36 bits más amplio, utilizable por Extensión de direcciones físicas (PAE), lo que le permitía acceder a hasta 64 GB de memoria.

El Pentium Pro tiene una memoria caché de instrucciones de 8 KB, de la que se extraen hasta 16 bytes en cada ciclo y se envían a los decodificadores de instrucciones. Hay tres decodificadores de instrucciones. Los decodificadores tienen habilidades desiguales: solo uno puede decodificar cualquier instrucción x86, mientras que los otros dos solo pueden decodificar instrucciones x86 simples. Esto restringe la capacidad del Pentium Pro para decodificar varias instrucciones simultáneamente, lo que limita la ejecución superescalar. Las instrucciones x86 se decodifican en microoperaciones de 118 bits (micro-ops). Las microoperaciones son similares a una computadora con conjunto de instrucciones reducido (RISC); es decir, codifican una operación, dos fuentes y un destino. El decodificador general puede generar hasta cuatro microoperaciones por ciclo, mientras que los decodificadores simples pueden generar una microoperación cada uno por ciclo. Por lo tanto, las instrucciones x86 que operan en la memoria (por ejemplo, agregar este registro a esta ubicación en la memoria) solo pueden ser procesadas por el decodificador general, ya que esta operación requiere un mínimo de tres microoperaciones. Asimismo, los decodificadores simples se limitan a instrucciones que pueden traducirse en una microoperación. Las instrucciones que requieren más microoperaciones que cuatro se traducen con la ayuda de un secuenciador, que genera las microoperaciones requeridas en múltiples ciclos de reloj. El Pentium Pro fue el primer procesador de la familia x86 en admitir microcódigo actualizable bajo el control del BIOS y/o del sistema operativo (SO).

Los microoperadores salen del búfer de reorden (ROB) y entran en una estación de reserva (RS), donde esperan ser enviados a las unidades de ejecución. En cada ciclo de reloj, se pueden enviar hasta cinco microoperaciones a cinco unidades de ejecución. El Pentium Pro tiene un total de seis unidades de ejecución: dos unidades de enteros, una unidad de punto flotante (FPU), una unidad de carga, una unidad de dirección de almacenamiento y una unidad de datos de almacenamiento. Una de las unidades enteras comparte los mismos puertos que la FPU y, por lo tanto, el Pentium Pro solo puede enviar una microoperación entera y una microoperación de punto flotante, o dos microoperaciones enteras por ciclo, además de microoperaciones. ops para las otras tres unidades de ejecución. De las dos unidades enteras, solo la que comparte la ruta con la FPU en el puerto 0 tiene el complemento completo de funciones, como un cambiador de barril, multiplicador, divisor y soporte para instrucciones LEA. La segunda unidad de enteros, que está conectada al puerto 1, no tiene estas facilidades y está limitada a operaciones simples como sumar, restar y el cálculo de direcciones de destino de sucursales.

La FPU ejecuta operaciones de punto flotante. La suma y la multiplicación están canalizadas y tienen una latencia de tres y cinco ciclos, respectivamente. La división y la raíz cuadrada no se canalizan y se ejecutan en unidades separadas que comparten los puertos de la FPU. La división y la raíz cuadrada tienen una latencia de 18-36 y 29-69 ciclos, respectivamente. El número más pequeño es para números de punto flotante de precisión simple (32 bits) y el más grande para números de precisión extendida (80 bits). La división y la raíz cuadrada pueden operar simultáneamente con sumas y multiplicaciones, evitando que se ejecuten solo cuando el resultado debe almacenarse en el ROB.

Después de que se lanzó el microprocesador, se descubrió un error en la unidad de punto flotante, comúnmente llamado "error de FPU Pentium Pro y Pentium II" y por Intel como la "errata de la bandera". El error ocurre en algunas circunstancias durante la conversión de coma flotante a entero cuando el número de coma flotante no encaja en el formato de entero más pequeño, lo que hace que la FPU se desvíe de su comportamiento documentado. El error se considera menor y se produce en circunstancias tan especiales que muy pocos programas de software, si es que alguno, se ven afectados.

Intel utilizó la microarquitectura Pentium Pro P6 de una forma u otra durante más de una década. La canalización escalaría desde su inicio inicial de 150 MHz hasta 1,4 GHz con el "Tualatin" Pentium III. Los diversos rasgos del diseño continuarían después de eso en el núcleo derivado llamado "Banias" en Pentium M e Intel Core (Yonah), que evolucionaría hacia la microarquitectura Core (procesador Core 2) a partir de 2006.

Conjunto de instrucciones

El Pentium Pro (P6) introdujo nuevas instrucciones en la gama Intel; las instrucciones CMOVxx ('movimiento condicional') pueden mover un valor que es el contenido de un registro o una ubicación de memoria a otro registro o no, de acuerdo con alguna condición lógica predicada xx en el registro de banderas, siendo xx un código de predicado de banderas tal como se da en la condición de instrucciones de salto condicional. Entonces, por ejemplo, CMOVNE mueve un valor específico a un registro o no, dependiendo de si la condición NE (distinta) es verdadera en el registro de banderas, es decir, bandera Z = 0. Esto permite la evaluación de operaciones if-then-else y, por ejemplo, el ?: operación en C. Estas instrucciones aumentan el rendimiento al evitar las costosas instrucciones de salto y bifurcación. En, por ejemplo, CMOVxx destreg1, source_operand2, el primer operando es el registro de destino, el segundo el registro de origen o la ubicación de la memoria. Desafortunadamente, el segundo operando no puede ser un valor inmediato (constante en línea) y dicha constante debería colocarse primero en un registro. El código de predicado xx puede tomar el rango completo de valores permitidos en las ramas condicionales.

Un segundo desarrollo fue la documentación de la instrucción ilegal UD2. Este código de operación está reservado y garantizado para causar una excepción de instrucción ilegal en el P6 y todos los procesadores posteriores. Esto permite a los desarrolladores bloquear fácilmente el programa actual a prueba de futuro cuando el software detecta un error.

Rendimiento

A pesar de ser avanzada para la época, la arquitectura de cambio de nombre de registros fuera de servicio del Pentium Pro tenía problemas para ejecutar código de 16 bits y código mixto (8 bits con 16 bits (8/16), o 16 bits con 32 bits (16/32), ya que el uso de registros parciales causa un vaciado frecuente de la tubería. El uso específico de registros parciales era entonces una optimización de rendimiento común, ya que no incurría en una penalización de rendimiento en los procesadores Intel anteriores a P6; también, el Los sistemas operativos dominantes en el momento del lanzamiento del Pentium Pro eran DOS de 16 bits y una combinación de Windows 3.1x de 16/32 bits y Windows 95 (aunque este último requiere una CPU 80386 de 32 bits, gran parte de su código sigue siendo de 16 bits por razones de rendimiento, como USER.exe). Esto, con el alto costo de los sistemas Pentium Pro, provocó ventas tibias entre los compradores de PC en ese momento. Para utilizar completamente la microarquitectura P6 de Pentium Pro, se necesita un sistema operativo completo de 32 bits, como Windows NT, Linux, Unix o OS / 2. Posteriormente, Intel mitigó parcialmente los problemas de rendimiento en el código heredado con el Pentium II.

En comparación con los microprocesadores RISC, el Pentium Pro, cuando se presentó, superó levemente a los microprocesadores RISC más rápidos en el rendimiento de números enteros cuando se ejecutó el punto de referencia SPECint95, pero el rendimiento de punto flotante fue significativamente menor, la mitad que el de algunos microprocesadores RISC. La ventaja de rendimiento de enteros del Pentium Pro desapareció rápidamente, primero superado por MIPS Technologies R10000 en enero de 1996, y luego por la variante EV56 de Digital Equipment Corporation del Alpha 21164.

Los revisores notaron rápidamente las escrituras muy lentas en la memoria de video como el punto débil de la plataforma P6, con un rendimiento aquí tan bajo como el 10 % de un sistema Pentium con frecuencia idéntica en puntos de referencia como VIDSPEED. Los métodos para eludir esto incluían configurar el dibujo VESA en la memoria del sistema en lugar de la memoria de video en juegos como Quake, y luego surgieron utilidades como FASTVID, que podría duplicar el rendimiento en ciertos juegos al habilitar las funciones de combinación de escritura. de la CPU. Los controladores de video de Windows configuran automáticamente los registros de rango de tipo de memoria (MTRR) a partir de ~ 1997, y allí el subsistema de caché/memoria mejorado y el rendimiento de la FPU hicieron que superara al Pentium reloj por reloj en los juegos 3D emergentes de mediados de hasta fines de la década de 1990, particularmente cuando se usa NT4. Sin embargo, su falta de implementación de MMX reduce el rendimiento en aplicaciones multimedia que utilizan esas instrucciones.

Almacenamiento en caché

Probablemente, la adición más notable de Pentium Pro fue su caché L2 en el paquete, que osciló entre 256 KB en el momento de la introducción y 1 MB en 1997. En ese momento, la tecnología de fabricación no permitía que se creara una gran caché L2. integrado en el núcleo del procesador. En cambio, Intel colocó los troqueles L2 por separado en el paquete, lo que aún permitía que funcionara a la misma velocidad de reloj que el núcleo de la CPU. Además, a diferencia de la mayoría de los esquemas de caché basados en placa base que compartían el bus del sistema principal con la CPU, el caché del Pentium Pro tenía su propio bus trasero (llamado bus dual independiente por Intel). Debido a esto, la CPU podía leer la memoria principal y la memoria caché al mismo tiempo, lo que reducía en gran medida un cuello de botella tradicional. El caché también era 'sin bloqueo', lo que significa que el procesador podía emitir más de una solicitud de caché a la vez (hasta 4), lo que reducía las penalizaciones por pérdida de caché. (Este es un ejemplo de MLP, paralelismo de nivel de memoria). Estas propiedades se combinaron para producir un caché L2 que era inmensamente más rápido que los cachés basados en placa base de procesadores más antiguos. Este caché solo le dio a la CPU una ventaja en el rendimiento de entrada/salida sobre las CPU x86 más antiguas. En configuraciones multiprocesador, la memoria caché integrada de Pentium Pro mejoró el rendimiento en comparación con las arquitecturas en las que cada CPU compartía una memoria caché central.

Sin embargo, este caché L2 mucho más rápido vino con algunas complicaciones. El "caché en el paquete" del Pentium Pro arreglo fue único. El procesador y la memoria caché estaban en matrices separadas en el mismo paquete y estaban conectados estrechamente mediante un bus de alta velocidad. Los dos o tres troqueles tenían que unirse al principio del proceso de producción, antes de que fuera posible realizar la prueba. Esto significó que un único y diminuto defecto en cualquiera de los dados obligó a descartar todo el ensamblaje, lo cual fue una de las razones del rendimiento de producción relativamente bajo y el alto costo del Pentium Pro. Todas las versiones del chip eran caras, especialmente aquellas con 1024 KB, ya que requerían dos troqueles de caché de 512 KB, así como el troquel del procesador.

Modelos disponibles

Las velocidades de reloj de Pentium Pro eran de 150, 166, 180 o 200 MHz con un reloj de bus externo de 60 o 66 MHz. Algunos usuarios eligieron overclockear sus chips Pentium Pro, con la versión de 200 MHz a menudo funcionando a 233 MHz, la versión de 180 MHz a menudo funcionando a 200 MHz y la versión de 150 MHz a menudo funcionando a 166 MHz. El chip era popular en configuraciones de multiprocesamiento simétrico, siendo comunes las configuraciones de estaciones de trabajo y servidores SMP dobles y cuádruples.

En la "Familia/Modelo/Paso a paso" de Intel esquema, el Pentium Pro es la familia 6, modelo 1, y su código de producto Intel es 80521.

| Reloj | Bus | L2-Cache | Max TDP |

|---|---|---|---|

| 150 MHz | 60 MHz | 0256 KB | 29.2 W |

| 166 MHz | 66 MHz | 0512 KB | 35 W |

| 180 MHz | 60 MHz | 0256 KB | 31,7 W |

| 200 MHz | 66 MHz | 35 W | |

| 0512 KB | 37,9 W | ||

| 1024 KB | 44 W |

Fabricación

El proceso utilizado para fabricar la matriz del procesador Pentium Pro y su matriz de memoria caché separada cambió, lo que llevó a una combinación de procesos utilizados en el mismo paquete:

- The 133 MHz Pentium Pro prototipo procesador die fue fabricado en un proceso de 0,6 μm BiCMOS.

- El pene de 150 MHz Pro procesador die fue fabricado en un proceso de 0,50 μm BiCMOS.

- The 166, 180, and 200 MHz Pentium Pro procesador die fue fabricado en un proceso de 0,35 μm BiCMOS.

- El 256 KB L2 cache die fue fabricado en un proceso de 0,50 μm BiCMOS.

- La caché de 512 y 1024 KB L2 fue fabricada en un proceso de 0,35 μm BiCMOS.

Embalaje

El Pentium Pro (hasta 512 KB de caché) está empaquetado en un módulo multichip cerámico (MCM). El MCM contiene dos cavidades en la parte inferior en las que residen el chip del microprocesador y su caché complementario. Las matrices están unidas a una barra de calor, cuya parte superior expuesta ayuda a que el calor de las matrices se transfiera más directamente al aparato de enfriamiento, como un disipador de calor. Los troqueles se conectan al paquete mediante unión de alambre convencional. Las cavidades se tapan con una placa de cerámica.

El Pentium Pro con 1 MB de caché utiliza un MCM de plástico. En lugar de dos cavidades, solo hay una, en la que residen los tres troqueles, unidos al paquete en lugar de una barra de calor. Las cavidades se rellenan con epoxi.

El MCM tiene 387 pines, de los cuales aproximadamente la mitad están dispuestos en una matriz de cuadrícula de pines (PGA) y la otra mitad en una matriz de cuadrícula de pines intersticial (IPGA). El empaque fue diseñado para Socket 8.

Rutas de actualización

En 1998, se lanzó el procesador Pentium II Overdrive de 300/333 MHz para Socket 8. Con L1 doble y 512 KB de caché L2 de velocidad completa, Intel lo produjo como una opción de actualización inmediata para los propietarios de sistemas Pentium Pro. Sin embargo, solo admitía multiprocesamiento sin cola de dos vías, no de cuatro vías o superior, lo que no lo convertía en una actualización utilizable para sistemas de cuatro procesadores. Estos procesadores Pentium II Xeon especialmente empaquetados se usaron para actualizar ASCI Red, que se convirtió en la primera computadora en alcanzar la marca de rendimiento de teraFLOPS con el procesador Pentium Pro y luego la primera en superar los 2 teraFLOPS después de la actualización a los procesadores Pentium II Xeon.

A medida que las placas base Slot 1 se hicieron predominantes, varios fabricantes lanzaron adaptadores de slocket, como Tyan M2020, Asus C-P6S1, Tekram P6SL1 y Abit KP6. Los zócalos permitieron que los procesadores Pentium Pro se usaran con placas base Slot 1. El conjunto de chips Intel 440FX admitía explícitamente los procesadores Pentium Pro y Pentium II, pero los conjuntos de chips Intel 440BX y Slot 1 posteriores no admitían explícitamente el Pentium Pro, por lo que los slockets Socket 8 no tuvieron un uso generalizado. Los Slockets, en forma de adaptadores Socket 370 a Slot 1, vieron una renovada popularidad cuando Intel presentó los procesadores Socket 370 Celeron y Pentium III.

Especificaciones básicas

Pentium Pro

- L1 caché: 8, 8 KB (datos, instrucciones)

- Caché L2: 256, 512 KB (uno muere) o 1024 KB (dos 512 KB muere) en un módulo multichip relojeado a velocidad de CPU

- Socket: Socket 8

- Autobús frontal: 60 y 66 MHz

- VCore: 3.1-3.3 V

- Fabricación: 0,50 μm o 0,35 BiCMOS

- Reloj: 150, 166, 180, 200 MHz, (capacidad de 233 MHz en algunas placas madre)

- Primera liberación: noviembre de 1995

Sobremarcha Pentium II

- L1 caché: 16, 16 KB (datos + instrucciones)

- L2 cache: 512 KB chip externo en el módulo CPU relojeado a velocidad CPU

- Socket: Socket 8

- Multiplicador: bloqueado en 5×

- Autobús frontal: 60 y 66 MHz

- VCore: 3.1-3.3 V (tiene regulador de tensión a bordo)

- Fabricación: 0,25 μm

- Reloj: Basado en el Pentium II de generación de Deschutes

- Primera liberación: 1997

- Supports MMX technology

Capacidades de bus y multiprocesador

El Pentium Pro usaba señalización GTL+ en su bus frontal. El Pentium Pro podría usarse solo en diseños de hasta cuatro vías. También se construyeron computadoras Pentium Pro de ocho vías, pero usaban múltiples buses.

El diseño del bus Pentium Pro estuvo influenciado por Futurebus, el bus Intel iAPX 432 y elementos del bus Intel i960. Futurebus fue pensado como un bus avanzado para reemplazar el VMEbus utilizado con el Motorola 68000 desde finales de la década de 1970, pero se estancó en el comité de estandarización durante más de una década si se cuentan todos los giros y vueltas. La iniciativa iAPX 432 de Intel también fue un fracaso comercial, pero en el proceso aprendieron a construir un bus de transacciones divididas para admitir un sistema multiprocesador sin caché. El i960 había desarrollado aún más el bus iAPX 432 de transacción dividida para incluir un protocolo de coherencia de caché, finalizando con un conjunto de funciones que recuerda mucho a las ambiciones originales de Futurebus.

El arquitecto principal de i960 fue el especialista en superescalaridad Fred Pollack, quien también fue el ingeniero principal de Intel iAPX 432 y el arquitecto principal del chip i686, el Pentium Pro. Sin duda estaba íntimamente familiarizado con toda esta historia. El Pentium Pro fue diseñado para incluir el bus coherente de caché de transacción dividida SMP de 4 vías como una característica obligatoria de cada chip producido. Esto también sirvió para negar el acceso de la competencia al zócalo para producir procesadores clonados.

Aunque el Pentium Pro no tuvo éxito como máquina para las masas, debido a la pobre compatibilidad de 16 bits con Windows 95, tuvo un gran éxito en el espacio del servidor de archivos debido a su diseño de bus integrado y avanzado, que introdujo muchos características que anteriormente solo estaban disponibles en el segmento de estaciones de trabajo costosas en el mercado de productos básicos.

Competidores Pentium Pro/6.ª generación

- AMD K5 y K6

- Cyrix 6x86 y MII

- IDT WinChip

- Pentium Intel P5, coexistido con Pentium Pro durante varios años