PDP-8

La PDP-8 es una minicomputadora de 12 bits producida por Digital Equipment Corporation (DEC). Fue la primera minicomputadora comercialmente exitosa, con más de 50,000 unidades vendidas durante la vida útil del modelo. Su diseño básico sigue el LINC pionero pero tiene un conjunto de instrucciones más pequeño, que es una versión ampliada del conjunto de instrucciones PDP-5. Máquinas similares de DEC son la PDP-12, que es una versión modernizada de los conceptos PDP-8 y LINC, y el sistema de control industrial PDP-14.

Resumen

El primer modelo PDP-8, conocido informalmente como 'Straight-8', se presentó el 22 de marzo de 1965 con un precio de 18 500 USD (equivalente a unos 160 000 USD en 2021). Utilizaba lógica de diodo-transistor empaquetada en tarjetas de chip invertidas en una máquina del tamaño de un pequeño refrigerador doméstico. Fue la primera computadora que se vendió por menos de $ 20,000, lo que la convirtió en la computadora más vendida en la historia en ese momento. El Straight-8 fue reemplazado en 1966 por el PDP-8/S, que estaba disponible en modelos de escritorio y de montaje en rack. El uso de una unidad lógica aritmética (ALU) en serie de un bit permitió que el PDP-8/S fuera más pequeño y menos costoso, aunque más lento que el PDP-8 original. Una 8/S básica se vendió por menos de $10,000, la primera máquina en alcanzar ese hito.

Los sistemas posteriores (el PDP-8/I y /L, el PDP-8/E, /F y /M, y el PDP-8/A) regresaron a una implementación más rápida y completamente paralela, pero usan mucho menos costosa lógica transistor-transistor (TTL) Lógica MSI. La mayoría de los PDP-8 supervivientes son de esta época. El PDP-8/E es común y bien considerado porque había muchos tipos de dispositivos de E/S disponibles para él. Los últimos modelos comerciales de PDP-8 introducidos en 1979 se denominan 'CMOS-8s', basados en microprocesadores CMOS. No tenían un precio competitivo y la oferta fracasó. Intersil vendió los circuitos integrados comercialmente hasta 1982 como la familia Intersil 6100. En virtud de su tecnología CMOS, tenían requisitos de baja potencia y se utilizaron en algunos sistemas militares integrados.

El ingeniero jefe que diseñó la versión inicial del PDP-8 fue Edson de Castro, quien luego fundó Data General.

Importancia arquitectónica

El PDP-8 combina bajo costo, simplicidad, capacidad de expansión e ingeniería cuidadosa para obtener valor. La mayor importancia histórica fue que el bajo costo y el alto volumen de la PDP-8 hicieron que una computadora estuviera disponible para muchos clientes nuevos para muchos usos nuevos. Su significado continuo es como un ejemplo histórico de diseño de computadora con ingeniería de valor.

La baja complejidad trajo otros costos. Hizo que la programación fuera engorrosa, como se ve en los ejemplos de este artículo y en la discusión de "páginas" y "campos". Gran parte del código de uno realizó la mecánica requerida, en lugar de establecer el algoritmo. Por ejemplo, restar un número implica calcular su complemento a dos y luego sumarlo; escribir un salto condicional implica escribir un salto condicional alrededor del salto, el salto codifica la condición negativa a la deseada. Algunos proyectos de programación ambiciosos no cabían en la memoria o desarrollaron defectos de diseño que no pudieron resolverse. Por ejemplo, como se indica a continuación, la repetición inadvertida de una subrutina produce defectos que son difíciles de rastrear hasta la subrutina en cuestión.

A medida que los avances en el diseño redujeron los costos de la lógica y la memoria, el tiempo del programador se volvió relativamente más importante. Los diseños de computadora posteriores enfatizaron la facilidad de programación, generalmente utilizando conjuntos de instrucciones más grandes e intuitivos.

Finalmente, la mayor parte del código de máquina fue generado por compiladores y generadores de informes. La computadora con conjunto de instrucciones reducido volvió al punto de partida del énfasis del PDP-8 en un conjunto de instrucciones simple y lograr múltiples acciones en un solo ciclo de instrucción, para maximizar la velocidad de ejecución, aunque las computadoras más nuevas tienen palabras de instrucción mucho más largas..

Descripción

El PDP-8 usó ideas de varios predecesores de 12 bits, en particular el LINC diseñado por W.A. Clark y C.E. Molnar, quienes se inspiraron en la minicomputadora CDC 160 de Seymour Cray.

El PDP-8 utiliza 12 bits para su tamaño de palabra y aritmética (en enteros sin signo de 0 a 4095 o enteros con signo de −2048 a +2047). Sin embargo, el software puede hacer aritmética de precisión múltiple. Un intérprete estaba disponible para operaciones de punto flotante, por ejemplo, que usa una representación de punto flotante de 36 bits con una mantisa de dos palabras (24 bits) y un exponente de una palabra. Sujeto a limitaciones de velocidad y memoria, el PDP-8 puede realizar cálculos similares a las computadoras electrónicas contemporáneas más caras, como el IBM 1130 y varios modelos del IBM System/360, mientras que es más fácil de conectar con dispositivos externos.

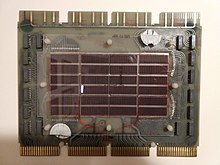

El espacio de direcciones de la memoria también es de 12 bits, por lo que la configuración básica del PDP-8 tiene una memoria principal de 4096 (212) palabras de doce bits. Una unidad de expansión de memoria opcional puede cambiar los bancos de memorias usando una instrucción IOT. La memoria es una memoria de núcleo magnético con un tiempo de ciclo de 1,5 microsegundos (0,667 MHz), de modo que una instrucción de referencia de memoria típica de dos ciclos (Obtener, Ejecutar) se ejecuta a una velocidad de 0,333 MIPS. La tarjeta de referencia de bolsillo de 1974 para el PDP-8/E proporciona un tiempo de instrucción básico de 1,2 microsegundos o 2,6 microsegundos para instrucciones que hacen referencia a la memoria.

El PDP-8 fue diseñado en parte para manejar telecomunicaciones y texto contemporáneos. Los códigos de caracteres de seis bits eran de uso generalizado en ese momento, y las palabras de doce bits del PDP-8 pueden almacenar de manera eficiente dos de esos caracteres. Además, los servicios de noticias por cable usaban ampliamente un código de teleimpresora de seis bits llamado telecomposición o código TTS, y una de las primeras aplicaciones para el PDP-8 fue la composición tipográfica con este código.

Las instrucciones de PDP-8 tienen un código de operación de 3 bits, por lo que solo hay ocho instrucciones. El ensamblador proporciona más mnemónicos de instrucción a un programador al traducir instrucciones de E/S y modo de operación a combinaciones de códigos de operación y campos de instrucción. También tiene solo tres registros visibles para el programador: un acumulador de 12 bits (AC), un contador de programa (PC) y una bandera de acarreo llamada "registro de enlace" (L).

Para entrada y salida, el PDP-8 tiene una sola interrupción compartida por todos los dispositivos, un bus de E/S al que se accede mediante instrucciones de E/S y un canal de acceso directo a memoria (DMA). El bus de E/S programado generalmente ejecuta periféricos de velocidad baja a media, como impresoras, teletipos, perforadoras de cinta de papel y lectores, mientras que DMA se usa para pantallas de tubo de rayos catódicos con un lápiz óptico, convertidores de analógico a digital, digital convertidores a analógico, unidades de cinta y unidades de disco.

Para ahorrar dinero, el diseño utiliza una memoria principal económica para muchos propósitos que son atendidos por registros flip-flop más costosos en otras computadoras, como contadores auxiliares y enlaces de subrutinas.

Los modelos básicos usan software para hacer multiplicaciones y divisiones. Para operaciones matemáticas más rápidas, el Elemento aritmético extendido (EAE) proporciona instrucciones de multiplicación y división con un registro adicional, el registro Multiplicador/Cociente (MQ). El EAE era una opción en el PDP-8 original, el 8/I y el 8/E, pero es una parte integral del microprocesador Intersil 6100.

El PDP-8 está optimizado para simplificar el diseño. En comparación con máquinas más complejas, se eliminaron funciones innecesarias y la lógica se comparte cuando es posible. Las instrucciones utilizan el acceso indirecto, el autoincremento y el autoborrado para aumentar la velocidad del software, reducir el uso de la memoria y sustituir la memoria económica por registros costosos.

La electrónica de una CPU PDP-8 básica tiene solo cuatro registros de 12 bits: el acumulador, el contador de programa, el registro de búfer de memoria y el registro de dirección de memoria. Para ahorrar dinero, estos sirvieron para múltiples propósitos en diferentes puntos del ciclo operativo. Por ejemplo, el registro de búfer de memoria proporciona operandos aritméticos, es parte del registro de instrucciones y almacena datos para reescribir la memoria central. (Esto restaura los datos centrales destruidos por la lectura).

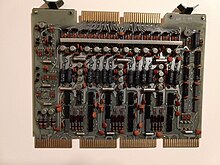

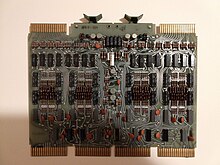

Debido a su simplicidad, los primeros modelos PDP-8 eran menos costosos que la mayoría de las otras computadoras disponibles en el mercado. Sin embargo, utilizaron métodos de producción costosos que a menudo se usan para prototipos. Usaron miles de módulos lógicos estandarizados muy pequeños, con conectores dorados, integrados por un costoso y complejo backplane envuelto en cables en un gabinete grande.

En el último modelo 8/S, presentado en agosto de 1966, dos voltajes lógicos diferentes aumentaron la distribución de la lógica económica de diodo-transistor. El 8/S también redujo la cantidad de puertas lógicas al usar una ruta de datos en serie de un solo bit de ancho para hacer aritmética. La CPU del PDP-8/S tiene solo alrededor de 519 puertas lógicas. En comparación, los microcontroladores pequeños (a partir de 2008) suelen tener 15 000 o más. Las reducciones en la electrónica permitieron una caja mucho más pequeña, del tamaño de una caja de pan. El 8/S fue diseñado por Saul Dinman.

La PDP-8/E, aún más reciente, es una computadora más grande y más capaz, pero rediseñada para obtener un mejor valor. Emplea una lógica transistor-transistor más rápida, en circuitos integrados. La memoria central fue rediseñada. Permite la expansión con menos gastos porque utiliza el OMNIBUS en lugar del backplane envuelto en alambre en modelos anteriores. (Se puede leer un relato personal del desarrollo del PDP-8/E en el Wiki de Historia de Ingeniería y Tecnología).

Versiones de la PDP-8

(feminine)La cifra total de ventas de la familia PDP-8 se ha estimado en más de 300 000 máquinas. Se fabricaron los siguientes modelos:

| Modelo | Descripción | Año | Precio | Cantidad producida | Peso |

|---|---|---|---|---|---|

| PDP-8 | Componentes semi-descretos. Usaron algunos IC híbridos. DTL. | 1965 | 18.000 dólares | 1450 | 250 libras (113 kg) |

| LINC-8 | Podría ejecutar el código LINC o PDP-8 | 1966 | 38.500 dólares | 142 | |

| PDP-8/S | Versión en serie de bajo costo del PDP-8 | 1966 | 10.000 dólares | 1024 | 84 libras (38 kg) |

| PDP-8/I | First PDP-8 made out of standard TTL ICs | 1968 | 12.800 dólares | 3698 | 250 libras (110 kg) |

| PDP-8/L | Contraparte de bajo costo al PDP-8/I | 1968 | 8.500 dólares | 3902 | 80 libras (36 kg) |

| PDP-12 | A PDP-8/I with support for LINC instructions (replaced the LINC-8) | 1969 | 27.900 dólares | 755 | |

| PDP-8/E | Menos, tablas más grandes para mejorar el precio y la eficiencia | 1970 | 6.500 dólares | 90 libras (41 kg) (típica) | |

| PDP-8/F | Contraparte de bajo costo al PDP-8/E | 1972 | 57 libras (26 kg) (típica) | ||

| PDP-8/M | Un PDP-8/F OEM con panel frontal alterado | 1972 | 5.000 dólares | 57 libras (26 kg) (típica) | |

| PDP-8/A | LSI lógica permitió que la CPU encajase en una sola tabla | 1974 | 1.835 dólares | ||

| Intersil 6100 | Microprocesador compatible con PDP-8 (utilizado en el VT78) | 1975 | |||

| Harris 6120 | Microprocesador compatible con PDP-8 CMOS (utilizado en los procesadores de palabras DECmate) | 1976 |

Implementaciones de los últimos días

El PDP-8 se emula fácilmente, ya que su conjunto de instrucciones es mucho más simple que las arquitecturas modernas. Los entusiastas han creado PDP-8 completos utilizando dispositivos FPGA individuales.

Hay varias simulaciones de software de un PDP-8 disponibles en Internet, así como reimplementaciones de hardware de código abierto. Los mejores ejecutan correctamente los sistemas operativos y el software de diagnóstico de DEC. Las simulaciones de software a menudo simulan PDP-8 de último modelo con todos los periféricos posibles. Incluso estos usan solo una pequeña fracción de la capacidad de una computadora personal moderna.

Una de las primeras versiones comerciales de una máquina virtual PDP-8/S se ejecutaba en un Kaypro 386 (una computadora basada en 80386) y estaba escrita en el lenguaje informático C (antes de que se finalizara el estándar ANSI-C) y ensamblador por David Beecher de Denver, Colorado. Reemplazó una computadora PDP-8/S defectuosa que operaba la máquina de manejo de combustible en el Reactor # 85, la estación de generación eléctrica alimentada por combustible nuclear de Platteville, Colorado, Ft. San Vrain. Fue revisado por Rockwell International y funcionó sin problemas durante 2,5 años durante el funcionamiento de la máquina de manejo de combustible mientras se usaba para extraer combustible del núcleo del reactor y desmantelar la planta. Incluía un cargador de cinta de papel simulado y un panel frontal.

Entrada/salida

Los sistemas de E/S sufrieron grandes cambios durante la era PDP-8. Los primeros modelos PDP-8 utilizan una interfaz de panel frontal, un lector de cinta de papel y una impresora de teletipo con una perforadora de cinta de papel opcional. Con el tiempo, se agregaron sistemas de E/S como cinta magnética, RS-232 y terminales tontos de bucle de corriente, lectores de tarjetas perforadas y discos de cabeza fija. Hacia el final de la era PDP-8, los disquetes y las unidades de disco de cartucho de cabezal móvil eran dispositivos de E/S populares. Los entusiastas modernos han creado adaptadores de disco duro IDE estilo PC estándar para computadoras PDP-8 reales y simuladas.

Se admiten varios tipos de E/S:

- ranuras dedicadas para controladores I/O

- Un autobús "Negativo" I/O (utilizando señalización de tensión negativa)

- Un autobús "Positivo" I/O (la misma arquitectura usando señalización TTL)

- El Omnibus (un backplane of undedicated system bus slots) introducido en el PDP-8/E. (Detalles se describen en el artículo referenciado de IEEE que figura a continuación.)

Una forma simplificada y económica de DMA llamada "corte de datos de tres ciclos" esta apoyado; esto requiere la asistencia del procesador. El "corte de datos" El método mueve parte de la lógica común necesaria para implementar E/S DMA desde cada dispositivo de E/S a una copia común de la lógica dentro del procesador. "Rotura de datos" coloca al procesador a cargo de mantener la dirección DMA y los registros de conteo de palabras. En tres ciclos de memoria sucesivos, el procesador actualiza el recuento de palabras, actualiza la dirección de transferencia y almacena o recupera la palabra de datos de E/S real.

La interrupción de datos de un ciclo efectivamente triplica la velocidad de transferencia de DMA porque solo los datos de destino deben transferirse hacia y desde la memoria central. Sin embargo, los dispositivos de E/S necesitan más lógica electrónica para administrar su propio recuento de palabras y transferir registros de direcciones. Para cuando se introdujo el PDP-8/E, la lógica electrónica se había vuelto menos costosa y la "rotura de datos de un ciclo" se hizo más popular.

Instalaciones de programación

Los primeros sistemas PDP-8 se enviaban sin software preinstalado; cada vez que se encendía el PDP-8, el usuario ingresaba manualmente las instrucciones usando un banco de 12 interruptores de palanca. Por lo general, estas instrucciones eran un cargador de arranque para leer un programa del lector de cintas de papel. El desarrollo del programa podría continuar entonces, usando entrada y salida de cinta de papel.

Las versiones en cinta de papel de varios lenguajes de programación estuvieron disponibles, incluido el intérprete FOCAL de DEC y un compilador y tiempo de ejecución 4K FORTRAN.

Hacia el final de la era PDP-8, los sistemas operativos como OS/8 y COS-310 permitieron un editor de modo de línea tradicional y un sistema de desarrollo de compilador de línea de comandos utilizando lenguajes como el lenguaje ensamblador PAL-III, FORTRAN, BASIC y DIBOL.

Había disponible un sistema operativo en tiempo real (RTOS) bastante moderno y avanzado y sistemas multiusuario multitarea preventivos: un sistema en tiempo real (RTS-8) estaba disponible al igual que sistemas comerciales multiusuario (COS-300 y COS-310) y un sistema de procesamiento de textos dedicado para un solo usuario (WPS-8).

También estaba disponible un sistema de tiempo compartido, TSS-8. TSS-8 permite que varios usuarios inicien sesión en el sistema a través de terminales de 110 baudios y editen, compilen y depuren programas. Los lenguajes incluyen una versión especial de BASIC, un subconjunto FORTRAN similar a FORTRAN-1 (sin subrutinas o funciones escritas por el usuario), un subconjunto ALGOL, FOCAL y un ensamblador llamado PAL-D.

Una gran cantidad de software donado por los usuarios para el PDP-8 estaba disponible en DECUS, la Sociedad de Usuarios de Digital Equipment Corporation, y a menudo venía con listas de fuentes completas y documentación.

Conjunto de instrucciones

Los tres bits de orden superior de la palabra de instrucción de 12 bits (etiquetados como bits del 0 al 2) son el código de operación. Para las seis operaciones que se refieren a la memoria, los bits del 5 al 11 proporcionan una dirección de 7 bits. El bit 4, si está establecido, dice que complete la dirección utilizando los 5 bits de orden superior del registro del contador de programa (PC), lo que significa que la ubicación direccionada estaba dentro de las mismas 128 palabras que la instrucción. Si el bit 4 está limpio, se usan ceros, por lo que la ubicación direccionada está dentro de las primeras 128 palabras de la memoria. El bit 3 especifica el direccionamiento indirecto; si se establece, la dirección obtenida como se describe hasta ahora apunta a un valor de 12 bits en la memoria que proporciona la dirección efectiva real para la instrucción; esto permite que los operandos estén en cualquier lugar de la memoria a expensas de una palabra adicional. La instrucción JMP no opera en una palabra de memoria, excepto si se especifica el direccionamiento indirecto, pero tiene los mismos campos de bits.

| 0 | 2 | 3 | 4 | 5 | 11 | ||||||

| Operación | I | Z | Offset | ||||||||

- Páginas de memoria

Este uso de la palabra de instrucción divide la memoria de 4096 palabras en páginas de 128 palabras; el bit 4 de la instrucción selecciona la página actual o la página 0 (direcciones 0000–0177 en octal). La memoria en la página 0 es muy importante, ya que las variables colocadas aquí se pueden abordar directamente desde cualquier página. (Además, la dirección 0000 es donde debe comenzar cualquier rutina de servicio de interrupción, y las direcciones 0010–0017 tienen la propiedad especial de autoincrementarse antes de cualquier referencia indirecta a través de ellas).

El ensamblador estándar coloca valores constantes para la aritmética en la página actual. Asimismo, los saltos entre páginas y las llamadas a subrutinas utilizan una dirección indirecta en la página actual.

Era importante escribir rutinas que se ajustaran a páginas de 128 palabras o organizar rutinas para minimizar las transiciones de página, ya que las referencias y los saltos fuera de la página actual requieren una palabra adicional. En consecuencia, se dedicó mucho tiempo a conservar hábilmente una o varias palabras. Los programadores colocaron código deliberadamente al final de una página para lograr una transición libre a la página siguiente a medida que se incrementaba la PC.

Instrucciones básicas

- 000 – Y – Y el funcionamiento de memoria con AC.

- 001 – TAD – Complemento de dos Asignó el funcionamiento de memoria a a 12 bits valor firmado (AC) w. port en L).

- 010 – ISZ – Incrementar el operado de memoria y Saltar la siguiente instrucción si el resultado es Zero.

- 011 – DCA – Depositar AC en el operado de memoria y Clear AC.

- 100 – JMS – JuMp to Subroutine (storing return address in first word of subroutine!).

- 101 – JMP – JuMP.

- 110 – IOT – Transferencia de entrada y salida (ver abajo).

- 111 – OPR – OPeRations microcodificados (ver abajo).

Instrucciones IOT (transferencia de entrada-salida)

El procesador PDP-8 definió algunas de las instrucciones IOT, pero simplemente proporcionó un marco. La mayoría de las instrucciones IOT fueron definidas por los dispositivos de E/S individuales.

| 0 | 2 | 3 | 8 | 9 | 11 | ||||||

| 6=IOT | Dispositivo | Función | |||||||||

- Dispositivo

Los bits del 3 al 8 de una instrucción IOT seleccionan un dispositivo de E/S. Algunas de estas direcciones de dispositivos están estandarizadas por convención:

- 00 es manejado por el procesador y no enviado a ningún dispositivo I/O (ver abajo).

- 01 es generalmente el lector de cintas de papel de alta velocidad.

- 02 es el golpe de cinta de papel de alta velocidad.

- 03 es el teclado de consola (y cualquier lector de cinta de papel de baja velocidad asociado).

- 04 es la impresora de consola (y cualquier golpe de cinta de papel de baja velocidad asociado).

Las instrucciones para el dispositivo 0 afectan al procesador como un todo. Por ejemplo, ION (6001) activa el procesamiento de interrupciones e IOFF (6002) lo desactiva.

- Función

Los bits del 9 al 11 de una instrucción IOT seleccionan las funciones que realiza el dispositivo. Los dispositivos simples (como el lector y perforador de cinta de papel y el teclado y la impresora de la consola) usan los bits de manera estándar:

- El bit 11 hace que el procesador salte la siguiente instrucción si el dispositivo I/O está listo.

- Un poco 10 limpia la AC.

- Bit 9 mueve una palabra entre AC y el dispositivo, inicia otra transferencia I/O, y aclara la bandera "listo" del dispositivo.

Estas operaciones tienen lugar en un orden bien definido que da resultados útiles si se establece más de un bit.

Los dispositivos más complicados, como las unidades de disco, utilizan estos 3 bits de forma específica para cada dispositivo. Por lo general, un dispositivo decodifica los 3 bits para dar 8 códigos de función posibles.

OPR (tasa de operación)

Muchas operaciones se logran usando OPR, incluyendo la mayoría de las condicionales. OPR no se dirige a una ubicación de memoria; la ejecución condicional se logra omitiendo condicionalmente una instrucción, que suele ser un JMP.

Se decía que la instrucción OPR estaba "microcodificada". Esto no significaba lo que significa la palabra hoy (que un programa de nivel inferior buscó e interpretó la instrucción OPR), sino que cada bit de la palabra de instrucción especifica una determinada acción, y el programador podría lograr varias acciones en un solo ciclo de instrucción. configurando varios bits. En uso, un programador puede escribir varios mnemotécnicos de instrucciones uno al lado del otro, y el ensamblador los combina con OR para idear la palabra de instrucción real. Muchos dispositivos de E/S admiten "microcodificados" Instrucciones IoT.

Las acciones microcodificadas tienen lugar en una secuencia bien definida diseñada para maximizar la utilidad de muchas combinaciones.

Las instrucciones OPR vienen en Grupos. Los bits 3, 8 y 11 identifican el Grupo de una instrucción OPR, por lo que es imposible combinar las acciones microcodificadas de diferentes grupos.

Grupo 1

00 01 02 03 05 06 07 08 09 10 11 ________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________ Silencio Silencio Silencio Silencio Silencio Silencio Silencio Silencio Silencio Silencio Silencio _______________________________________ CMA RAR BSW CLL CML RAL IAC Orden de ejecución 1 1 2 2 4 4 3

- 7200 – CLA – Acumulado

- 7100 – CLL – Limpiar el L Bit

- 7040 – CMA – Unos acumuladores complementarios

- 7020 – CML – Complemento L Bit

- 7001 – IAC – Incremento

- 7010 – RAR – Rotate RoL,AC confianza Bien.

- 7004 – RAL – Rotate iereL,AC confianza Izquierda

- 7012 – RTR – Rotación RoL,AC confianza Dos veces.

- 7006 – RTL – Rotación LL,AC confianza Doble izquierda

- 7002 – BSW – Byte Swap 6-bit "bytes" (PDP 8/e y arriba)

En la mayoría de los casos, las operaciones están secuenciadas para que puedan combinarse de la manera más útil. Por ejemplo, combinar CLA (CLear Accumulator), CLL (CLear Link) e IAC (Increment ACcumulator) primero borra el AC y Link, luego incrementa el acumulador, dejándolo establecido en 1. Agregar RAL a la mezcla (para que CLA CLL IAC RAL) hace que el acumulador se borre, incremente y luego gire a la izquierda, dejándolo establecido en 2. De esta manera, las pequeñas constantes enteras se colocaron en el acumulador con una sola instrucción.

La combinación CMA IAC, que el ensamblador le permite abreviar como CIA, produce la inversa aritmética de AC: la negación del complemento a dos. Dado que no hay instrucción de resta, solo la suma en complemento a dos (TAD), que calcula la diferencia de dos operandos, requiere primero negar el sustraendo.

Una instrucción OPR del Grupo 1 que no tiene configurado ninguno de los bits microprogramados no realiza ninguna acción. El programador puede escribir NOP (Sin operación) para ensamblar dicha instrucción.

Grupo 2, O Grupo

00 01 02 03 05 06 07 08 09 10 11 ________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________ Silencio Silencio Silencio Silencio Silencio Silencio Silencio Silencio Silencio Silencio Silencio _______________________________________ TENCLA SZA OSR SMA SNL HLT 2 1 1 1 3 3

- 7600 – CLA – AC transparente

- 7500 – SMA – Saltar a AC 0 (o grupo)

- 7440 – SZA – Saltar en AC = 0 (o grupo)

- 7420 – SNL – Saltar en L √ 0 (o grupo)

- 7404 – OSR – conmutadores frontales lógicamente 'o' con AC

- 7402 – HLT – Halt

Cuando se borra el bit 8, se realiza un salto si alguna de las condiciones especificadas es verdadera. Por ejemplo, "SMA SZA", código de operación 7540, se salta si AC ≤ 0.

Una instrucción OPR del Grupo 2 que no tiene ninguno de los bits microprogramados establecidos es otra instrucción No-Op.

Grupo 2, Y Grupo

00 01 02 03 05 06 07 08 09 10 11 ________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________ Silencio 1 sufrimiento Silencio Silencio Silencio Silencio Silencio Silencio Silencio Silencio _______________________________________ SNA OSR SPA SZL HLT 2 1 1 1 3 2

- 7410 – SKP – Saltar incondicionalmente

- 7610 – CLA – AC transparente

- 7510 – SPA – Saltar en AC ≥ 0 (y grupo)

- 7450 – SNA – Saltar en AC ل 0 (y grupo)

- 7430 – SZL – Saltar en L = 0 (y grupo)

Cuando se establece el bit 8, la condición de salto del Grupo 2, O se invierte, a través de las leyes de De Morgan: el salto no se realiza si alguna de las condiciones del grupo 2, O está verdadero, lo que significa que todas las condiciones de salto especificadas deben ser verdaderas. Por ejemplo, "SPA SNA", código de operación 7550, se salta si AC > 0. Si no se establece ninguno de los bits 5 a 7, el salto es incondicional.

Grupo 3

Las combinaciones de bits no utilizadas de OPR se definen como un tercer grupo de acciones microprogramadas que afectan principalmente al registro MQ (multiplicador/cociente). El registro MQ y las instrucciones del elemento aritmético extendido (EAE) son opcionales y solo existen cuando se compró la opción EAE.

00 01 02 03 05 06 07 08 09 10 11 ________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________ Silencio Silencio Silencio Silencio Silencio Silencio Silencio Silencio Silencio Silencio Silencio _______________________________________ TENCLA SCA _ _/ MQA MQL CODE 1* 2 2 3

- 7601 – CLA – AC transparente

- 7501 – MQA – Multiplier Quotient con AC (lógica o MQ en AC)

- 7441 – SCA – Paso la carga del contador en AC

- 7421 – MQL – Multiplier Quotient Load (Transferir AC a MQ, AC claro)

- 7621 – CAM – CLA + MQL limpia tanto AC como MQ.

Por lo general, CLA y MQA se combinaron para transferir MQ a AC. Otra combinación útil es MQA y MQL, para intercambiar los dos registros.

Tres bits especificaron una instrucción de multiplicar/dividir para realizar:

- 7401 – Sin operación

- 7403 – SCL – Step Counter Load (mediata palabra sigue, PDP-8/I y arriba)

- 7405 – MUY – Multiply

- 7407 – DVI – Divide

- 7411 – NMI – Normalizar

- 7413 – SHL – Se desplaza a la izquierda (seguir palabra inmediata)

- 7415 – ASR – cambio Aritmético derecho

- 7417 – LSR – cambio lógico derecho

Control de memoria

Una palabra de 12 bits puede tener 4096 valores diferentes, y esta es la cantidad máxima de palabras que el PDP-8 original puede abordar indirectamente a través de un puntero de palabra. 4096 palabras de 12 bits representan 6144 bytes en la terminología moderna, o 6 kB. A medida que los programas se volvieron más complejos y el precio de la memoria cayó, se hizo deseable expandir este límite.

Para mantener la compatibilidad con los programas preexistentes, el nuevo hardware fuera del diseño original agregó bits de alto orden a las direcciones efectivas generadas por el programa. El Controlador de Extensión de Memoria expande la memoria direccionable por un factor de 8, a un total de 32,768 palabras. Se pensó que esta expansión era suficiente porque, con la memoria central que entonces costaba alrededor de 50 centavos por palabra, 32K de memoria completa equivaldrían al costo de la CPU.

Cada 4K de memoria se denomina campo. El controlador de extensión de memoria contiene dos registros de tres bits: el DF (campo de datos) y el IF (campo de instrucciones). Estos registros especifican un campo para cada referencia de memoria de la CPU, permitiendo un total de 15 bits de dirección. El registro IF especifica el campo para búsquedas de instrucciones y referencias directas a memoria; el registro DF especifica el campo para accesos indirectos a datos. Un programa que se ejecuta en un campo puede hacer referencia a datos en el mismo campo mediante direccionamiento directo y hacer referencia a datos en otro campo mediante direccionamiento indirecto.

El controlador de extensión de memoria maneja un conjunto de instrucciones de E/S en el rango de 6200 a 6277 y brinda acceso a los registros DF e IF. La instrucción 62X1 (CDF, Change Data Field) establece el campo de datos en X. De manera similar, 62X2 (CIF) establece el campo de instrucción y 62X3 establece ambos. Los programas preexistentes nunca ejecutarían CIF o CDF; los registros DF e IF apuntarían al mismo campo, un solo campo al que estos programas estaban limitados. El efecto de la instrucción CIF se difirió para que coincidiera con la siguiente instrucción JMP o JMS, de modo que la ejecución de CIF no provocara un salto.

Para los programas de campos múltiples era más complicado manejar los límites de campo y los registros DF e IF de lo que hubiera sido si pudieran generar simplemente direcciones de 15 bits, pero el diseño proporcionó compatibilidad con versiones anteriores y es consistente con los 12 Arquitectura de bits utilizada en todo el PDP-8. Compare el último Intel 8086, cuyas direcciones de memoria de 16 bits se expanden a 20 bits al combinarlas con el contenido de un registro de segmento especificado o implícito.

El esquema de memoria extendida permite que los programas existentes manejen memoria aumentada con cambios mínimos. Por ejemplo, 4K FOCAL normalmente tenía alrededor de 3K de código y solo quedaba 1K para el programa y los datos del usuario. Con algunos parches, FOCAL podría usar un segundo campo 4K para el programa y los datos del usuario. Además, se podrían asignar campos 4K adicionales a usuarios separados, convirtiendo 4K FOCAL en un sistema de tiempo compartido multiusuario.

- Virtualización

En el modelo PDP-8/E y posteriores, se mejoró el controlador de extensión de memoria para habilitar la virtualización de máquinas. Un programa escrito para usar todos los recursos de un PDP-8 puede coexistir con otros programas similares en el mismo PDP-8 bajo el control de un administrador de máquina virtual. El administrador puede hacer que todas las instrucciones de E/S (incluidas las que operaron en el controlador de extensión de memoria) provoquen una trampa (una interrupción manejada por el administrador). De esta forma, el administrador puede mapear referencias de memoria, mapear datos o campos de instrucciones y redirigir E/S a diferentes dispositivos. Cada programa original tiene acceso completo a una "máquina virtual" proporcionada por el gerente.

Las nuevas instrucciones de E/S para el controlador de extensión de memoria recuperan el valor actual de los campos de datos e instrucciones, lo que permite que el software guarde y restaure la mayor parte del estado de la máquina a través de una trampa. Sin embargo, un programa no puede detectar si la CPU está en proceso de diferir el efecto de una instrucción CIF (si ha ejecutado un CIF y aún no ha ejecutado la instrucción de salto correspondiente). El administrador debe incluir un emulador PDP-8 completo (no es difícil para una máquina de 8 instrucciones). Cada vez que una instrucción CIF atrapa al administrador, debe emular las instrucciones hasta el siguiente salto. Afortunadamente, como un salto suele ser la siguiente instrucción después de CIF, esta emulación no ralentiza mucho los programas, pero es una gran solución para una deficiencia de diseño aparentemente pequeña.

En el momento del PDP-8/A, los precios de la memoria habían bajado lo suficiente como para desear una memoria superior a 32K. El 8/A agregó un nuevo conjunto de instrucciones para manejar más de ocho campos de memoria. El número de campo ahora podría colocarse en el AC, en lugar de codificarse en la instrucción. Sin embargo, en ese momento, el PDP-8 estaba en declive, por lo que se modificó muy poco software estándar para usar estas nuevas funciones.

Ejemplos

Los siguientes ejemplos muestran código en lenguaje ensamblador PDP-8 como se podría escribir para el ensamblador PAL-III.

Comparar dos números

La siguiente pieza de código muestra lo que se necesita solo para comparar dos números:

/Comparar números en memoria de OPD1 y OPD2 CLA CLL /Must comienza con 0 en AC y enlace TAD OPD1 /Load opera primero en AC (añadiéndolo a 0); el enlace sigue siendo claro CIA / Complemento, luego aumenta AC, negándolo TAD OPD2 /AC ahora tiene OPD2-OPD1; si OPD2≥OPD1, la suma se desborda y se establece el enlace SZL /Skip si el enlace es claro JMP OP2GT /Jump en algún lugar en el caso de que OPD2≥OPD1; /Otros, caen a través de código abajo.

Como se muestra, gran parte del texto de un programa PDP-8 típico no se centra en el algoritmo previsto por el autor, sino en la mecánica de bajo nivel. Un problema de legibilidad adicional es que en saltos condicionales como el que se muestra arriba, la instrucción condicional (que salta el JMP) resalta lo contrario de la condición de interés.

Cadena de salida

Este programa completo de lenguaje ensamblador PDP-8 genera "¡Hola, mundo!" al teletipo.

*10 / Establecer el origen de montaje actual para la dirección 10, STPTR, STRNG-1 / Registro de autoincremento (uno de ocho a 10-17) *200 / Establecer el origen de montaje actual para programar el área de texto HELLO, CLA CLL / Clear AC y Link de nuevo (necesitado cuando nos alejamos de tls) TAD I Z STPTR / Obtenga el siguiente carácter, indirecto a través de la dirección PRE-auto-incremento desde la página cero SNA / Skip if non-zero (not end of string) HLT / Else parar en cero (fin de cadena) TLS / Output the character in the AC to the teleprinter TSF / Skip if teleprinter ready for character JMP.-1 / Else retrocede e inténtelo de nuevo JMP HELLO / Volver al siguiente personaje STRNG, 310 / H 345 / e 354 / l 354 / l 357 / o 254 /, 240 / (espacio) 367 / w 357 / o 362 / r 354 / l 344 / d 241 / ! 0 / Fin de la cuerda $HELLO /DEFAULT TERMINATOR

Subrutinas

El procesador PDP-8 no implementa una pila sobre la cual almacenar registros u otro contexto cuando se llama a una subrutina o se produce una interrupción. (Se puede implementar una pila en el software, como se demuestra en la siguiente sección). En cambio, la instrucción JMS simplemente almacena la PC actualizada (apuntando más allá de JMS, a la dirección de retorno) en la dirección efectiva y salta a la dirección efectiva más uno. La subrutina regresó a su llamador mediante una instrucción JMP indirecta que aborda la primera palabra de la subrutina.

Por ejemplo, aquí está "¡Hola, mundo!" reescrito para usar una subrutina. Cuando la instrucción JMS salta a la subrutina, modifica el 0 codificado en la ubicación OUT1:

*10 / Establecer el origen de montaje actual para la dirección 10, STPTR, STRNG-1 / Registro de autoincremento (uno de ocho a 10-17) *200 / Conjunto de origen de montaje (dirección de descarga) LOOP, TAD I STPTR / Pre-increment mem location 10, evite indirectamente para conseguir el próximo carácter de nuestro mensaje SNA / Skip on non-zero AC HLT / Alto al final del mensaje JMS OUT1 / Escribe un personaje JMP LOOP / Y vuelta atrás para más OUT1, 0 / Será reemplazado por el PC actualizado de llamada TSF / Skip if printer ready JMP.-1 / Espera la bandera TLS / Enviar el personaje en el AC CLA CLL / Clear AC y Link para el próximo paso JMP I OUT1 / Volver a la llamada STRNG, "H / Un mensaje bien conocido "e / "I / NOTA: "l / "o / Las cuerdas en PAL-8 y PAL-III fueron "sixbit" ", / Para usar ASCII, lo deletreamos, carácter por carácter " "w / "o / "r / "l / "d / " 015 / 012 / 0 / Marcar el final de nuestra cadena nula-terminada (.ASCIZ no había sido inventado todavía!)

El hecho de que la instrucción JMS utilice la palabra justo antes del código de la subrutina para depositar la dirección de retorno evita la reentrada y la recursividad sin trabajo adicional por parte del programador. También dificulta el uso de ROM con el PDP-8 porque el almacenamiento de dirección de retorno de lectura y escritura se mezcla con el almacenamiento de código de solo lectura en el espacio de direcciones. Los programas destinados a ser colocados en ROM abordan este problema de varias maneras:

- Se copian para leer la memoria antes de la ejecución, o

- Se colocan en tarjetas ROM especiales que proporcionan algunas palabras de memoria de lectura/escritura, accedidas indirectamente a través del uso de un bit de trece banderas en cada palabra ROM.

- Evitan el uso de subrutinas; o usan códigos como los siguientes, en lugar de la instrucción JMS, para poner la dirección de retorno en la memoria de lectura-escritura:

JUMPL, DCA TEMP / Depósito del acumulador en algún lugar temporal TAD JUMPL+3 / Cargar la dirección de retorno en el acumulador: codificado duro JMP SUBRO / Ve a la subrutina, y haz que la manija retroceder (a JUMPL+3)

El uso de la instrucción JMS dificulta la depuración. Si un programador comete el error de hacer que una subrutina se llame a sí misma, directamente o mediante una subrutina intermedia, la dirección de retorno de la llamada externa es destruida por la dirección de retorno de la llamada posterior, lo que lleva a un bucle infinito. Si un módulo está codificado con una dirección incorrecta u obsoleta para una subrutina, no solo fallaría al ejecutar la secuencia de código completa de la subrutina, sino que podría modificar una palabra del código de la subrutina, depositando una dirección de retorno que el procesador podría interpretarse como una instrucción durante una subsiguiente llamada correcta a la subrutina. Ambos tipos de error pueden volverse evidentes durante la ejecución del código que se escribió correctamente.

Pila de software

Aunque el PDP-8 no tiene una pila de hardware, las pilas se pueden implementar en el software. Aquí hay ejemplos de subrutinas PUSH y POP, simplificadas para omitir problemas como la prueba de desbordamiento y subdesbordamiento de pila:

*100 /make rutinas accesibles para el siguiente ejemplo PUSH, 0 DCA DATA CLA CMA / -1 TAD SP DCA SP TAD DATA DCA I SP JMP I PUSH / Retorno POP, 0 CLA CLL TAD I SP ISZ SP JMP I POP DATOS, 0 SP, 0

Y aquí está "Hello World" con esta "pila" implementado y "FUERA" subrutina:

*200 MAIN, CLA CLL /Set el indicador del mensaje TAD (MESSG /Al principio del mensaje (literal) DCA SP LOOP, JMS POP SNA /Parar la ejecución si cero HLT JMS OUT / Otra vez, producir un personaje JMP LOOP Señor, "H "e "l "l "o " " " "o "r "l "d "! 015 012 0 OUT, 0 / Será reemplazado por el PC actualizado de la llamada TSF / Skip if printer ready JMP.-1 / Espera la bandera TLS / Enviar el personaje en el AC CLA CLL / Clear AC y Link para el próximo paso JMP I OUT / Volver a la llamada

Lista enlazada

Otra posible subrutina para el PDP-8 es una lista enlazada.

GETN, 0 /Obtiene el número apuntado y mueve el puntero CLA CLL /Clear accumulator TAD I PTR /Obtiene el número apuntado a DCA TEMP /Ahorra valor actual ISZ PTR / Increment pointer TAD I PTR / Obtener la siguiente dirección DCA PTR /Put en puntero JMP I GETN /return PTR, 0 TEMP, 0

Interrupciones

Hay una sola línea de interrupción en el bus de E/S del PDP-8. El procesador maneja cualquier interrupción deshabilitando más interrupciones y ejecutando un JMS en la ubicación 0000. Como es difícil escribir subrutinas reentrantes, es difícil anidar interrupciones y esto generalmente no se hace; cada interrupción se ejecuta hasta el final y vuelve a habilitar las interrupciones justo antes de ejecutar la instrucción JMP I 0 que regresa de la interrupción.

Debido a que solo hay una línea de interrupción en el bus de E/S, la ocurrencia de una interrupción no informa al procesador de la fuente de la interrupción. En su lugar, la rutina de servicio de interrupción tiene que sondear en serie cada dispositivo de E/S activo para ver si es la fuente. El código que hace esto se denomina cadena de omisión porque consiste en una serie de PDP-8 "probar y omitir si se establece la bandera" Instrucciones de E/S. (No era extraño que una cadena de salto llegara a su fin sin encontrar ningún dispositivo que necesitara servicio). La prioridad de interrupción relativa de los dispositivos de E/S está determinada por su posición en el salto. cadena: si varios dispositivos se interrumpen, el dispositivo probado anteriormente en la cadena de salto se repara primero.

Libros

Un libro de texto de ingeniería popular en la década de 1980, El arte del diseño digital de David Winkel y Franklin Prosser, contiene un problema de ejemplo que abarca varios capítulos en los que los autores demuestran el proceso de diseño de una computadora que es compatible con el PDP-8/I. Se explica la función de cada componente. Aunque no es un diseño de producción, ya que utiliza componentes SSI y MSI más modernos y memoria de estado sólido en lugar de memoria central, el ejercicio proporciona una descripción detallada del funcionamiento de la computadora.

Clones sin licencia

La URSS produjo las minicomputadoras Saratov-1 y Saratov-2, que clonaron el PDP-8 y el PDP-8/E, respectivamente.

Contenido relacionado

Dan Bricklin

Cinta perforada

Intel 8008