Multiplexor

En electrónica, a multiplexador (o mux; escrito a veces como multiplexor), también conocido como un selector de datos, es un dispositivo que selecciona entre varias señales de entrada analógicas o digitales y envía la entrada seleccionada a una sola línea de salida. La selección está dirigida por un conjunto separado de entradas digitales conocidas como líneas selectas. Un multiplexor de 2n{displaystyle 2^{n} entradas n{displaystyle n} seleccionar líneas, que se utilizan para seleccionar qué línea de entrada enviar a la salida.

Un multiplexor hace posible que varias señales de entrada compartan un dispositivo o recurso, por ejemplo, un convertidor de analógico a digital o un medio de transmisión de comunicaciones, en lugar de tener un dispositivo por señal de entrada. Los multiplexores también se pueden usar para implementar funciones booleanas de múltiples variables.

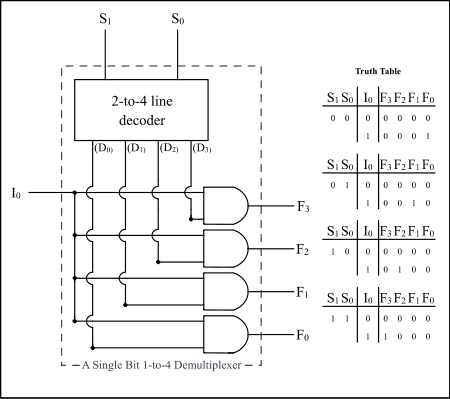

Por el contrario, un demultiplexor (o demux) es un dispositivo que toma una sola entrada y selecciona señales de la salida del mux compatible, que está conectado a la entrada única y una línea de selección compartida. A menudo se utiliza un multiplexor con un demultiplexor complementario en el extremo receptor.

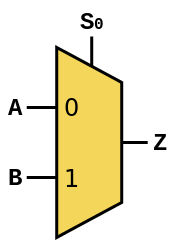

Un multiplexor electrónico se puede considerar como un interruptor de entrada múltiple, un solo salida, y un demultiplexer como un interruptor de entrada única y salida múltiple. El símbolo esquemático para un multiplexor es un isosceles trapezoide con el lado paralelo más largo que contiene los pines de entrada y el lado paralelo corto que contiene el pin de salida. El esquema de la derecha muestra un multiplexor de 2 a 1 en la izquierda y un interruptor equivalente en la derecha. El sel{displaystyle sel} alambre conecta la entrada deseada a la salida.

Aplicaciones

Los multiplexores son parte de los sistemas informáticos para seleccionar datos de una fuente específica, ya sea un chip de memoria o un periférico de hardware. Una computadora usa multiplexores para controlar los buses de datos y direcciones, lo que permite que el procesador seleccione datos de múltiples fuentes de datos.

En las comunicaciones digitales, los multiplexores permiten varias conexiones en un solo canal, al conectar la salida única del multiplexor a la entrada única del demultiplexor (multiplexación por división de tiempo). La imagen de la derecha demuestra este beneficio. En este caso, el costo de implementar canales separados para cada fuente de datos es mayor que el costo y la inconveniencia de proporcionar las funciones de multiplexado/desmultiplexado.

En el extremo receptor del enlace de datos, generalmente se requiere un desmultiplexor complementario para dividir el flujo de datos único en los flujos originales. En algunos casos, el sistema del otro extremo puede tener una funcionalidad mayor que un simple demultiplexor; y aunque técnicamente todavía se produce la demultiplexación, es posible que nunca se implemente de forma discreta. Este sería el caso cuando, por ejemplo, un multiplexor da servicio a varios usuarios de la red IP; y luego alimenta directamente a un enrutador, que inmediatamente lee el contenido de todo el enlace en su procesador de enrutamiento; y luego hace la demultiplexación en memoria desde donde se convertirá directamente en secciones IP.

A menudo, un multiplexor y un demultiplexor se combinan en una sola pieza de equipo, que simplemente se denomina multiplexor. Ambos elementos del circuito son necesarios en ambos extremos de un enlace de transmisión porque la mayoría de los sistemas de comunicaciones transmiten en ambas direcciones.

En el diseño de circuitos analógicos, un multiplexor es un tipo especial de interruptor analógico que conecta una señal seleccionada de varias entradas a una sola salida.

Multiplexores digitales

En el diseño de circuitos digitales, los cables selectores son de valor digital. En el caso de un multiplexor 2-a-1, un valor lógico de 0 se conectaría I0{displaystyle I_{0} a la salida, mientras que un valor lógico de 1 se conectaría I1{displaystyle I_{1} a la salida. En multiplexores más grandes, el número de pins selectores es igual a ⌈log2 ()n)⌉{displaystyle leftlceil log _{2}(n)rightrceil } Donde n{displaystyle n} es el número de entradas.

Por ejemplo, de 9 a 16 entradas requerirían no menos de 4 pines selectores y de 17 a 32 entradas requerirían no menos de 5 pines selectores. El valor binario expresado en estos pines selectores determina el pin de entrada seleccionado.

Un multiplexador de 2 a 1 tiene una ecuación booleana donde A{displaystyle A} y B{displaystyle B} son las dos entradas, S0{displaystyle S_{0} es la entrada selectora, y Z{displaystyle Z} es la salida:

- Z=()A∧ ∧ ¬ ¬ S0)Alternativa Alternativa ()B∧ ∧ S0){displaystyle Z=(Awedge neg S_{0})vee (Bwedge S_{0})}

Que se puede expresar como una tabla de verdad:

| S0{displaystyle S_{0} | A{displaystyle A} | B{displaystyle B} | Z{displaystyle Z} |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

O, en una notación más simple:

| S0{displaystyle S_{0} | Z{displaystyle Z} |

|---|---|

| 0 | A |

| 1 | B |

Estas tablas muestran que cuando S0=0{displaystyle S_{0}=0} entonces Z=A{displaystyle Z=A} pero cuando S0=1{displaystyle S_{0}=1} entonces Z=B{displaystyle Z=B.. Una realización directa de este multiplexor 2-a-1 necesitaría 2 Y puertas, una puerta OR y una puerta NO. Si bien esto es matemáticamente correcto, una implementación física directa sería propensa a las condiciones de raza que requieren puertas adicionales para suprimir.

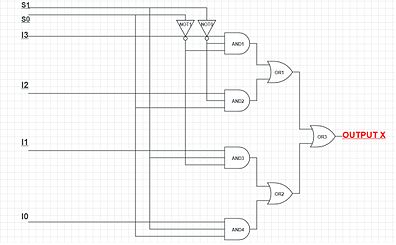

Los multiplexores más grandes también son comunes y, como se indicó anteriormente, requieren ⌈log2 ()n)⌉{displaystyle leftlceil log _{2}(n)rightrceil } pins selector para n{displaystyle n} entradas. Otros tamaños comunes son 4 a 1, 8 a 1, y 16 a-1. Puesto que la lógica digital utiliza valores binarios, los poderes de 2 se utilizan (4, 8, 16) para controlar al máximo una serie de entradas para el número dado de entradas selectoras.

La ecuación booleana para un multiplexor 4 a 1 es:

- Z=()A∧ ∧ ¬ ¬ S0∧ ∧ ¬ ¬ S1)Alternativa Alternativa ()B∧ ∧ S0∧ ∧ ¬ ¬ S1)Alternativa Alternativa ()C∧ ∧ ¬ ¬ S0∧ ∧ S1)Alternativa Alternativa ()D∧ ∧ S0∧ ∧ S1){displaystyle Z=(Awedge neg {S_{0}wedge neg S_{1})vee (Bwedge S_{0}wedge neg S_{1})vee (Cwedge neg S_{0}wedge S_{1})vee (Dwedge S_{0}wedge S_{1}

El siguiente multiplexor 4 a 1 se construye a partir de búferes de 3 estados y puertas AND (las puertas AND actúan como decodificador):

Los subscriptos en los In{displaystyle I_{n} Las entradas indican el valor decimal de las entradas de control binario en las que se permite esa entrada.

Encadenamiento de multiplexores

Los multiplexores más grandes se pueden construir utilizando multiplexores más pequeños encadenándolos entre sí. Por ejemplo, un multiplexor 8 a 1 puede fabricarse con dos multiplexores 4 a 1 y uno 2 a 1. Las dos salidas del multiplexor 4 a 1 se alimentan al 2 a 1 con los pines selectores en los 4 a 1 puestos en paralelo dando un número total de entradas de selector a 3, que es equivalente a un 8 a 1.

Lista de circuitos integrados que proporcionan multiplexación

Para los números de pieza de la serie 7400 en la siguiente tabla, "x" es la familia lógica.

| IC No. | Función | Estado producto |

|---|---|---|

| 74x157 | Quad 2:1 mux. | Producto igual a la entrada dada |

| 74x158 | Quad 2:1 mux. | La salida es entrada invertida |

| 74x153 | Doble 4:1 mux. | Producto igual a la entrada |

| 74x352 | Doble 4:1 mux. | La salida es entrada invertida |

| 74x151A | 8:1 mux. | Ambos productos disponibles (es decir, productos complementarios) |

| 74x151 | 8:1 mux. | La salida es entrada invertida |

| 74x150 | 16:1 mux. | La salida es entrada invertida |

Demultiplexores digitales

Los demultiplexores toman una entrada de datos y varias entradas de selección, y tienen varias salidas. Envían la entrada de datos a una de las salidas en función de los valores de las entradas de selección. Los demultiplexores a veces son convenientes para diseñar lógica de uso general porque si la entrada del demultiplexor siempre es verdadera, el demultiplexor actúa como un decodificador binario. Esto significa que cualquier función de los bits de selección puede construirse mediante un OR lógico en el conjunto correcto de salidas.

Si X es la entrada y S es el selector, y A y B son las salidas:

Lista de circuitos integrados que proporcionan demultiplexación

Para los números de pieza de la serie 7400 en la siguiente tabla, "x" es la familia lógica.

| IC No (7400) | IC No (4000) | Función | Estado producto |

|---|---|---|---|

| 74x139 | Doble 1:4 demux. | La salida es entrada invertida | |

| 74x156 | Doble 1:4 demux. | La salida es un coleccionista abierto | |

| 74x138 | 1:8 demux. | La salida es entrada invertida | |

| 74x238 | 1:8 demux. | ||

| 74x154 | 1:16 demux. | La salida es entrada invertida | |

| 74x159 | CD4514/15 | 1:16 demux. | La salida es el coleccionista abierto y el mismo que la entrada |

Multiplexores como PLD

Los multiplexores también se pueden utilizar como dispositivos lógicos programables para implementar funciones booleanas. Cualquier función booleana de variables n y un resultado se puede implementar con un multiplexor con entradas de selector n. Las variables se conectan a las entradas del selector, y el resultado de la función, 0 o 1, para cada combinación posible de entradas del selector se conecta a la entrada de datos correspondiente. Si una de las variables (por ejemplo, D) también está disponible invertida, un multiplexor con entradas de selector n-1 es suficiente; las entradas de datos se conectan a 0, 1, D o ~D, según la salida deseada para cada combinación de las entradas del selector.

Contenido relacionado

Comprobación de redundancia longitudinal

Algoritmo de Grover

Nitrox