Múltiples instrucciones, múltiples datos

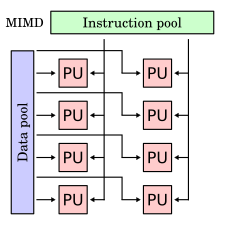

En informática, instrucción múltiple, datos múltiples (MIMD) es una técnica empleada para lograr el paralelismo. Las máquinas que utilizan MIMD tienen varios procesadores que funcionan de forma asíncrona e independiente. En cualquier momento, diferentes procesadores pueden ejecutar diferentes instrucciones en diferentes datos.

Las arquitecturas MIMD se pueden utilizar en diversas áreas de aplicación, como diseño asistido por computadora/fabricación asistida por computadora, simulación, modelado y como interruptores de comunicación. Las máquinas MIMD pueden ser de memoria compartida o de memoria distribuida. Estas clasificaciones se basan en cómo los procesadores MIMD acceden a la memoria. Las máquinas de memoria compartida pueden ser de tipo bus, extendida o jerárquica. Las máquinas de memoria distribuida pueden tener esquemas de interconexión de hipercubo o malla.

Ejemplos

Un ejemplo de sistema MIMD es Intel Xeon Phi, descendiente de la microarquitectura Larrabee. Estos procesadores tienen múltiples núcleos de procesamiento (hasta 61 a partir de 2015) que pueden ejecutar diferentes instrucciones en diferentes datos.

La mayoría de las computadoras paralelas, a partir de 2013, son sistemas MIMD.

Modelo de memoria compartida

En el modelo de memoria compartida, todos los procesadores están conectados a un "disponible globalmente" memoria, ya sea por medio de software o hardware. El sistema operativo generalmente mantiene su coherencia de memoria.

Desde el punto de vista de un programador, este modelo de memoria se comprende mejor que el modelo de memoria distribuida. Otra ventaja es que la coherencia de la memoria la gestiona el sistema operativo y no el programa escrito. Dos desventajas conocidas son: la escalabilidad más allá de treinta y dos procesadores es difícil y el modelo de memoria compartida es menos flexible que el modelo de memoria distribuida.

Hay muchos ejemplos de memoria compartida (multiprocesadores): UMA (acceso a memoria uniforme), COMA (acceso a memoria de solo caché).

Basado en autobús

Las máquinas MIMD con memoria compartida tienen procesadores que comparten una memoria central común. En la forma más simple, todos los procesadores están conectados a un bus que los conecta a la memoria. Esto significa que cada máquina con memoria compartida comparte un CM específico, sistema de bus común para todos los clientes.

Por ejemplo, si consideramos un bus con los clientes A, B, C conectados en un lado y P, Q, R conectados en el lado opuesto, cualquiera de los clientes se comunicará con el otro por medio de la interfaz de bus entre ellos.

Jerárquica

(feminine)Las máquinas MIMD con memoria compartida jerárquica usan una jerarquía de buses (como, por ejemplo, en un 'árbol grueso') para dar a los procesadores acceso a la memoria de los demás. Los procesadores de diferentes placas pueden comunicarse a través de buses internodales. Los buses admiten la comunicación entre placas. Con este tipo de arquitectura, la máquina puede soportar más de nueve mil procesadores.

Memoria distribuida

En las máquinas MIMD (múltiples instrucciones, múltiples datos) de memoria distribuida, cada procesador tiene su propia ubicación de memoria individual. Cada procesador no tiene conocimiento directo sobre la memoria de otro procesador. Para que los datos se compartan, deben pasar de un procesador a otro como un mensaje. Dado que no hay memoria compartida, la contención no es un problema tan grande con estas máquinas. No es económicamente factible conectar una gran cantidad de procesadores directamente entre sí. Una forma de evitar esta multitud de conexiones directas es conectar cada procesador a unos pocos más. Este tipo de diseño puede resultar ineficaz debido al tiempo adicional necesario para pasar un mensaje de un procesador a otro a lo largo de la ruta del mensaje. La cantidad de tiempo requerida para que los procesadores realicen el enrutamiento de mensajes simples puede ser considerable. Los sistemas se diseñaron para reducir esta pérdida de tiempo y el hipercubo y la malla se encuentran entre dos de los esquemas de interconexión populares.

Ejemplos de memoria distribuida (varias computadoras) incluyen MPP (procesadores paralelos masivos), COW (grupos de estaciones de trabajo) y NUMA (acceso a memoria no uniforme). El primero es complejo y costoso: muchas supercomputadoras acopladas a redes de banda ancha. Los ejemplos incluyen hipercubo e interconexiones de malla. VACA es el "hecho en casa" versión por una fracción del precio.

Red de interconexión Hipercubo

En una máquina de memoria distribuida MIMD con una red de interconexión de sistema de hipercubo que contiene cuatro procesadores, se coloca un procesador y un módulo de memoria en cada vértice de un cuadrado. El diámetro del sistema es el número mínimo de pasos necesarios para que un procesador envíe un mensaje al procesador que está más alejado. Entonces, por ejemplo, el diámetro de un cubo de 2 es 2. En un sistema de hipercubo con ocho procesadores y cada procesador y módulo de memoria se colocan en el vértice de un cubo, el diámetro es 3. En general, un sistema que contiene 2 ^ N procesadores con cada procesador conectado directamente a otros N procesadores, el diámetro del sistema es N. Una desventaja de un sistema de hipercubo es que debe configurarse en potencias de dos, por lo que se debe construir una máquina que potencialmente podría tener muchos más procesadores de los que realmente necesita la aplicación.

Red de interconexión en malla

En una máquina de memoria distribuida MIMD con una red de interconexión de malla, los procesadores se colocan en una cuadrícula bidimensional. Cada procesador está conectado a sus cuatro vecinos inmediatos. Se pueden proporcionar conexiones envolventes en los bordes de la malla. Una ventaja de la red de interconexión de malla sobre el hipercubo es que el sistema de malla no necesita configurarse en potencias de dos. Una desventaja es que el diámetro de la red de malla es mayor que el hipercubo para sistemas con más de cuatro procesadores.

Contenido relacionado

Marco de descripción de recursos

Desinflar

Programación lógica inductiva