Memoria de núcleo magnético

La memoria de núcleo magnético fue la forma predominante de memoria informática de acceso aleatorio durante 20 años, entre 1955 y 1975. Dicha memoria a menudo se denomina simplemente memoria central o, de manera informal, núcleo.

La memoria de núcleo utiliza toroides (anillos) de un material magnético duro (por lo general, una ferrita semidura) como núcleos de transformadores, donde cada cable que pasa por el núcleo sirve como bobinado de transformador. Dos o más cables pasan a través de cada núcleo. La histéresis magnética permite que cada uno de los núcleos "recuerde" o almacene un estado.

Cada núcleo almacena un bit de información. Un núcleo se puede magnetizar en el sentido de las agujas del reloj o en el sentido contrario a las agujas del reloj. El valor del bit almacenado en un núcleo es cero o uno según la dirección de magnetización de ese núcleo. Los pulsos de corriente eléctrica en algunos de los cables a través de un núcleo permiten que la dirección de la magnetización en ese núcleo se establezca en cualquier dirección, almacenando así un uno o un cero. Otro cable a través de cada núcleo, el cable de detección, se usa para detectar si el núcleo cambió de estado.

El proceso de lectura del núcleo hace que el núcleo se restablezca a cero, lo que lo borra. Esto se llama lectura destructiva. Cuando no se está leyendo ni escribiendo, los núcleos mantienen el último valor que tenían, incluso si se apaga la alimentación. Por lo tanto, son un tipo de memoria no volátil.

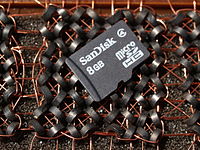

Usando núcleos y cables más pequeños, la densidad de memoria del núcleo aumentó lentamente y, a fines de la década de 1960, era típica una densidad de aproximadamente 32 kilobits por pie cúbico (alrededor de 0,9 kilobits por litro). Sin embargo, alcanzar esta densidad requirió una fabricación extremadamente cuidadosa, que casi siempre se llevó a cabo a mano a pesar de los repetidos e importantes esfuerzos para automatizar el proceso. El costo disminuyó durante este período de alrededor de $1 por bit a alrededor de 1 centavo por bit. La introducción de los primeros chips de memoria de semiconductores a fines de la década de 1960, que inicialmente crearon una memoria estática de acceso aleatorio (SRAM), comenzó a erosionar el mercado de la memoria central. La primera memoria dinámica de acceso aleatorio (DRAM) exitosa, la Intel 1103, siguió en 1970. Su disponibilidad en cantidad a 1 centavo por bit marcó el principio del fin de la memoria central.

Las mejoras en la fabricación de semiconductores condujeron a rápidos aumentos en la capacidad de almacenamiento y reducciones en el precio por kilobyte, mientras que los costos y las especificaciones de la memoria central cambiaron poco. La memoria central fue expulsada del mercado gradualmente entre 1973 y 1978.

Dependiendo de cómo esté conectada, la memoria central podría ser excepcionalmente confiable. La memoria de cuerda central de solo lectura, por ejemplo, se usó en la computadora de guía Apollo de misión crítica esencial para los alunizajes exitosos de la NASA.

Aunque la memoria central está obsoleta, la memoria de la computadora todavía se llama a veces "núcleo" a pesar de que está hecho de semiconductores, particularmente por personas que han trabajado con máquinas que tienen memoria central real. Los archivos que resultan de guardar todo el contenido de la memoria en el disco para su inspección, lo que hoy en día se realiza comúnmente de forma automática cuando ocurre un error importante en un programa informático, todavía se denominan "volcados de memoria".

Historia

Desarrolladores

El concepto básico de usar el ciclo de histéresis cuadrado de ciertos materiales magnéticos como dispositivo de almacenamiento o conmutación se conocía desde los primeros días del desarrollo de computadoras. Gran parte de este conocimiento se había desarrollado debido a la comprensión de los transformadores, que permitían la amplificación y el rendimiento similar al de un interruptor cuando se construían con ciertos materiales. El comportamiento de conmutación estable era bien conocido en el campo de la ingeniería eléctrica, y su aplicación en sistemas informáticos fue inmediata. Por ejemplo, J. Presper Eckert y Jeffrey Chuan Chu habían realizado un trabajo de desarrollo sobre el concepto en 1945 en la Escuela Moore durante los esfuerzos de ENIAC.

El pionero de la robótica George Devol presentó una patente para la primera memoria magnética estática (sin movimiento) el 3 de abril de 1946. La memoria magnética de Devol se refinó aún más a través de 5 patentes adicionales y finalmente se usó en el primer robot industrial. Frederick Viehe solicitó varias patentes sobre el uso de transformadores para construir circuitos lógicos digitales en lugar de lógica de relé a partir de 1947. En 1947 se patentó un sistema central completamente desarrollado y luego IBM lo compró en 1956. Este desarrollo era poco conocido, sin embargo, el desarrollo principal de Core normalmente se asocia con tres equipos independientes.

Los físicos estadounidenses nacidos en Shanghái An Wang y Way-Dong Woo llevaron a cabo un trabajo sustancial en este campo y crearon el dispositivo de control de transferencia de pulsos en 1949. El nombre hace referencia a la forma en que el campo magnético de los núcleos podría usarse para controlar la conmutación de corriente; su patente se centró en el uso de núcleos para crear sistemas de memoria de línea de retardo o registro de desplazamiento. Wang y Woo trabajaban en el Laboratorio de Cómputo de la Universidad de Harvard en ese momento, y la universidad no estaba interesada en promover los inventos creados en sus laboratorios. Wang pudo patentar el sistema por su cuenta.

La computadora MIT Project Whirlwind requería un sistema de memoria rápido para el seguimiento de aeronaves en tiempo real. Al principio, se utilizó una matriz de tubos Williams, un sistema de almacenamiento basado en tubos de rayos catódicos, pero resultó ser temperamental y poco confiable. Varios investigadores a fines de la década de 1940 concibieron la idea de usar núcleos magnéticos para la memoria de la computadora, pero el ingeniero informático del MIT, Jay Forrester, recibió la patente principal por su invención de la memoria central de corriente coincidente que permitió el almacenamiento de información en 3D. William Papian del Proyecto Torbellino citó uno de estos esfuerzos, la 'Línea de retardo magnético estático' de Harvard, en un memorando interno. La primera memoria de núcleo de 32 × 32 × 16 bits se instaló en Whirlwind en el verano de 1953. Papian declaró: "El almacenamiento de núcleo magnético tiene dos grandes ventajas: (1) mayor fiabilidad con la consiguiente reducción del tiempo de mantenimiento dedicado al almacenamiento; (2) tiempo de acceso más corto (el tiempo de acceso al núcleo es de 9 microsegundos: el tiempo de acceso al tubo es de aproximadamente 25 microsegundos), lo que aumenta la velocidad de funcionamiento de la computadora."

En abril de 2011, recordó Forrester, "el uso de núcleos por parte de Wang no tuvo ninguna influencia en mi desarrollo de la memoria de acceso aleatorio. La memoria de Wang era costosa y complicada. Según recuerdo, lo que puede no ser del todo correcto, usaba dos núcleos por bit binario y era esencialmente una línea de retardo que avanzaba un poco. En la medida en que me haya centrado en él, el enfoque no era adecuado para nuestros propósitos." Él describe la invención y los eventos asociados, en 1975. Desde entonces, Forrester ha observado: “Nos tomó alrededor de siete años convencer a la industria de que la memoria de núcleo magnético de acceso aleatorio era la solución a un eslabón perdido en la tecnología informática. Luego pasamos los siguientes siete años en los tribunales de patentes convenciéndolos de que no todos habían pensado en eso primero."

Un tercer desarrollador involucrado en el desarrollo inicial de Core fue Jan A. Rajchman en RCA. Como inventor prolífico, Rajchman diseñó un sistema central único utilizando bandas de ferrita envueltas alrededor de tubos metálicos delgados, construyendo sus primeros ejemplos utilizando una prensa de aspirina convertida en 1949. Más tarde, Rajchman desarrolló versiones del tubo Williams y lideró el desarrollo del Selectron.

Dos inventos clave llevaron al desarrollo de la memoria de núcleo magnético en 1951. El primero, el de An Wang, fue el ciclo de escritura después de lectura, que resolvió el problema de cómo utilizar un medio de almacenamiento en el que el El acto de leer borró los datos leídos, lo que permitió la construcción de un registro de desplazamiento unidimensional en serie (de 50 bits), utilizando dos núcleos para almacenar un bit. Un registro de desplazamiento del núcleo de Wang se encuentra en la exhibición Revolution en el Museo de Historia de la Computación. El segundo, el de Forrester, era el sistema de corriente coincidente, que permitía que una pequeña cantidad de cables controlara una gran cantidad de núcleos, lo que permitía matrices de memoria 3D de varios millones de bits. El primer uso del núcleo fue en la computadora Whirlwind, y la contribución más famosa del Proyecto Whirlwind fue la función de almacenamiento de núcleo magnético de acceso aleatorio. La comercialización siguió rápidamente. El núcleo magnético se usó en los periféricos de ENIAC en 1953, el IBM 702 entregado en julio de 1955 y más tarde en el propio 702. El IBM 704 (1954) y el Ferranti Mercury (1957) usaban memoria de núcleo magnético.

Fue a principios de la década de 1950 cuando Seeburg Corporation desarrolló una de las primeras aplicaciones comerciales de almacenamiento de memoria central de corriente coincidente en el sistema "Tormat" memoria de su nueva gama de jukeboxes, comenzando con el V200 desarrollado en 1953 y lanzado al mercado en 1955. Siguieron numerosos usos en informática, telefonía y control de procesos industriales.

Disputas de patentes

La patente de Wang no se concedió hasta 1955 y, en ese momento, la memoria de núcleo magnético ya estaba en uso. Esto inició una larga serie de juicios, que finalmente terminaron cuando IBM compró la patente directamente a Wang por 500 000 dólares estadounidenses. Wang usó los fondos para expandir en gran medida los Laboratorios Wang, que había cofundado con el Dr. Ge-Yao Chu, un compañero de escuela de China.

MIT quería cobrar a IBM $0,02 por bit de regalías en la memoria central. En 1964, después de años de disputas legales, IBM pagó al MIT 13 millones de dólares por los derechos de la patente de Forrester, el mayor acuerdo de patentes hasta la fecha.

Economía de la producción

En 1953, los núcleos probados pero aún no conectados costaban 0,33 USD cada uno. A medida que aumentaba el volumen de fabricación, en 1970 IBM producía 20 000 millones de núcleos al año y el precio por núcleo cayó a 0,0003 USD. Los tamaños de los núcleos se redujeron durante el mismo período de alrededor de 2,5 mm (0,1 pulgadas) de diámetro en la década de 1950 a 0,33 mm (0,013 pulgadas) en 1966. La potencia necesaria para cambiar la magnetización de un núcleo es proporcional al volumen, por lo que representa una caída en el consumo de energía por un factor de 125.

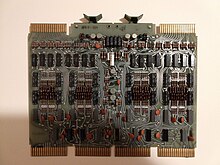

El costo de los sistemas de memoria de núcleo completo estuvo dominado por el costo de tender los cables a través de los núcleos. El sistema de corriente coincidente de Forrester requería que uno de los cables se corriera a 45 grados con respecto a los núcleos, lo que resultó difícil de cablear por máquina, por lo que los arreglos de núcleos tuvieron que ser ensamblados bajo microscopios por trabajadores con control de motor fino.

En 1956, un grupo de IBM solicitó una patente para una máquina que enhebraba automáticamente los primeros cables a través de cada núcleo. Esta máquina mantuvo el plano completo de núcleos en un 'nido'. y luego empujó una serie de agujas huecas a través de los núcleos para guiar los cables. El uso de esta máquina redujo el tiempo necesario para enhebrar las líneas rectas de selección X e Y de 25 horas a 12 minutos en una matriz de 128 por 128 núcleos.

Los núcleos más pequeños hicieron que el uso de agujas huecas fuera poco práctico, pero hubo numerosos avances en el enhebrado semiautomático de núcleos. Se desarrollaron nidos de apoyo con canales guía. Los núcleos se unieron de forma permanente a una lámina de respaldo "parche" que los apoyó durante su fabricación y uso posterior. Las agujas de enhebrar se soldaron a tope a los alambres, por lo que los diámetros de la aguja y el alambre eran los mismos, y se hicieron esfuerzos para eliminar por completo el uso de agujas.

El cambio más importante, desde el punto de vista de la automatización, fue la combinación de los cables de detección e inhibición, eliminando la necesidad de un cable de detección diagonal tortuoso. Con pequeños cambios en el diseño, esto también permitió un empaquetamiento mucho más ajustado de los núcleos en cada parche.

A principios de la década de 1960, el costo del núcleo cayó hasta el punto de que se convirtió en casi universal como memoria principal, reemplazando tanto la memoria de batería económica de bajo rendimiento como los costosos sistemas de alto rendimiento que usaban válvulas de vacío y, posteriormente, transistores discretos como memoria. El costo de la memoria central se redujo drásticamente durante la vida útil de la tecnología: los costos comenzaron en aproximadamente USD 1,00 por bit y se redujeron a aproximadamente US$0.01 por bit. El núcleo fue reemplazado por chips RAM semiconductores integrados en la década de 1970.

Un ejemplo de la escala, la economía y la tecnología de la memoria central en la década de 1960 fue la unidad de memoria central de 256 000 palabras de 36 bits (1,2 MiB) instalada en el PDP-6 en el Laboratorio de Inteligencia Artificial del MIT en 1967. Esta fue considerado "inimaginablemente enorme" en ese momento, y apodado "Moby Memory". Costó $380,000 ($0.04/bit) y medía 69 pulgadas de ancho, 50 pulgadas de alto y 25 pulgadas de profundidad con sus circuitos de soporte (189 kilobits/pie cúbico = 6,7 kilobits/litro). Su tiempo de ciclo fue de 2,75 μs.

Descripción

El término "núcleo" proviene de transformadores convencionales cuyos devanados rodean un núcleo magnético. En la memoria central, los cables pasan una vez a través de cualquier núcleo dado: son dispositivos de un solo giro. Las propiedades de los materiales utilizados para los núcleos de memoria son radicalmente diferentes de las que se utilizan en los transformadores de potencia. El material magnético para una memoria central requiere un alto grado de remanencia magnética, la capacidad de permanecer altamente magnetizado y una baja coercitividad, de modo que se requiera menos energía para cambiar la dirección de magnetización. El núcleo puede tomar dos estados, codificando un bit. El contenido de la memoria central se conserva incluso cuando el sistema de memoria se apaga (memoria no volátil). Sin embargo, cuando se lee el núcleo, se restablece a "cero" valor. Los circuitos en el sistema de memoria de la computadora luego restauran la información en un ciclo de reescritura inmediato.

Cómo funciona la memoria central

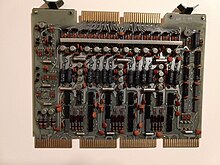

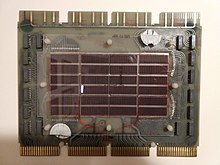

La forma más común de memoria central, corriente coincidente de línea X/Y, utilizada para la memoria principal de una computadora, consta de una gran cantidad de pequeñas ferritas cerámicas ferrimagnéticas toroidales ( núcleos) unidos en una estructura de rejilla (organizada como una "pila" de capas llamadas planos), con alambres tejidos a través de los agujeros en los núcleos' centros. En los primeros sistemas había cuatro cables: X, Y, Sensor e Inhibir, pero los núcleos posteriores combinaron los los últimos dos cables en una línea Sense/Inhibit. Cada toroide almacena un bit (0 o 1). Se podía acceder a un bit en cada plano en un ciclo, por lo que cada palabra de máquina en una matriz de palabras se distribuía en una 'pila'. de aviones Cada plano manipularía un bit de una palabra en paralelo, lo que permitiría leer o escribir la palabra completa en un ciclo.

Core se basa en el "bucle cuadrado" propiedades del material de ferrita utilizado para fabricar los toroides. Una corriente eléctrica en un cable que pasa a través de un núcleo crea un campo magnético. Solo un campo magnético superior a una determinada intensidad ("seleccionar") puede hacer que el núcleo cambie su polaridad magnética. Para seleccionar una ubicación de memoria, una de las líneas X y una de las Y se activan con la mitad de la corriente ("media selección") necesaria para provocar este cambio. Solo el campo magnético combinado generado donde se cruzan las líneas X e Y (una función AND lógica) es suficiente para cambiar el estado; otros núcleos verán solo la mitad del campo necesario ("seleccionado a la mitad"), o ninguno en absoluto. Al conducir la corriente a través de los cables en una dirección particular, el campo inducido resultante obliga al flujo magnético del núcleo seleccionado a circular en una dirección u otra (hacia la derecha o hacia la izquierda). Una dirección es un 1 almacenado, mientras que la otra es un 0 almacenado.

Se prefiere la forma toroidal de un núcleo ya que el camino magnético está cerrado, no hay polos magnéticos y, por lo tanto, hay muy poco flujo externo. Esto permite que los núcleos se empaqueten muy juntos sin permitir que sus campos magnéticos interactúen. Los cables sensores diagonales requerían el posicionamiento alterno de 45 grados utilizado en los primeros conjuntos de núcleos. Con la eliminación de estos alambres diagonales, fue posible un empaque más apretado.

Leer y escribir

Para leer un poco de la memoria del núcleo, el circuito intenta cambiar el bit a la polaridad asignada al estado 0, activando las líneas X e Y seleccionadas que se cruzan en ese núcleo.

- Si el bit ya era 0, el estado físico del núcleo no es afectado.

- Si el bit era anteriormente 1, entonces el núcleo cambia la polaridad magnética. Este cambio, después de un retraso, induce un pulso de tensión en la línea Sense.

La detección de dicho pulso significa que el bit contenía un 1 más recientemente. La ausencia del pulso significa que el bit contenía un 0. La demora en detectar el pulso de voltaje se denomina tiempo de acceso. b> de la memoria central.

Después de cualquier lectura de este tipo, el bit contiene un 0. Esto ilustra por qué un acceso a la memoria del núcleo se denomina lectura destructiva: cualquier operación que lea el contenido de un núcleo borra ese contenido y debe ser recreado inmediatamente.

Para escribir un bit de memoria central, el circuito asume que ha habido una operación de lectura y que el bit está en estado 0.

- Para escribir un poco, las líneas X y Y seleccionadas son impulsadas, con corriente en la dirección opuesta en cuanto a la operación de lectura. Como con la lectura, el núcleo de la intersección de las líneas X y Y cambia la polaridad magnética.

- Para escribir un poco, se pueden aplicar dos métodos. El primero es el mismo que el proceso de lectura con corriente en la dirección original. La segunda ha revertido la lógica. Escribe 0 bit, en otras palabras, es inhibir la escritura de un poco. La misma cantidad de corriente también se envía a través de la línea Inhibit. Esto reduce la corriente neta fluyendo a través del núcleo respectivo a la mitad de la corriente selecta, inhibiendo el cambio de polaridad.

El tiempo de acceso más el tiempo de reescritura es el tiempo del ciclo de memoria.

El cable de detección se usa solo durante la lectura y el cable de inhibición solo se usa durante la escritura. Por esta razón, los sistemas centrales posteriores combinaron los dos en un solo cable y utilizaron circuitos en el controlador de memoria para cambiar la función del cable. Sin embargo, cuando el cable Sense cruza demasiados núcleos, la corriente de selección media también puede inducir un voltaje considerable en toda la línea debido a la superposición del voltaje en cada núcleo individual. Este riesgo potencial de "lectura incorrecta" limita el número mínimo del cable Sense. El aumento de los cables de detección requiere más circuitos de decodificación.

Los controladores de memoria central fueron diseñados para que cada lectura fuera seguida inmediatamente por una escritura (porque la lectura obligó a todos los bits a 0 y porque la escritura asumió que esto había sucedido). Las computadoras comenzaron a aprovechar este hecho. Por ejemplo, un valor en la memoria podría leerse e incrementarse (como por ejemplo mediante la instrucción AOS en el PDP-6) casi tan rápido como podría leerse; el hardware simplemente incrementó el valor entre la fase de lectura y la fase de escritura de un solo ciclo de memoria (tal vez indicando al controlador de memoria que se detuviera brevemente en medio del ciclo). Esto podría ser el doble de rápido que el proceso de obtener el valor con un ciclo de lectura y escritura, incrementar el valor en algún registro del procesador y luego escribir el nuevo valor con otro ciclo de lectura y escritura.

Otras formas de memoria central

línea de palabra se usaba a menudo para proporcionar memoria de registro. Otros nombres para este tipo son selección lineal y 2-D. Esta forma de memoria central generalmente tejía tres cables a través de cada núcleo en el plano, lectura de palabras, escritura de palabras y sentido/escritura de bits. Para leer o borrar palabras, la corriente completa se aplica a una o más líneas de lectura de palabras; esto borra los núcleos seleccionados y cualquiera que induzca pulsos de voltaje en sus líneas de bit sense/write. Para leer, normalmente solo se seleccionaría una línea de palabra de lectura; pero para que quede claro, se pueden seleccionar varias líneas de palabra de lectura mientras se ignoran las líneas de bit sense/write. Para escribir palabras, la mitad de la corriente se aplica a una o más líneas word write, y la mitad de la corriente se aplica a cada línea bit sense/write para establecer un bit. En algunos diseños, las líneas de lectura de palabras y escritura de palabras se combinaron en un solo cable, lo que resultó en una matriz de memoria con solo dos cables por bit. Para escribir, se pueden seleccionar varias líneas de escritura de palabras. Esto ofrecía una ventaja de rendimiento sobre la corriente coincidente de línea X/Y en el sentido de que se podían borrar o escribir varias palabras con el mismo valor en un solo ciclo. El conjunto de registros de una máquina típica generalmente usaba solo un plano pequeño de esta forma de memoria central. Algunas memorias muy grandes se construyeron con esta tecnología, por ejemplo, la memoria auxiliar Extended Core Storage (ECS) en el CDC 6600, que era de hasta 2 millones de palabras de 60 bits.

Otra forma de memoria central llamada memoria de cuerda central proporcionaba almacenamiento de solo lectura. En este caso, los núcleos, que tenían materiales magnéticos más lineales, se utilizaron simplemente como transformadores; ninguna información se almacenó magnéticamente dentro de los núcleos individuales. Cada parte de la palabra tenía un núcleo. La lectura del contenido de una dirección de memoria dada generó un pulso de corriente en un cable correspondiente a esa dirección. Cada cable de dirección se enhebró a través de un núcleo para indicar un binario [1], o alrededor del exterior de ese núcleo, para indicar un binario [0]. Como era de esperar, los núcleos eran mucho más grandes físicamente que los de la memoria central de lectura y escritura. Este tipo de memoria era excepcionalmente confiable. Un ejemplo fue la computadora de guía Apollo utilizada para los alunizajes de la NASA.

Características físicas

El rendimiento de las primeras memorias centrales se puede caracterizar en términos actuales como comparable a una velocidad de reloj de 1 MHz (equivalente a las computadoras domésticas de principios de la década de 1980, como Apple II y Commodore 64). Los primeros sistemas de memoria central tenían tiempos de ciclo de aproximadamente 6 µs, que habían caído a 1,2 µs a principios de la década de 1970 y, a mediados de la década de 1970, se redujeron a 600 ns (0,6 µs). Algunos diseños tenían un rendimiento sustancialmente mayor: el CDC 6600 tenía un tiempo de ciclo de memoria de 1,0 µs en 1964, utilizando núcleos que requerían una corriente de selección media de 200 mA. Se hizo todo lo posible para disminuir los tiempos de acceso y aumentar las tasas de datos (ancho de banda), incluido el uso simultáneo de múltiples cuadrículas de núcleo, cada una de las cuales almacena un bit de una palabra de datos. Por ejemplo, una máquina podría usar 32 cuadrículas de núcleo con un solo bit de la palabra de 32 bits en cada una, y el controlador podría acceder a la palabra completa de 32 bits en un solo ciclo de lectura/escritura.

La memoria central es un almacenamiento no volátil: puede retener su contenido indefinidamente sin energía. También es relativamente poco afectado por EMP y radiación. Estas fueron ventajas importantes para algunas aplicaciones, como controladores programables industriales de primera generación, instalaciones militares y vehículos como aviones de combate, así como naves espaciales, y llevaron al uso del núcleo durante varios años después de la disponibilidad de la memoria MOS de semiconductores (ver también MOSFET). Por ejemplo, las computadoras de vuelo del transbordador espacial IBM AP-101B usaban memoria central, que preservaba el contenido de la memoria incluso a través del Challenger's desintegración y posterior zambullida en el mar en 1986. Otra característica del núcleo inicial era que la fuerza coercitiva era muy sensible a la temperatura; la corriente semiseleccionada adecuada a una temperatura no es la corriente semiseleccionada adecuada a otra temperatura. Entonces, un controlador de memoria incluiría un sensor de temperatura (típicamente un termistor) para ajustar los niveles actuales correctamente para los cambios de temperatura. Un ejemplo de esto es la memoria central utilizada por Digital Equipment Corporation para su computadora PDP-1; esta estrategia continuó a través de todos los sistemas de memoria central de seguimiento construidos por DEC para su línea PDP de computadoras enfriadas por aire. Otro método para manejar la sensibilidad a la temperatura era encerrar la 'pila' del núcleo magnético. en un horno de temperatura controlada. Ejemplos de esto son la memoria central de aire caliente del IBM 1620 (que podría tardar hasta 30 minutos en alcanzar la temperatura de funcionamiento, alrededor de 41 °C (106 °F)) y la memoria central en baño de aceite calentado del IBM 7090, primeros IBM 7094 e IBM 7030.

El núcleo se calentó en lugar de enfriarse porque el requisito principal era una temperatura consistente y era más fácil (y más económico) mantener una temperatura constante muy por encima de la temperatura ambiente que una temperatura igual o inferior a ella.

En 1980, el precio de una placa de memoria central de 16 kW (kilopalabra, equivalente a 32 kB) que se instalaba en una computadora DEC Q-bus rondaba los US$3000. En ese momento, la matriz de núcleos y la electrónica de soporte cabían en una sola placa de circuito impreso de aproximadamente 25 × 20 cm de tamaño, la matriz de núcleos se montaba unos pocos milímetros por encima de la placa de circuito impreso y se protegía con una placa de metal o plástico.

El diagnóstico de problemas de hardware en la memoria central requería la ejecución de programas de diagnóstico que consumían mucho tiempo. Si bien una prueba rápida verificó si cada bit podía contener un uno y un cero, estos diagnósticos probaron la memoria central con los patrones del peor de los casos y tuvieron que ejecutarse durante varias horas. Como la mayoría de las computadoras tenían solo una placa de memoria de un solo núcleo, estos diagnósticos también se movieron en la memoria, lo que hizo posible probar cada bit. Una prueba avanzada se denominó "prueba de Shmoo" en el que se modificaron las corrientes de selección media junto con el tiempo en el que se probó la línea de detección ("estroboscópica"). La gráfica de datos de esta prueba parecía parecerse a un personaje de dibujos animados llamado "Shmoo," y el nombre se quedó. En muchas ocasiones, los errores se pueden resolver golpeando suavemente la placa de circuito impreso con la matriz central sobre una mesa. Esto cambió ligeramente las posiciones de los núcleos a lo largo de los cables que los atraviesan y podría solucionar el problema. El procedimiento rara vez fue necesario, ya que la memoria central demostró ser muy confiable en comparación con otros componentes informáticos de la época.

Contenido relacionado

Historia de la ingeniería en sistemas

Computadora Atanasoff-Berry

Mandriva linux