Interrumpir

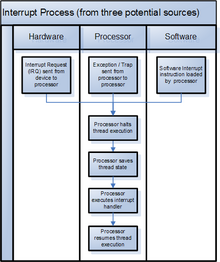

En las computadoras digitales, una interrupción (a veces denominada trampa) es una solicitud para que el procesador interrumpa el código que se está ejecutando actualmente (cuando esté permitido), para que el evento pueda ser procesado en tiempo y forma. Si se acepta la solicitud, el procesador suspenderá sus actividades actuales, guardará su estado y ejecutará una función llamada controlador de interrupciones (o una rutina de servicio de interrupciones, ISR) para tratar el evento. Esta interrupción suele ser temporal, lo que permite que el software reanude sus actividades normales después de que finalice el controlador de interrupciones, aunque la interrupción podría indicar un error fatal.

Los dispositivos de hardware suelen utilizar interrupciones para indicar cambios de estado electrónicos o físicos que requieren una atención urgente. Las interrupciones también se utilizan comúnmente para implementar la multitarea informática, especialmente en la informática en tiempo real. Se dice que los sistemas que usan interrupciones de esta manera están controlados por interrupciones.

Tipos

Se pueden emitir señales de interrupción en respuesta a eventos de hardware o software. Estas se clasifican como interrupciones de hardware o interrupciones de software, respectivamente. Para cualquier procesador en particular, el número de tipos de interrupción está limitado por la arquitectura.

Interrupciones de hardware

Una interrupción de hardware es una condición relacionada con el estado del hardware que puede ser señalada por un dispositivo de hardware externo, por ejemplo, una línea de solicitud de interrupción (IRQ) en una PC, o detectada por dispositivos integrados en la lógica del procesador (por ejemplo, el temporizador de la CPU en IBM System/370), para comunicar que el dispositivo necesita atención del sistema operativo (SO) o, si no hay SO, del "bare-metal" programa que se ejecuta en la CPU. Dichos dispositivos externos pueden ser parte de la computadora (por ejemplo, un controlador de disco) o pueden ser periféricos externos. Por ejemplo, presionar una tecla del teclado o mover un mouse conectado a un puerto PS/2 desencadena interrupciones de hardware que hacen que el procesador lea la posición del mouse o la pulsación de tecla.

Las interrupciones de hardware pueden llegar de forma asincrónica con respecto al reloj del procesador y en cualquier momento durante la ejecución de la instrucción. En consecuencia, todas las señales de interrupción de hardware entrantes se condicionan al sincronizarlas con el reloj del procesador, y se actúa solo en los límites de ejecución de instrucciones.

En muchos sistemas, cada dispositivo está asociado con una señal IRQ particular. Esto hace posible determinar rápidamente qué dispositivo de hardware está solicitando servicio y agilizar el servicio de ese dispositivo.

En algunos sistemas más antiguos, como el CDC 3600 de 1964, todas las interrupciones iban a la misma ubicación y el sistema operativo usaba una instrucción especializada para determinar la interrupción sin enmascarar pendiente de mayor prioridad. En los sistemas contemporáneos, generalmente hay una rutina de interrupción distinta para cada tipo de interrupción (o para cada fuente de interrupción), a menudo implementada como una o más tablas de vectores de interrupción.

Enmascaramiento

Enmascarar una interrupción es deshabilitarla, por lo que el procesador la aplaza o la ignora, mientras que desenmascarar una interrupción es habilitarla.

Los procesadores suelen tener un registro interno de máscara de interrupción, que permite habilitar (y deshabilitar) selectivamente las interrupciones de hardware. Cada señal de interrupción está asociada con un bit en el registro de máscara. En algunos sistemas, la interrupción se habilita cuando se establece el bit y se desactiva cuando el bit se borra. En otros, lo contrario es cierto y un bit establecido desactiva la interrupción. Cuando la interrupción está deshabilitada, el procesador puede ignorar la señal de interrupción asociada o puede permanecer pendiente. Las señales que se ven afectadas por la máscara se denominan interrupciones enmascarables.

Algunas señales de interrupción no se ven afectadas por la máscara de interrupción y, por lo tanto, no se pueden desactivar; estas se denominan interrupciones no enmascarables (NMI). Estos indican eventos de alta prioridad que no se pueden ignorar bajo ninguna circunstancia, como la señal de tiempo de espera de un temporizador de vigilancia.

Interrupciones falsas

Una interrupción espuria es una interrupción de hardware para la cual no se puede encontrar una fuente. El término "interrupción fantasma" o "interrupción fantasma" también puede usarse para describir este fenómeno. Las interrupciones espurias tienden a ser un problema con un circuito de interrupción cableado-OR conectado a una entrada de procesador sensible al nivel. Tales interrupciones pueden ser difíciles de identificar cuando un sistema se comporta mal.

En un circuito OR cableado, la carga/descarga de capacitancia parásita a través de la resistencia de polarización de la línea de interrupción causará una pequeña demora antes de que el procesador reconozca que la fuente de interrupción se ha eliminado. Si el dispositivo de interrupción se borra demasiado tarde en la rutina de servicio de interrupción (ISR), no habrá tiempo suficiente para que el circuito de interrupción vuelva al estado de reposo antes de que finalice la instancia actual de ISR. El resultado es que el procesador pensará que hay otra interrupción pendiente, ya que el voltaje en su entrada de solicitud de interrupción no será lo suficientemente alto o bajo para establecer un 1 lógico interno inequívoco o un 0 lógico interno. La interrupción aparente no tendrá una fuente identificable, por lo tanto, el & #34;falso" apodo

Una interrupción espuria también puede ser el resultado de anomalías eléctricas debido a un diseño de circuito defectuoso, altos niveles de ruido, diafonía, problemas de sincronización o, más raramente, erratas del dispositivo.

Una interrupción espuria puede resultar en un interbloqueo del sistema u otra operación indefinida si el ISR no tiene en cuenta la posibilidad de que ocurra tal interrupción. Como las interrupciones espurias son en su mayoría un problema con los circuitos de interrupción cableados-OR, una buena práctica de programación en dichos sistemas es que el ISR verifique todas las fuentes de interrupción en busca de actividad y no tome ninguna acción (aparte de posiblemente registrar el evento) si ninguna de las fuentes está interrumpiendo..

Interrupciones de software

El propio procesador solicita una interrupción de software al ejecutar instrucciones particulares o cuando se cumplen ciertas condiciones. Cada señal de interrupción de software está asociada con un controlador de interrupción particular.

Una interrupción de software puede ser causada intencionalmente al ejecutar una instrucción especial que, por diseño, invoca una interrupción cuando se ejecuta. Estas instrucciones funcionan de manera similar a las llamadas a subrutinas y se utilizan para una variedad de propósitos, como solicitar servicios del sistema operativo e interactuar con controladores de dispositivos (por ejemplo, para leer o escribir medios de almacenamiento). Las interrupciones de software también pueden ser provocadas por errores de ejecución del programa o por el sistema de memoria virtual.

Normalmente, el kernel del sistema operativo detectará y manejará dichas interrupciones. Algunas interrupciones se manejan de forma transparente para el programa; por ejemplo, la resolución normal de una falla de página es hacer que la página requerida sea accesible en la memoria física. Pero en otros casos, como una falla de segmentación, el sistema operativo ejecuta una devolución de llamada del proceso. En los sistemas operativos similares a Unix, esto implica enviar una señal como SIGSEGV, SIGBUS, SIGILL o SIGFPE, que puede llamar a un controlador de señal o ejecutar una acción predeterminada (terminar el programa). En Windows, la devolución de llamada se realiza mediante el manejo estructurado de excepciones con un código de excepción como STATUS_ACCESS_VIOLATION o STATUS_INTEGER_DIVIDE_BY_ZERO.

En un proceso del núcleo, a menudo se supone que no deben ocurrir algunos tipos de interrupciones de software. Si ocurren a pesar de todo, es posible que se bloquee el sistema operativo.

Terminología

Los términos interrupción, trampa, excepción, fallo y abortar se utilizan para distinguir tipos de interrupciones, aunque "no existe un consenso claro en cuanto al significado exacto de estos términos". El término trampa puede referirse a cualquier interrupción, a cualquier interrupción de software, a cualquier interrupción de software síncrona, o solo a interrupciones causadas por instrucciones con trampa en sus nombres. En algunos usos, el término trampa se refiere específicamente a un punto de interrupción destinado a iniciar un cambio de contexto a un programa de supervisión o depurador. También puede referirse a una interrupción síncrona causada por una condición excepcional (por ejemplo, división por cero, acceso a memoria inválido, código de operación ilegal), aunque el término excepción es más común para esto.

x86 divide las interrupciones en interrupciones (de hardware) y excepciones de software, e identifica tres tipos de excepciones: fallas, trampas y anulaciones. Las interrupciones (de hardware) son interrupciones activadas de forma asíncrona por un dispositivo de E/S y permiten que el programa se reinicie sin pérdida de continuidad. Una falla también se puede reiniciar, pero está vinculada a la ejecución síncrona de una instrucción: la dirección de retorno apunta a la instrucción que falla. Una captura es similar a una falla, excepto que la dirección de retorno apunta a la instrucción que se ejecutará después de la instrucción de captura; un uso destacado es implementar llamadas al sistema. Un aborto se usa para errores graves, como errores de hardware y valores ilegales en las tablas del sistema, y a menudo no permite reiniciar el programa.

ARM usa el término excepción para referirse a todos los tipos de interrupciones, y divide las excepciones en (hardware) interrupciones, abortos, restablecer e instrucciones de generación de excepciones. Los abortos corresponden a excepciones x86 y pueden ser abortos de búsqueda previa (obtenciones de instrucciones fallidas) o abortos de datos (accesos de datos fallidos), y pueden ser síncronos o asíncronos. Los abortos asíncronos pueden ser precisos o imprecisos. Los abortos de MMU (fallos de página) son sincrónicos.

Métodos de activación

Cada entrada de señal de interrupción está diseñada para ser activada por un nivel de señal lógica o por un borde de señal particular (transición de nivel). Las entradas sensibles al nivel solicitan continuamente el servicio del procesador siempre que se aplique un nivel lógico particular (alto o bajo) a la entrada. Las entradas sensibles a los flancos reaccionan a los flancos de la señal: un flanco particular (ascendente o descendente) hará que se bloquee una solicitud de servicio; el procesador restablece el pestillo cuando se ejecuta el controlador de interrupción.

Activado por nivel

Se solicita una interrupción activada por nivel manteniendo la señal de interrupción en su nivel lógico activo particular (alto o bajo). Un dispositivo invoca una interrupción activada por nivel llevando la señal y manteniéndola en el nivel activo. Niega la señal cuando el procesador se lo ordena, generalmente después de que se haya reparado el dispositivo.

El procesador muestrea la señal de entrada de interrupción durante cada ciclo de instrucción. El procesador reconocerá la solicitud de interrupción si la señal se afirma cuando ocurre el muestreo.

Las entradas activadas por nivel permiten que varios dispositivos compartan una señal de interrupción común a través de conexiones O cableadas. El procesador sondea para determinar qué dispositivos están solicitando servicio. Después de dar servicio a un dispositivo, el procesador puede sondear nuevamente y, si es necesario, dar servicio a otros dispositivos antes de salir del ISR.

Desencadenada por el borde

(feminine)Una interrupción activada por flanco es una interrupción señalada por una transición de nivel en la línea de interrupción, ya sea un flanco descendente (de mayor a menor) o un flanco ascendente (de menor a mayor). Un dispositivo que desea señalar una interrupción envía un pulso a la línea y luego libera la línea a su estado inactivo. Si el pulso es demasiado corto para ser detectado por la E/S encuestada, es posible que se requiera un hardware especial para detectarlo. La parte importante de la activación por flanco es que la señal debe hacer la transición para activar la interrupción; por ejemplo, si la señal fuera alta-baja-baja, solo se activaría una interrupción de flanco descendente y el nivel bajo continuado no desencadenaría una interrupción adicional. La señal debe volver al nivel alto y caer de nuevo para activar una nueva interrupción. Esto contrasta con un disparador de nivel donde el nivel bajo continuaría creando interrupciones (si están habilitadas) hasta que la señal regrese a su nivel alto.

Las computadoras con interrupciones activadas por borde pueden incluir un registro de interrupción que retiene el estado de las interrupciones pendientes. Los sistemas con registros de interrupción generalmente también tienen registros de máscara de interrupción.

Respuesta del procesador

El procesador muestrea las señales de activación de interrupción o el registro de interrupción durante cada ciclo de instrucción y procesará la interrupción habilitada de mayor prioridad encontrada. Independientemente del método de disparo, el procesador comenzará el procesamiento de interrupciones en el siguiente límite de instrucción después de un disparo detectado, asegurando así:

- El estado del procesador se salva de una manera conocida. Típicamente el estado se almacena en una ubicación conocida, pero en algunos sistemas se almacena en una pila.

- Todas las instrucciones antes del apuntado por el PC han ejecutado completamente.

- Ninguna instrucción más allá de la señalada por el PC ha sido ejecutada, o ninguna de estas instrucciones se deshacen antes de manejar la interrupción.

- Se conoce el estado de ejecución de la instrucción señalada por el PC.

Implementación del sistema

Las interrupciones se pueden implementar en el hardware como un componente distinto con líneas de control, o se pueden integrar en el subsistema de memoria.

Si se implementa en el hardware como un componente distinto, se puede conectar un circuito controlador de interrupción, como el controlador de interrupción programable (PIC) de IBM PC, entre el dispositivo de interrupción y el pin de interrupción del procesador para multiplexar varios fuentes de interrupción en una o dos líneas de CPU típicamente disponibles. Si se implementa como parte del controlador de memoria, las interrupciones se asignan al espacio de direcciones de memoria del sistema.

IRQ compartidas

Múltiples dispositivos pueden compartir una línea de interrupción activada por borde si están diseñados para ello. La línea de interrupción debe tener una resistencia pull-down o pull-up para que, cuando no se accione activamente, se establezca en su estado inactivo, que es el estado predeterminado. Los dispositivos señalan una interrupción conduciendo brevemente la línea a su estado no predeterminado y dejan que la línea flote (no la controlen activamente) cuando no están señalando una interrupción. Este tipo de conexión también se conoce como colector abierto. La línea entonces transporta todos los pulsos generados por todos los dispositivos. (Esto es similar al cordón de tracción en algunos autobuses y trolebuses que cualquier pasajero puede tirar para indicarle al conductor que está solicitando una parada). Sin embargo, los pulsos de interrupción de diferentes dispositivos pueden fusionarse si ocurren cerca en el tiempo. Para evitar perder interrupciones, la CPU debe disparar en el borde posterior del pulso (por ejemplo, el borde ascendente si la línea se eleva y se reduce). Después de detectar una interrupción, la CPU debe verificar todos los dispositivos para conocer los requisitos de servicio.

Las interrupciones activadas por borde no sufren los problemas que tienen las interrupciones activadas por nivel con el uso compartido. El servicio de un dispositivo de baja prioridad se puede posponer arbitrariamente, mientras que las interrupciones de los dispositivos de alta prioridad continúan recibiéndose y recibiendo servicio. Si hay un dispositivo que la CPU no sabe cómo reparar, lo que puede generar interrupciones falsas, no interferirá con la señalización de interrupción de otros dispositivos. Sin embargo, es fácil pasar por alto una interrupción activada por borde, por ejemplo, cuando las interrupciones están enmascaradas durante un período, y a menos que haya algún tipo de pestillo de hardware que registre el evento, es imposible recuperarlo. Este problema causó muchos "bloqueos" en el hardware de las primeras computadoras porque el procesador no sabía que se esperaba que hiciera algo. El hardware más moderno a menudo tiene uno o más registros de estado de interrupción que bloquean las solicitudes de interrupción; un código de manejo de interrupciones basado en el borde bien escrito puede verificar estos registros para garantizar que no se pierda ningún evento.

El antiguo bus Industry Standard Architecture (ISA) utiliza interrupciones activadas por borde, sin exigir que los dispositivos puedan compartir líneas IRQ, pero todas las placas base ISA convencionales incluyen resistencias pull-up en sus líneas IRQ, por lo que los dispositivos ISA se comportan bien compartir líneas IRQ debería funcionar bien. El puerto paralelo también utiliza interrupciones activadas por borde. Muchos dispositivos más antiguos asumen que tienen un uso exclusivo de las líneas IRQ, lo que hace que sea eléctricamente inseguro compartirlas.

Hay 3 formas en que múltiples dispositivos "compartiendo la misma línea" se puede levantar Primero es por conducción exclusiva (conmutación) o conexión exclusiva (a pines). El siguiente es en bus (todos conectados a la misma línea de escucha): las tarjetas en un bus deben saber cuándo deben hablar y no hablar (es decir, el bus ISA). La conversación se puede activar de dos maneras: por pestillo de acumulación o por puertas lógicas. Las puertas lógicas esperan un flujo de datos continuo que se monitorea en busca de señales clave. Los acumuladores solo se disparan cuando el lado remoto excita la puerta más allá de un umbral, por lo que no se requiere una velocidad negociada. Cada uno tiene sus ventajas de velocidad versus distancia. Un disparador, generalmente, es el método en el que se detecta la excitación: flanco ascendente, flanco descendente, umbral (el osciloscopio puede disparar una amplia variedad de formas y condiciones).

La activación de interrupciones de software debe estar integrada en el software (tanto en el sistema operativo como en la aplicación). A 'C' La aplicación tiene una tabla de activación (una tabla de funciones) en su encabezado, que tanto la aplicación como el sistema operativo conocen y usan adecuadamente y que no está relacionada con el hardware. Sin embargo, no confunda esto con las interrupciones de hardware que envían señales a la CPU (la CPU ejecuta el software a partir de una tabla de funciones, de manera similar a las interrupciones de software).

Dificultades para compartir líneas de interrupción

Múltiples dispositivos que comparten una línea de interrupción (de cualquier estilo de activación) actúan como fuentes de interrupción espurias entre sí. Con muchos dispositivos en una línea, la carga de trabajo en el servicio de interrupciones crece en proporción al cuadrado de la cantidad de dispositivos. Por lo tanto, se prefiere repartir los dispositivos de manera uniforme en las líneas de interrupción disponibles. La escasez de líneas de interrupción es un problema en los diseños de sistemas más antiguos donde las líneas de interrupción son conductores físicos distintos. Las interrupciones señaladas por mensaje, donde la línea de interrupción es virtual, son preferidas en las nuevas arquitecturas de sistemas (como PCI Express) y alivian este problema en gran medida.

Algunos dispositivos con una interfaz de programación mal diseñada no proporcionan ninguna forma de determinar si han solicitado servicio. Pueden bloquearse o comportarse mal si se les da servicio cuando no lo desean. Dichos dispositivos no pueden tolerar interrupciones espurias y, por lo tanto, tampoco pueden tolerar compartir una línea de interrupción. Las tarjetas ISA, debido a su diseño y construcción a menudo baratos, son notorias por este problema. Dichos dispositivos se están volviendo mucho más raros, ya que la lógica del hardware se vuelve más barata y las nuevas arquitecturas de sistemas exigen interrupciones compartibles.

Híbrida

(feminine)Algunos sistemas utilizan un híbrido de señalización activada por nivel y activada por borde. El hardware no solo busca un borde, sino que también verifica que la señal de interrupción permanezca activa durante un cierto período de tiempo.

Un uso común de una interrupción híbrida es para la entrada NMI (interrupción no enmascarable). Debido a que los NMI generalmente señalan eventos importantes, o incluso catastróficos, del sistema, una buena implementación de esta señal intenta garantizar que la interrupción sea válida verificando que permanezca activa durante un período de tiempo. Este enfoque de 2 pasos ayuda a evitar que las interrupciones falsas afecten al sistema.

Mensaje señalado

Una interrupción señalada por mensaje no utiliza una línea de interrupción física. En cambio, un dispositivo señala su solicitud de servicio mediante el envío de un mensaje corto a través de algún medio de comunicación, generalmente un bus de computadora. El mensaje puede ser de un tipo reservado para interrupciones o puede ser de algún tipo preexistente, como una escritura de memoria.

Las interrupciones señaladas por mensaje se comportan de manera muy parecida a las interrupciones activadas por borde, en el sentido de que la interrupción es una señal momentánea en lugar de una condición continua. El software de manejo de interrupciones trata a los dos de la misma manera. Por lo general, se permite la fusión de múltiples interrupciones señaladas por mensajes pendientes con el mismo mensaje (la misma línea de interrupción virtual), al igual que se pueden fusionar las interrupciones activadas por borde muy próximas entre sí.

Los vectores de interrupción señalados por mensaje se pueden compartir, en la medida en que se pueda compartir el medio de comunicación subyacente. No se requiere ningún esfuerzo adicional.

Debido a que la identidad de la interrupción se indica mediante un patrón de bits de datos, que no requiere un conductor físico separado, se pueden manejar de manera eficiente muchas más interrupciones distintas. Esto reduce la necesidad de compartir. Los mensajes de interrupción también se pueden pasar a través de un bus serie, sin necesidad de líneas adicionales.

PCI Express, un bus de computadora en serie, utiliza exclusivamente interrupciones señalizadas por mensajes.

Timbre

En una analogía de botón pulsador aplicada a los sistemas informáticos, el término timbre o interrupción del timbre se utiliza a menudo para describir un mecanismo mediante el cual un sistema de software puede señalar o notificar a una computadora dispositivo de hardware que hay algo de trabajo por hacer. Por lo general, el sistema de software colocará los datos en algunas ubicaciones de memoria bien conocidas y acordadas mutuamente, y "tocará el timbre" escribiendo en una ubicación de memoria diferente. Esta ubicación de memoria diferente a menudo se denomina región del timbre, e incluso puede haber varios timbres que cumplen diferentes propósitos en esta región. Es este acto de escribir en la región del timbre de la memoria lo que "toca el timbre" y notifica al dispositivo de hardware que los datos están listos y esperando. El dispositivo de hardware ahora sabría que los datos son válidos y se puede actuar sobre ellos. Por lo general, escribiría los datos en una unidad de disco duro, los enviaría a través de una red, los cifraría, etc.

El término interrupción del timbre suele ser un nombre inapropiado. Es similar a una interrupción, porque hace que el dispositivo realice algún trabajo; sin embargo, la región del timbre a veces se implementa como una región de sondeo, a veces la región del timbre escribe a través de los registros del dispositivo físico y, a veces, la región del timbre está conectada directamente a los registros del dispositivo físico. Al escribir a través o directamente en los registros del dispositivo físico, esto puede causar una interrupción real en la unidad central de procesamiento (CPU) del dispositivo, si tiene una.

Las interrupciones del timbre se pueden comparar con las interrupciones señaladas por mensaje, ya que tienen algunas similitudes.

IPI multiprocesador

En sistemas multiprocesador, un procesador puede enviar una solicitud de interrupción a otro procesador a través de interrupciones entre procesadores (IPI).

Rendimiento

Las interrupciones proporcionan una sobrecarga baja y una buena latencia con poca carga, pero se degradan significativamente con una tasa de interrupción alta, a menos que se tenga cuidado para evitar varias patologías. El fenómeno en el que el rendimiento general del sistema se ve gravemente obstaculizado por cantidades excesivas de tiempo de procesamiento dedicado al manejo de interrupciones se denomina tormenta de interrupciones.

Hay varias formas de bloqueos dinámicos, cuando el sistema pasa todo su tiempo procesando interrupciones y excluyendo otras tareas requeridas. En condiciones extremas, una gran cantidad de interrupciones (como un tráfico de red muy alto) pueden paralizar completamente el sistema. Para evitar tales problemas, un sistema operativo debe programar el manejo de interrupciones de red con el mismo cuidado con el que programa la ejecución del proceso.

Con los procesadores multinúcleo, se pueden lograr mejoras de rendimiento adicionales en el manejo de interrupciones a través del escalado del lado de recepción (RSS) cuando se utilizan NIC de varias colas. Tales NIC proporcionan múltiples colas de recepción asociadas a interrupciones separadas; al enrutar cada una de esas interrupciones a diferentes núcleos, el procesamiento de las solicitudes de interrupción desencadenadas por el tráfico de red recibido por una sola NIC se puede distribuir entre varios núcleos. El sistema operativo puede realizar automáticamente la distribución de las interrupciones entre los núcleos, o el enrutamiento de las interrupciones (normalmente denominado afinidad IRQ) puede configurarse manualmente.

Una implementación puramente basada en software de la distribución del tráfico de recepción, conocida como dirección de paquetes de recepción (RPS), distribuye el tráfico recibido entre los núcleos más adelante en la ruta de datos, como parte de la funcionalidad del controlador de interrupciones. Las ventajas de RPS sobre RSS incluyen requisitos de hardware específico, filtros de distribución de tráfico más avanzados y una tasa reducida de interrupciones producidas por una NIC. Como desventaja, RPS aumenta la tasa de interrupciones entre procesadores (IPI). La dirección de flujo de recepción (RFS) lleva el enfoque basado en software más allá al tener en cuenta la localidad de la aplicación; Se logran mejoras adicionales en el rendimiento procesando las solicitudes de interrupción por los mismos núcleos en los que la aplicación de destino consumirá los paquetes de red específicos.

Usos típicos

Las interrupciones se usan comúnmente para dar servicio a los temporizadores de hardware, transferir datos hacia y desde el almacenamiento (p. ej., E/S de disco) e interfaces de comunicación (p. ej., UART, Ethernet), manejar eventos de teclado y mouse, y para responder a cualquier otro momento. -eventos sensibles según lo requiera el sistema de aplicación. Las interrupciones no enmascarables generalmente se usan para responder a solicitudes de alta prioridad, como tiempos de espera del temporizador de vigilancia, señales de apagado y trampas.

Los temporizadores de hardware se utilizan a menudo para generar interrupciones periódicas. En algunas aplicaciones, el controlador de interrupciones cuenta dichas interrupciones para realizar un seguimiento del tiempo absoluto o transcurrido, o el programador de tareas del sistema operativo las utiliza para administrar la ejecución de los procesos en ejecución, o ambas cosas. Las interrupciones periódicas también se usan comúnmente para invocar el muestreo de dispositivos de entrada como convertidores de analógico a digital, interfaces de codificador incremental y entradas GPIO, y para programar dispositivos de salida como convertidores de digital a analógico, controladores de motor y salidas GPIO.

Una interrupción de disco señala la finalización de una transferencia de datos desde o hacia el periférico de disco; esto puede hacer que se ejecute un proceso que está esperando para leer o escribir. Una interrupción de apagado predice una pérdida inminente de energía, lo que permite que la computadora se apague ordenadamente mientras aún queda suficiente energía para hacerlo. Las interrupciones del teclado generalmente hacen que las pulsaciones de teclas se almacenen en búfer para implementar la escritura anticipada.

Las interrupciones a veces se utilizan para emular instrucciones que no están implementadas en algunos equipos de una familia de productos. Por ejemplo, las instrucciones de punto flotante pueden implementarse en hardware en algunos sistemas y emularse en sistemas de menor costo. En el último caso, la ejecución de una instrucción de coma flotante no implementada provocará una "instrucción ilegal" interrupción de excepción. El controlador de interrupciones implementará la función de punto flotante en el software y luego regresará al programa interrumpido como si la instrucción implementada por hardware se hubiera ejecutado. Esto proporciona portabilidad del software de aplicación en toda la línea.

Las interrupciones son similares a las señales, con la diferencia de que las señales se utilizan para la comunicación entre procesos (IPC), mediadas por el núcleo (posiblemente a través de llamadas al sistema) y manejadas por procesos, mientras que las interrupciones son mediadas por el procesador y manejadas por el núcleo El núcleo puede pasar una interrupción como señal al proceso que la provocó (ejemplos típicos son SIGSEGV, SIGBUS, SIGILL y SIGFPE).

Historia

Las interrupciones de hardware se introdujeron como una optimización, eliminando el tiempo de espera improductivo en los bucles de sondeo, esperando eventos externos. El primer sistema que utilizó este enfoque fue el DYSEAC, completado en 1954, aunque los sistemas anteriores proporcionaban funciones de captura de errores.

A la computadora UNIVAC 1103A generalmente se le atribuye el primer uso de interrupciones en 1953. Anteriormente, en la UNIVAC I (1951), el desbordamiento aritmético activaba la ejecución de una rutina de reparación de dos instrucciones en la dirección 0 o, a elección del programador, hizo que la computadora se detuviera." El IBM 650 (1954) incorporó la primera aparición de enmascaramiento de interrupciones. La Oficina Nacional de Normas DYSEAC (1954) fue la primera en utilizar interrupciones para E/S. El IBM 704 fue el primero en utilizar interrupciones para la depuración, con una 'trampa de transferencia', que podía invocar una rutina especial cuando se encontraba una instrucción de bifurcación. El sistema TX-2 del Laboratorio Lincoln del MIT (1957) fue el primero en proporcionar múltiples niveles de interrupciones de prioridad.

Contenido relacionado

Juan Ericsson

Reconocimiento óptico de caracteres

Peso