Intel 8085

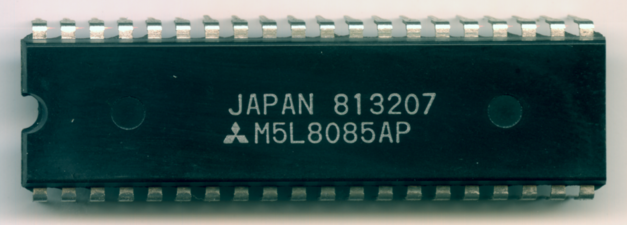

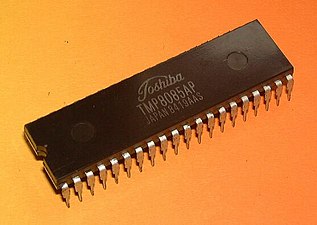

El Intel 8085 ("ochenta-ochenta-cinco") es un microprocesador de 8 bits producido por Intel y presentado en marzo de 1976. Es compatible en software binario con el más famoso Intel 8080 con solo dos instrucciones menores agregadas para admitir sus funciones adicionales de interrupción y entrada/salida en serie. Sin embargo, requiere menos circuitos de soporte, lo que permite construir sistemas de microcomputadoras más simples y menos costosos. El "5" en el número de pieza destacó el hecho de que el 8085 usa una sola fuente de alimentación de +5 voltios (V) mediante el uso de transistores de modo de agotamiento, en lugar de requerir los suministros de +5 V, −5 V y +12 V que necesita el 8080. Esta capacidad coincidía con la del Z80 de la competencia, un popular CPU derivado del 8080 presentado el año anterior. Estos procesadores podrían usarse en computadoras que ejecutan el sistema operativo CP/M.

El 8085 se suministra en un paquete DIP de 40 pines. Para maximizar las funciones en los pines disponibles, el 8085 utiliza un bus de dirección/datos multiplexados (AD0-AD7). Sin embargo, un circuito 8085 requiere un latch de dirección de 8 bits, por lo que Intel fabricó varios chips de soporte con un latch de dirección incorporado. Estos incluyen el 8755, con un latch de dirección, 2 KB de EPROM y 16 pines de E/S, y el 8155 con 256 bytes de RAM, 22 pines de E/S y un temporizador/contador programable de 14 bits. El bus de direcciones/datos multiplexado redujo el número de pistas de PCB entre el 8085 y dichos chips de memoria y E/S.

Tanto el 8080 como el 8085 fueron eclipsados por el Zilog Z80 para computadoras de escritorio, que se hizo cargo de la mayor parte del mercado de computadoras CP/M, así como una parte del floreciente mercado de computadoras domésticas a principios y mediados de -1980.

El 8085 tuvo una larga vida como controlador, sin duda gracias a su E/S serial integrada y cinco interrupciones priorizadas, posiblemente características similares a las de un microcontrolador que la CPU Z80 no tenía. Una vez diseñado en productos como el controlador DECtape II y el terminal de video VT102 a fines de la década de 1970, el 8085 sirvió para nuevas producciones durante la vida útil de esos productos. Por lo general, esto era más largo que la vida útil del producto de las computadoras de escritorio.

Descripción

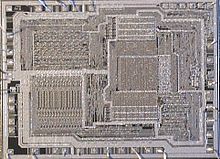

El 8085 es un diseño convencional de von Neumann basado en el Intel 8080. A diferencia del 8080, no multiplexa señales de estado en el bus de datos, sino que el bus de datos de 8 bits se multiplexa con los ocho bits inferiores del bus de 16 bits. bus de dirección de bits para limitar el número de pines a 40. Las señales de estado son proporcionadas por pines de señal de control de bus dedicados y dos pines de ID de estado de bus dedicados llamados S0 y S1. El pin 40 se usa para la fuente de alimentación (+5 V) y el pin 20 para tierra. El pin 39 se utiliza como pin de retención. El procesador fue diseñado usando circuitos nMOS, y el posterior "H" Las versiones se implementaron en el proceso nMOS mejorado de Intel llamado HMOS II ('MOS de alto rendimiento'), desarrollado originalmente para productos de RAM estática rápida. Solo se necesita una fuente de alimentación de 5 voltios, como los procesadores de la competencia ya diferencia del 8080. El 8085 utiliza aproximadamente 6500 transistores.

El 8085 incorpora las funciones del 8224 (generador de reloj) y el 8228 (controlador del sistema) en chip, aumentando el nivel de integración. Una desventaja en comparación con diseños contemporáneos similares (como el Z80) es el hecho de que los buses requieren demultiplexación; sin embargo, los pestillos de dirección en los chips de memoria Intel 8155, 8355 y 8755 permiten una interfaz directa, por lo que un 8085 junto con estos chips es casi un sistema completo.

El 8085 tiene extensiones para admitir nuevas interrupciones, con tres interrupciones vectoriales enmascarables (RST 7.5, RST 6.5 y RST 5.5), una interrupción no enmascarable (TRAP) y una interrupción con servicio externo (INTR). Cada una de estas cinco interrupciones tiene un pin separado en el procesador, una característica que permite que los sistemas simples eviten el costo de un controlador de interrupción separado. La interrupción RST 7.5 se activa por borde (bloqueada), mientras que RST 5.5 y 6.5 son sensibles al nivel. Todas las interrupciones son habilitadas por la instrucción EI y deshabilitadas por la instrucción DI. Además, las instrucciones SIM (Establecer máscara de interrupción) y RIM (Leer máscara de interrupción), las únicas instrucciones del 8085 que no son del diseño del 8080, permiten enmascarar individualmente cada una de las tres interrupciones RST enmascarables. Los tres están enmascarados después de un reinicio normal de la CPU. SIM y RIM también permiten leer el estado de máscara de interrupción global y los tres estados de máscara de interrupción RST independientes, leer los estados de interrupción pendiente de esas mismas tres interrupciones, restablecer el flip-flop de pestillo de activación RST 7.5 (cancelando la interrupción pendiente sin repararla), y los datos en serie se enviarán y recibirán a través de los pines SOD y SID, respectivamente, todo bajo el control del programa e independientemente entre sí.

SIM y RIM se ejecutan cada uno en cuatro ciclos de reloj (estados T), lo que permite muestrear SID y/o alternar SOD considerablemente más rápido de lo que es posible alternar o muestrear una señal a través de cualquier E/S o puerto asignado a la memoria, p.ej. uno de los puertos de un 8155. (De esta manera, SID se puede comparar con el pin SO ["Set Overflow"] de la CPU 6502 contemporánea al 8085).

Al igual que el 8080, el 8085 puede acomodar memorias más lentas a través de estados de espera generados externamente (pin 35, READY) y tiene provisiones para acceso directo a memoria (DMA) usando señales HOLD y HLDA (pines 39 y 38). Una mejora con respecto al 8080 es que el 8085 puede controlar un cristal piezoeléctrico conectado directamente a él, y un generador de reloj integrado genera señales de reloj de dos fases de gran amplitud interna a la mitad de la frecuencia del cristal (un cristal de 6,14 MHz produciría un reloj de 3,07 MHz, por ejemplo). El reloj interno está disponible en un pin de salida, para controlar dispositivos periféricos u otras CPU en sincronía de bloqueo con la CPU desde la que se emite la señal. El 8085 también puede sincronizarse con un oscilador externo (lo que hace factible usar el 8085 en sistemas multiprocesador síncronos que usan un reloj común para todo el sistema para todas las CPU, o para sincronizar la CPU con una referencia de tiempo externa, como la de un fuente de video o una referencia de tiempo de alta precisión).

El 8085 es un seguimiento binario compatible del 8080. Admite el conjunto de instrucciones completo del 8080, con exactamente el mismo comportamiento de instrucción, incluidos todos los efectos en los indicadores de la CPU (excepto la operación AND/ANI, que establece la bandera AC de manera diferente). Esto significa que la gran mayoría del código objeto (cualquier imagen de programa en ROM o RAM) que se ejecuta con éxito en el 8080 puede ejecutarse directamente en el 8085 sin traducción ni modificación. (Las excepciones incluyen el código de tiempo crítico y el código que es sensible a la diferencia antes mencionada en la configuración del indicador AC o a las diferencias en el comportamiento de la CPU no documentado). el MOV r,r' instrucción, son un ciclo de reloj más rápido, pero las instrucciones que implican operaciones de 16 bits, incluidas las operaciones de pila (que aumentan o disminuyen el registro SP de 16 bits) generalmente un ciclo más lento. Por supuesto, es posible que el 8080 y/o el 8085 real difieran de las especificaciones publicadas, especialmente en detalles sutiles. (No ocurre lo mismo con el Z80). Como ya se mencionó, solo las instrucciones SIM y RIM eran nuevas para el 8085.

Modelo de programación

El procesador tiene siete registros de 8 bits accesibles para el programador, llamados A, B, C, D, E, H y L, donde A también se conoce como el acumulador. Los otros seis registros se pueden usar como registros de bytes independientes o como tres pares de registros de 16 bits, BC, DE y HL (o B, D, H, como se menciona en los documentos de Intel), según la instrucción particular. Algunas instrucciones usan HL como un acumulador (limitado) de 16 bits. Al igual que en el 8080, se puede acceder al contenido de la dirección de memoria apuntada por HL como un pseudo registro M. También tiene un contador de programa de 16 bits y un puntero de memoria de pila de 16 bits (reemplazando el 8008's interno). pila). Instrucciones como PUSH PSW, POP PSW afectan la palabra de estado del programa (acumulador y banderas). El acumulador almacena los resultados de las operaciones aritméticas y lógicas, y los bits de registro de las banderas (señal, cero, acarreo auxiliar, paridad y banderas de acarreo) se establecen o borran de acuerdo con los resultados de estas operaciones. El indicador de signo se establece si el resultado tiene un signo negativo (es decir, se establece si se establece el bit 7 del acumulador). La bandera auxiliar o de medio acarreo se establece si se produce un traspaso del bit 3 al bit 4. El indicador de paridad se establece en 1 si la paridad (número de 1 bits) del acumulador es par; si es impar, se borra. El indicador cero se establece si el resultado de la operación fue 0. Por último, el indicador de acarreo se establece si se produjo un remanente del bit 7 del acumulador (el MSB).

Comandos/instrucciones

Como en muchos otros procesadores de 8 bits, todas las instrucciones están codificadas en un solo byte (incluidos los números de registro, pero excluyendo los datos inmediatos), por simplicidad. Algunos de ellos van seguidos de uno o dos bytes de datos, que pueden ser un operando inmediato, una dirección de memoria o un número de puerto. Un NOP "sin operación" existe la instrucción, pero no modifica ninguno de los registros o banderas. Al igual que los procesadores más grandes, tiene instrucciones CALL y RET para llamadas y devoluciones de procedimientos de varios niveles (que se pueden ejecutar condicionalmente, como saltos) e instrucciones para guardar y restaurar cualquier par de registros de 16 bits en la pila de la máquina. También hay ocho instrucciones de llamada de un byte (RST) para subrutinas ubicadas en las direcciones fijas 00h, 08h, 10h,...,38h. Estos están destinados a ser suministrados por hardware externo para invocar una rutina de servicio de interrupción correspondiente, pero también se emplean a menudo como llamadas rápidas al sistema. Una instrucción sofisticada es XTHL, que se utiliza para intercambiar el par de registros HL con el valor almacenado en la dirección indicada por el puntero de la pila.

Instrucciones de 8 bits

Todas las operaciones aritméticas y lógicas (ALU) de 8 bits y dos operandos funcionan en el acumulador de 8 bits (el registro A). Para operaciones de dos operandos de 8 bits, el otro operando puede ser un valor inmediato, otro registro de 8 bits o una celda de memoria direccionada por el par de registros de 16 bits HL. Las únicas operaciones ALU de 8 bits que pueden tener un destino diferente al acumulador son las instrucciones de incremento o decremento unario, que pueden operar en cualquier registro de 8 bits o en la memoria direccionada por HL, como para operaciones de 8 bits de dos operandos. Se admite la copia directa entre dos registros cualesquiera de 8 bits y entre cualquier registro de 8 bits y una celda de memoria con dirección HL, utilizando la instrucción MOV. También se puede mover un valor inmediato a cualquiera de los destinos anteriores, usando la instrucción MVI. Debido a la codificación regular de la instrucción MOV (utilizando casi una cuarta parte del espacio total del código de operación), existen códigos redundantes para copiar un registro en sí mismo (MOV B,B, por ejemplo), que son de poco uso, salvo retrasos. Sin embargo, lo que habría sido una copia de la celda direccionada por HL en sí misma (es decir, MOV M,M) codifica la instrucción HLT, deteniendo la ejecución hasta que se produzca un reinicio externo o una interrupción desenmascarada.

Operaciones de 16 bits

Aunque el 8085 es un procesador de 8 bits, tiene algunas operaciones de 16 bits. Cualquiera de los tres pares de registros de 16 bits (BC, DE, HL o SP) se puede cargar con un valor inmediato de 16 bits (usando LXI), incrementado o decrementado (usando INX y DCX) o agregado a HL (usando DAD). LHLD carga HL desde la memoria direccionada directamente y SHLD almacena HL de la misma manera. La operación XCHG intercambia los valores de HL y DE. Agregar HL a sí mismo realiza un desplazamiento aritmético a la izquierda de 16 bits con una instrucción. La única instrucción de 16 bits que afecta cualquier indicador es DAD (que agrega BC, DE, HL o SP a HL), que actualiza el indicador de acarreo para facilitar adiciones de 24 bits o más y desplazamientos a la izquierda. Agregar el puntero de pila a HL es útil para indexar variables en marcos de pila (recursivos). Se puede asignar un marco de pila usando DAD SP y SPHL, y se puede hacer una bifurcación a un puntero calculado con PCHL. Estas capacidades hacen factible compilar lenguajes como PL/M, Pascal o C con variables de 16 bits y producir código de máquina 8085. Las operaciones lógicas de resta y bit a bit en 16 bits se realizan en pasos de 8 bits. Las operaciones que deben implementarse mediante código de programa (bibliotecas de subrutinas) incluyen comparaciones de enteros con signo, así como multiplicaciones y divisiones.

Instrucciones no documentadas

Dos ingenieros de software, Wolfgang Dehnhardt y Villy M. Sorensen, descubrieron varias instrucciones y banderas no documentadas en el proceso de desarrollo de un ensamblador 8085. Estas instrucciones utilizan operandos de 16 bits e incluyen operaciones de carga y almacenamiento indirectos de una palabra, una resta, un desplazamiento, una rotación y una compensación.

Esquema de entrada/salida

El 8085 es compatible con E/S tanto con asignación de puerto como con asignación de memoria. Admite hasta 256 puertos de entrada/salida (E/S) a través de instrucciones de entrada/salida dedicadas, con direcciones de puerto como operandos. La E/S mapeada en puertos puede ser una ventaja en procesadores con espacio de direcciones limitado. Durante un ciclo de bus de E/S con asignación de puertos, la CPU emite la dirección de E/S de 8 bits en las mitades inferior y superior del bus de direcciones de 16 bits.

También se puede acceder a los dispositivos diseñados para E/S mapeada en memoria usando las instrucciones LDA (cargar acumulador desde una dirección de 16 bits) y STA (almacenar acumulador en una dirección de 16 bits especificada), o cualquier otra instrucción que tenga operandos de memoria. Un ciclo de transferencia de E/S asignado a la memoria aparece en el bus como un ciclo normal de acceso a la memoria.

Sistema de desarrollo

Intel produjo una serie de sistemas de desarrollo para el 8080 y el 8085, conocidos como el sistema de microprocesador MDS-80. El sistema de desarrollo original tenía un procesador 8080. Más tarde se agregó compatibilidad con 8085 y 8086, incluido ICE (emuladores en circuito). Es una caja de sobremesa grande y pesada, de unos 20" cubo (en el color azul corporativo de Intel) que incluye una CPU, un monitor y una sola unidad de disquete de 8 pulgadas. Posteriormente, se puso a disposición una caja externa con dos unidades de disquete más. Ejecuta el sistema operativo ISIS y también puede operar un emulador y un programador EPROM externo. Esta unidad utiliza la jaula de tarjetas Multibus que fue diseñada solo para el sistema de desarrollo. Se vendía una cantidad sorprendente de soportes para tarjetas y procesadores de repuesto, lo que llevó al desarrollo del Multibus como un producto separado.

El último iPDS es una unidad portátil, de aproximadamente 8" × 16" × 20", con mango. Tiene una pequeña pantalla verde, un teclado incorporado en la parte superior, una unidad de disquete de 5¼ pulgadas y ejecuta el sistema operativo ISIS-II. También puede aceptar un segundo procesador 8085, lo que permite una forma limitada de operación multiprocesador donde ambos procesadores se ejecutan de forma simultánea e independiente. La pantalla y el teclado se pueden cambiar entre ellos, lo que permite ensamblar programas en un procesador (los programas grandes tomaron un tiempo) mientras se editan los archivos en el otro. Tiene una opción de memoria de burbuja y varios módulos de programación, incluidos EPROM, y módulos de programación Intel 8048 y 8051 que se conectan al costado, reemplazando a los programadores de dispositivos independientes. Además de un ensamblador 8080/8085, Intel produjo una serie de compiladores, incluidos los de PL/M-80 y Pascal, y un conjunto de herramientas para vincular y ubicar estáticamente programas para permitir que se graben en EPROM y se utilicen en sistemas integrados..

Un "Kit de diseño del sistema MCS-85" de menor costo (SDK-85) contiene una CPU 8085, una ROM 8355 que contiene un programa de monitoreo de depuración, una RAM 8155 y 22 puertos de E/S, un teclado hexadecimal 8279 y un LED de 7 segmentos de 8 dígitos y un TTY (teletipo) 20 mA interfaz serial de bucle de corriente. Los pads están disponibles para una EPROM 8755 2K×8 más y otra 256 byte RAM 8155 I/O El temporizador/contador se puede agregar opcionalmente. Todas las señales de datos, control y dirección están disponibles en cabezales de doble pin y se proporciona una gran área de creación de prototipos.

Lista de Intel 8085

| Número de modelo | Proceso de tecnología | Nodo de proceso | Reloj de velocidad | Rango de temperatura | Calificación actual | Power Tolerance | Paquete | Fecha de lanzamiento | Precio USD |

|---|---|---|---|---|---|---|---|---|---|

| 8085A | NMOS | 3 micrones | 3 MHz | 170 mA | ± 5% | $6,25 | |||

| P8085AH | HMOS II | 2 micrones | 3 MHz | 135 mA | ± 10% | Plástico | Julio/agosto de 1981 | $4.40 | |

| 8085-2 | 5 MHz | ||||||||

| 8085A-2 | NMOS | 3 micrones | 5 MHz | 170 mA | ± 5% | $8.75 | |||

| P8085AH-2 | HMOS II | 2 micrones | 5 MHz | 135 mA | ± 10% | Plástico | Julio/agosto de 1981 | $5.80 | |

| P8085AH-1 | HMOS II | 2 micrones | 6 MHz | Plástico | Julio/agosto de 1981 | $12.45 | |||

| ID8085 | 3 MHz | Industrial | Marzo/abril de 1979 | 38,75 dólares | |||||

| M8085A | 3 MHz | Militar | Marzo/abril de 1979 | $110.00 |

- ^ En cantidades de 100 y hasta

Aplicaciones

El procesador 8085 se usó en algunas de las primeras computadoras personales, por ejemplo, la línea TRS-80 Modelo 100 usó un 80C85 (MSM80C85ARS) fabricado por OKI. La versión CMOS 80C85 del procesador NMOS/HMOS 8085 tiene varios fabricantes. En la Unión Soviética, se desarrolló un clon 80C85 con la designación IM1821VM85A (en ruso: ИМ1821ВМ85А) que en 2016 todavía estaba en producción. Algunos fabricantes ofrecen variantes con funciones adicionales, como instrucciones adicionales.

La versión resistente a la radiación del 8085 ha estado en procesadores de datos de instrumentos a bordo para varias misiones de física espacial de la NASA y la ESA en la década de 1990 y principios de la de 2000, incluidas CRRES, Polar, FAST, Cluster, HESSI, Sojourner Mars Rover, y TEMIS. La empresa suiza SAIA utilizó el 8085 y el 8085-2 como CPU de su línea PCA1 de controladores lógicos programables durante la década de 1980.

Pro-Log Corp. colocó el 8085 y el hardware de soporte en una tarjeta de formato de bus STD que contiene CPU, RAM, zócalos para ROM/EPROM, E/S e interfaces de bus externas. La tarjeta de referencia del conjunto de instrucciones incluida utiliza mnemónicos completamente diferentes para la CPU Intel 8085. El producto era un competidor directo de las ofertas de tarjetas Multibus de Intel.

- Fuentes Intel 8085

Familia MCS-85

La CPU 8085 es parte de una familia de chips desarrollados por Intel para construir un sistema completo. Muchos de estos chips de soporte también se usaron con otros procesadores. La PC IBM original basada en el procesador Intel 8088 usaba varios de estos chips; las funciones equivalentes en la actualidad las proporcionan los chips VLSI, a saber, el "Southbridge" papas fritas.

- 8085 – CPU

- 8231 – Aritmética Dependencia de Procesamiento

- 8232 – Procesador de pintura flotante

- 8205 – 1 of 8 Binary Decoder

RAM estática

- 8155 – 2K-bit MOS RAM estática con 3 puertos I/O y temporizador. La versión industrial del ID8155 estaba disponible para 37,50 dólares en cantidades de 100 y arriba. La versión militar de M8155 estaba disponible para US$100,00 en cantidades de 100. Hay un 5 MHz versión de Intel 8155-2. El 8155H disponible se introdujo utilizando la tecnología HMOS II que utiliza un 30 por ciento menos potencia que la generación anterior. La versión del paquete de plástico de P8155H (3 MHz) y P8155H-2 (5 MHz) están disponibles para 5,15 dólares y 6,40 dólares por 100 en cantidades respetuosamente.

- 8156 – 2K-bit MOS RAM estática con 3 puertos I/O y temporizador. La versión industrial del ID8156 estaba disponible para 37,50 dólares en cantidades de 100. Hay un 5 MHz versión de Intel 8156-2. El 8156H disponible se introdujo utilizando la tecnología HMOS II que utiliza 30 por ciento menos potencia que la generación anterior. La versión del paquete de plástico de P8156H (3 MHz) y P8156H-2 (5 MHz) están disponibles para 5,15 dólares y 6,40 dólares por 100 en cantidades respetuosamente.

- 8185 – 1.024 x 8-bit RAM estática. El 5 MHz versión de Intel 8185-2 estaba disponible para 48,75 dólares en cantidad de 100.

Memoria ROM

- 8355 – 2.048 × 8 bits ROM, dos puertos I/O de 8 bits. La versión industrial del ID8355 estaba disponible para US$22.00 en cantidades de 1000. Hay un 5 MHz versión de Intel 8355-2.

- 8604 – 4096-bit (512 × 8) PROM

- 8755 – 2048 x 8 bit EPROM, dos puertos I/O de 8 bits. El Intel 8755A-2 es el 5 MHz versión. Esa versión estaba disponible para US$81.00 en cantidad de 100. Había una versión de Grado Industrial Intel I8755A-8.

Controladores de RAM

- 8202 – Controlador de RAM dinámico. Esto admite los módulos Intel 2104A, 2117 o 2118 DRAM, hasta 128 KB de módulos DRAM. El precio se redujo a 36,25 dólares para cantidades de 100 para el estilo de paquete D8202 alrededor de mayo de 1979.

- 8203 – Controlador de RAM dinámico. La versión Intel 82C03 CMOS disipa menos de 25 mA. Admite hasta 16x 64K-bit RAM para una capacidad total de hasta 256 KB. Refresca cada 10 a 16 microsegundos. Soporta multiplexación de direcciones de memoria fila y columna. Genera estrobos para coger la dirección interna. Arregla entre solicitudes simultáneas de acceso a la memoria y refresco. También reconoce ciclos de acceso a la memoria al sistema CPU. El 82C03 estaba disponible en paquetes de cerámica o plástico para 32.00 dólares en 100 piezas de cantidad.

- 8207 – DRAM Controlador

Periferia

- 8206 – Detección de errores " Corrección Dependencia

- 8210 – TTL A MOS Shifter & Controlador de reloj de alta tensión

- 8212 – 8 bits I/O Puerto. La versión industrial del ID8212 estaba disponible para 6,75 dólares en cantidades de 100.

- 8216 – 4 bits Parallel Bidirectional Bus Driver. La versión industrial del ID8216 estaba disponible para 6,40 dólares en cantidades de 100.

- 8218/8219 – Controlador de autobuses

- 8226 – 4 bits Parallel Bidirectional Bus Driver. La versión industrial del ID8226 estaba disponible para 6,40 dólares en cantidades de 100.

- 8237 – DMA Controlador

- 8251 – USART Communication Controller

- 8253 – Programable Interval Timer

- 8254 – Programable Interval Timer. La versión 82C54 CMOS fue subcontratada a Oki Electronic Industry Co., Ltd.

- 8255 – Programable Interfaz periférica

- 8256 – Multifunción periférica. Este chip multifunción utiliza Comunicaciones serie, Paralelo I/O, Contratiempos e Interrupciones. El Intel 8256AH estaba disponible para US$21.40 en cantidades de 100. Este chip de circuito integrado integra los chips con la siguiente funcionalidad:

- Intel 8251A Interfaz de comunicaciones programables

- Intel 8253 Programable Interval Timer

- Intel 8255A Interfaz periférica programable

- Intel 8259A Controlador Interrupt programable.

- 8257 – DMA Controlador

- 8259 – Programable Interrupt Controller

- 8271 – Programable Controlador de discos de Floppy

- 8272 – Controlador de Discos de Densidad Individual/Doble. Es compatible con los formatos IBM 3740 y System 34 y proporciona tanto Modulación de frecuencias (FM) como Modificación de frecuencias modificadas (MFM). Esta versión estaba disponible para 38,10 dólares en cantidades de 100.

- 8273 – Controlador de protocolo HDLC/SDLC programable. Este dispositivo admite los protocolos de comunicación SDLC de ISO/CCITT y IBM. Éstos estaban disponibles para 33,75 dólares ()4 MHz) y US$30.00 ()8 MHz) en cantidades de 100.

- 8274 – Multi-Protocolo Controlador de serie. Esta compatibilidad con tres protocolos diferentes utilizando la siguiente característica de Operación Asincrónica, Operación Sincrónica Byte y Operación Sincrónica Bit. El modo Byte Synchronous es compatible con el protocolo de señal Bisync de IBM. El modo Bit Synchronous es compatible con el SDLC de IBM y el protocolo HDLC de la Organización Internacional de Normas y es compatible con el estándar internacional CCITT X.25. Fue empaquetado en un producto de 40 pines usando la tecnología HMOS de Intel. La versión disponible es de hasta 880 kilobaud por 30,30 dólares en las cantidades de 100. NEC μPD7201 también era compatible.

- 8275 – Controlador de CRT programable. Refresca la pantalla del escaneo de la raster con amortiguación desde la memoria principal y manteniendo la pista de la parte de la pantalla. Esta versión estaba disponible para 32.00 dólares en cantidades de 100.

- 8276 – Controlador de CRT pequeño sistema

- 8278 – Programable Interfaz de la junta clave

- 8279 – Key Board/Display Controller

- 8282 – 8-bit Extracción con amortiguación de salida

- 8283 – 8 bits Inverting Latch with Output Buffer

- 8291 – GPIB Talker/Listener. Este controlador puede funcionar de 1 a 1 8 MHz. Estaba disponible para 23,75 dólares en cantidades de 100.

- 8292 – Controlador GPIB. Diseñado alrededor de Intel 8041A que ha sido programado como elemento de interfaz de controlador. También controla el autobús usando tres temporizadores para detectar problemas en la interfaz de bus GPIB. Estaba disponible para US$21.25 en cantidades de 100.

- 8293 – Transceptor GPIB. Este chipset admite hasta 4 modos diferentes: Modo 0 Líneas de Control de Talker/Listener, Modo 1 Líneas de Control de Talker/Listener/Controller, Modo 2 Talker/Listener/Controller Líneas de datos, y Modo 3 Líneas de datos Talker/Listener. Estaba disponible para US$11.50 en cantidades de 100. En el momento de la liberación, estaba disponible en muestras y luego la producción completa en el primer trimestre de 1980.

- 8294 – Unidad de cifrado/descifrado de datos + 1 O/P Puerto. Encripta y descifra bloques de 64 bits de datos usando el algoritmo estándar de procesamiento de información federal. Esto también utiliza el algoritmo de cifrado de la Oficina Nacional de Normas. Este DEU opera usando una clave especificada por el usuario de 56 bits para generar palabras de cifrado de 64 bits. Estaba disponible para 22,50 dólares en cantidades de 100.

- 8295 – Controlador de impresoras Dot Matrix. Esta interfaz con impresoras de matriz de puntos LRC 7040 Series y otras impresoras pequeñas también. Estaba disponible para 20,65 dólares en cantidades de 100.

Uso educativo

En muchas escuelas de ingeniería, el procesador 8085 se usa en cursos de introducción a los microprocesadores. Varias empresas ofrecen kits de formación compuestos por una placa de circuito impreso, 8085, y hardware de soporte. Estos kits suelen incluir documentación completa que permite a un estudiante pasar de la soldadura a la programación en lenguaje ensamblador en un solo curso. Además, la arquitectura y el conjunto de instrucciones del 8085 son fáciles de entender para un estudiante. Las versiones de proyectos compartidos de computadoras de placa única basadas en 8085 educativas y de pasatiempo se indican a continuación en la sección Enlaces externos de este artículo.

Simuladores

Los simuladores de software están disponibles para el microprocesador 8085, que permiten la ejecución simulada de códigos de operación en un entorno gráfico.

Contenido relacionado

Gramática libre de contexto

Turbo pascal

Microfluidos