Intel 8051

El Intel MCS-51 (comúnmente denominado 8051) es una serie de microcontroladores de un solo chip (MCU) desarrollada por Intel en 1980 para su uso en sistemas integrados. El arquitecto del conjunto de instrucciones Intel MCS-51 fue John H. Wharton. Las versiones originales de Intel fueron populares en la década de 1980 y principios de la de 1990, y los derivados compatibles binarios mejorados siguen siendo populares en la actualidad. Es un ejemplo de una computadora con conjunto de instrucciones complejo (pero que también posee algunas de las características de las arquitecturas RISC, como un gran conjunto de registros y ventanas de registro) y tiene espacios de memoria separados para instrucciones y datos del programa.

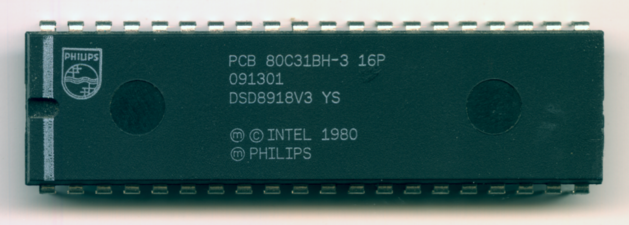

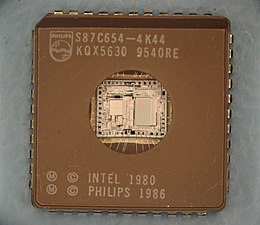

La familia MCS-51 original de Intel se desarrolló utilizando tecnología de semiconductores de óxido de metal (NMOS) de tipo N, como su predecesor Intel MCS-48, pero las versiones posteriores se identifican con una letra C en su nombre (por ejemplo, 80C51) utilizan tecnología complementaria de metal-óxido-semiconductor (CMOS) y consumen menos energía que sus predecesores NMOS. Esto los hizo más adecuados para dispositivos alimentados por batería.

La familia continuó en 1996 con el MCS-151 mejorado de 8 bits y el MCS-251 de 8/16 bits/32 bits de la familia de microcontroladores compatibles binarios. Si bien Intel ya no fabrica las familias MCS-51, MCS-151 y MCS-251, los derivados compatibles binarios mejorados fabricados por numerosos proveedores siguen siendo populares en la actualidad. Algunos derivados integran un procesador de señal digital (DSP) o una unidad de coma flotante (coprocesador, FPU). Más allá de estos dispositivos físicos, varias empresas también ofrecen derivados de MCS-51 como núcleos IP para su uso en arreglos de compuertas programables en campo (FPGA) o diseños de circuitos integrados específicos de aplicaciones (ASIC).

Características y aplicaciones importantes

La arquitectura 8051 proporciona muchas funciones (unidad central de procesamiento (CPU), memoria de acceso aleatorio (RAM), memoria de solo lectura (ROM), puertos de entrada/salida (E/S), puerto serie, control de interrupciones, temporizadores)) en un paquete:

- Unidad de lógica aritmética de 8 bits (ALU) y acumulador, registros de 8 bits (un registro de 16 bits con instrucciones especiales de movimiento), bus de datos de 8 bits y autobuses de dirección 2×16-bit, contador de programas, puntero de datos y operaciones de 8/11/16-bit relacionadas; por lo tanto, es principalmente un microcontrolador de 8 bits

- Procesador booleano con 17 instrucciones, acumulador de 1 bit, 32 registros (4x8-bit, poco aconsejable) y hasta 144 variables especiales 1 bit-addressable RAM (18x8-bit)

- Multiply, dividir y comparar instrucciones

- Cuatro bancos de registro rápidos conmutables con ocho registros cada uno (memoria mapeado)

- Interrupción rápida con conmutación de banco de registro opcional

- Interrupciones e hilos con prioridad seleccionable

- 128 o 256 bytes de RAM on-chip (IRAM)

- Autobús de dirección de 16 bits doble; puede acceder a 2×216 ubicaciones de memoria: 64 KB (65.536 ubicaciones) cada una de ROM (PMEM) y RAM externa (XRAM), utilizando dos autobuses de memoria en una arquitectura de Harvard.

- ROM en chip (no incluido en las variantes 803x)

- Cuatro (tres puertos completos) puertos bidireccionales de entrada / salida de 8 bits, poco accesible

- UART (puerto serie)

- Dos anticonceptivos de 16 bits

- Modo de ahorro de energía (en algunos derivados)

Una característica del núcleo 8051 es la inclusión de un motor de procesamiento booleano, que permite que las operaciones lógicas booleanas a nivel de bits se lleven a cabo de manera directa y eficiente en registros internos seleccionados, puertos y ubicaciones de RAM seleccionadas. Otra característica es la inclusión de cuatro conjuntos de registros de trabajo seleccionables por banco, que reducen en gran medida el tiempo necesario para realizar los cambios de contexto para entrar y salir de las rutinas de servicio de interrupción. Con una sola instrucción, el 8051 puede cambiar de banco de registros, lo que evita la tediosa tarea de transferir los registros críticos a la RAM.

Una vez que se ha configurado un UART, y un temporizador si es necesario, el programador solo necesita escribir una rutina de interrupción simple para rellenar el registro de desplazamiento enviar cada vez que el UART desplaza el último bit y /o vaciar el registro de desplazamiento recibir completo (copiar los datos en otro lugar). Luego, el programa principal realiza lecturas y escrituras en serie simplemente leyendo y escribiendo datos de 8 bits en pilas.

Características derivadas

A partir de 2013, muchos de los principales fabricantes de chips siguen desarrollando nuevos derivados, y los principales proveedores de compiladores, como IAR Systems, Keil y Altium Tasking, lanzan actualizaciones continuamente.

Los microcontroladores basados en MCS-51 suelen incluir uno o dos UART, dos o tres temporizadores, 128 o 256 bytes de RAM de datos interna (16 bytes de los cuales son direccionables por bits), hasta 128 bytes de E/S, 512 bytes a 64 KB de memoria de programa interna y, a veces, una cantidad de RAM de datos extendida (ERAM) ubicada en el espacio de datos externo. La RAM y la ROM externas comparten los buses de datos y direcciones. El núcleo 8051 original funcionaba a 12 ciclos de reloj por ciclo de máquina, y la mayoría de las instrucciones se ejecutaban en uno o dos ciclos de máquina. Con una frecuencia de reloj de 12 MHz, el 8051 podría ejecutar 1 millón de instrucciones de un ciclo por segundo o 500 000 instrucciones de dos ciclos por segundo. Los núcleos 8051 mejorados ahora se usan comúnmente y funcionan a seis, cuatro, dos o incluso un reloj por ciclo de máquina (denominado "1T") y tienen frecuencias de reloj de hasta 100 MHz y, por lo tanto, son capaces de un número aún mayor de instrucciones por segundo. Todos los dispositivos de Silicon Labs, algunos Dallas (ahora parte de Maxim Integrated) y algunos Atmel (ahora parte de Microchip) tienen núcleos de un solo ciclo.

Las variantes 8051 pueden incluir temporizadores de reinicio integrados con detección de caída de tensión, osciladores en el chip, memoria de programa ROM flash autoprogramable, RAM externa integrada, almacenamiento de programa interno adicional, código de cargador de arranque en ROM, EEPROM no almacenamiento de datos volátiles, interfaces host I2C, SPI y USB, bus CAN o LIN, módulos de radio ZigBee o Bluetooth, generadores PWM, comparadores analógicos, convertidores de analógico a digital y de digital a analógico, RTC, contadores y temporizadores adicionales, instalaciones de depuración en circuito, más fuentes de interrupción, modos de ahorro de energía adicionales, más/menos puertos paralelos, etc. Intel fabricó una versión programada en máscara, 8052AH-BASIC, con un intérprete BASIC en ROM, capaz de ejecutar programas de usuario cargados en RAM.

Los microcontroladores basados en MCS-51 se han adaptado a entornos extremos. Ejemplos de variantes de alta temperatura son la familia Tekmos TK8H51 para −40 °C a +250 °C o Honeywell HT83C51 para −55 °C a +225 °C (con funcionamiento hasta 1 año a +300 °C). Los microcontroladores MCS-51 resistentes a la radiación para su uso en naves espaciales están disponibles; por ejemplo, de Cobham (anteriormente Aeroflex) como UT69RH051 o de NIIET como 1830VE32 (en ruso: 1830ВЕ32).

En algunas escuelas de ingeniería, el microcontrolador 8051 se usa en cursos de introducción a microcontroladores.

Convenciones de nombres familiares

8051 es el nombre original de Intel con 4 KB de ROM y 128 bytes de RAM. Las variantes que comienzan con 87 tienen una EPROM programable por el usuario, a veces borrable por UV. Las variantes con una C como tercer carácter son algún tipo de CMOS. 8031 y 8032 son versiones sin ROM, con 128 y 256 bytes de RAM. El último dígito puede indicar el tamaño de la memoria, p. 8052 con 8 KB de ROM, 87C54 con 16 KB de EPROM y 87C58 con 32 KB de EPROM, todos con 256 bytes de RAM.

Arquitectura de la memoria

El MCS-51 tiene cuatro tipos distintos de memoria: RAM interna, registros de funciones especiales, memoria de programa y memoria de datos externa. Para acceder a estos de manera eficiente, algunos compiladores utilizan hasta 7 tipos de definiciones de memoria: RAM interna, acceso de un solo bit a la RAM interna, registros de funciones especiales, acceso de un solo bit a registros de funciones especiales seleccionados (divisible por 8), RAM de programa, RAM externa a la que se accede mediante un registro de acceso indirecto, mediante uno de los registros estándar de 8 bits, y registro de acceso indirecto a la RAM externa mediante el registro de acceso indirecto de 16 bits.

El conjunto de instrucciones del 8051 está diseñado como una arquitectura Harvard con memoria segregada (datos e instrucciones); solo puede ejecutar código extraído de la memoria del programa y no tiene instrucciones para escribir en la memoria del programa. Sin embargo, el bus que sale del IC tiene una sola dirección y ruta de datos, y se parece mucho a un bus de arquitectura Von Neumann.

La mayoría de los sistemas 8051 respetan el conjunto de instrucciones y requieren funciones personalizadas para descargar nuevos programas ejecutables, p. en la memoria flash.

RAM interna

La RAM interna (IRAM) tiene un espacio de direcciones de 8 bits y utiliza direcciones de 0 a 0xFF. IRAM de 0x00 a 0x7F contiene 128 registros de 1 byte directamente direccionables, a los que se puede acceder mediante una dirección absoluta de 8 bits que forma parte de la instrucción. Alternativamente, se puede acceder a IRAM indirectamente: la dirección se carga en R0 o R1, y se accede a la memoria usando la sintaxis @R0 o @R1, o como memoria de pila a través del puntero de pila SP, con las operaciones PUSH y POP; y operaciones *CALL y RET.

El 8051 original tiene solo 128 bytes de IRAM. El 8052 agregó IRAM de 0x80 a 0xFF, al que solo se puede acceder indirectamente (por ejemplo, para usar como espacio de pila). La mayoría de los clones 8051 también tienen 256 bytes completos de IRAM.

Los accesos directos a las direcciones IRAM 80-FF se asignan, en cambio, a los registros de funciones especiales (SFR), donde los acumuladores A, B llevan el bit C y otros registros especiales para control, estado, etc. situado.

Registros de funciones especiales

Los registros de funciones especiales (SFR) están ubicados en el mismo espacio de direcciones que IRAM, en las direcciones 0x80 a 0xFF, y se accede a ellos directamente usando las mismas instrucciones que para la mitad inferior de IRAM. No se puede acceder a ellos indirectamente a través de @R0 o @R1 o mediante el puntero de pila SP; el acceso indirecto a esas direcciones accederá a la segunda mitad de IRAM, en cambio.

Los registros de funciones especiales (SFR) incluyen los acumuladores A (o ACC, en E0) y B (en F0) y la palabra de estado del programa (o PSW, en D0), así como el puntero de datos de 16 bits DPTR (a los 82, como DPL y 83 como DPH). Además de estos, un pequeño núcleo de otros registros de funciones especiales, incluido el IE de habilitación de interrupción en A8 y la IP de prioridad de interrupción en B8; los puertos de E/S P0 (80), P1 (90), P2 (A0), P3 (B0); el control de E/S serie SCON (98) y el búfer SBUF (99); el registro de control de potencia/CPU PCON (87); y los registros para el control de los temporizadores 0 y 1 (TCON en 88) y el modo de operación (TMOD en 89), el temporizador 0 de 16 bits (TL0 en 8A, TH0 en 8C) y el temporizador 1 (TL1 en 8B, TH1 en 8D) - están presentes en todas las versiones del 8051. Otras direcciones dependen de la versión; en particular, los registros del temporizador 2 para el 8052: el registro de control T2CON (en C8), la captura/latch de 16 bits (RCAP2L en CA, RCAP2H en CB) y el temporizador 2 (TL2 en CC y TH2 en CD), son no incluido con el 8051.

Registrar ventanas

Los 32 bytes en IRAM de 0x00–0x1F contienen espacio para cuatro ventanas de registro de ocho bytes, a las que se asignan los 8 registros R0–R7. La ventana actualmente activa está determinada por una dirección de dos bits contenida en la palabra de estado del programa.

Registros de bits

Los 16 bytes (128 bits) en las ubicaciones IRAM 0x20–0x2F contienen espacio para 128 registros de 1 bit, que se pueden direccionar por separado como registros de bits 00-7F.

Los registros de bits restantes, direccionados como 80-FF, se asignan a los 16 registros de funciones especiales 80, 88, 90, 98,..., F0 y F8 (aquellos cuyas direcciones son múltiplos de 8), y por lo tanto incluyen comprendiendo los bits los acumuladores A, B y la palabra de estado del programa PSW. La dirección de la ventana de registro, siendo los bits 3 y 4 en PSW, es en sí misma direccionable como registros de bits D3 y D4, respectivamente; mientras que el bit de acarreo C (o CY), en el bit 7 de la PSW, es direccionable como registro de bit D7.

Memoria de programa

La memoria de programa (PMEM, aunque de uso menos común que IRAM y XRAM) tiene hasta 64 KB de memoria de solo lectura, comenzando en la dirección 0 en un espacio de direcciones separado. Puede estar dentro o fuera del chip, según el modelo particular de chip que se utilice. La memoria de programa es de solo lectura, aunque algunas variantes del 8051 usan memoria flash en chip y proporcionan un método para reprogramar la memoria en el sistema o en la aplicación.

Además del código, es posible almacenar datos de solo lectura, como tablas de búsqueda en la memoria del programa, recuperadas por el id MOVC A,@A+DPTR o MOVC A,@A+PC instrucciones. La dirección se calcula como la suma del acumulador de 8 bits y un registro de 16 bits (PC o DPTR).

Instrucciones especiales de llamada y salto (AJMP y ACALL) reduce ligeramente el tamaño del código que accede localmente (dentro de la misma memoria de programa de 2 KB).

Cuando se requiere un código de más de 64 K, un sistema común hace que el código cambie de banco, con E/S de uso general seleccionando los bits de dirección superiores. Algunos compiladores 8051 hacen provisiones para acceder automáticamente al código paginado. En estos sistemas, los vectores de interrupción y la tabla de paginación se colocan en los primeros 32 K del código y siempre son residentes.

Memoria de datos externa

La memoria de datos externa (XRAM) es un tercer espacio de direcciones, también comienza en la dirección 0 y permite 16 bits de espacio de direcciones. También puede estar dentro o fuera del chip; lo que lo hace "externo" es que se debe acceder usando el MOVX (mover externo) instrucción. Muchas variantes del 8051 incluyen los 256 bytes estándar de IRAM más algunos kilobytes de XRAM en el chip.

Se puede acceder a los primeros 256 bytes de XRAM mediante MOVX A, @R0, MOVX A,@ R1, MOVX @R0,A y MOVX @R1,A instrucciones. Se puede acceder a los 64 KB completos usando MOVX A,@DPTR y MOVX @DPTR,A. La dirección de 16 bits requiere que el programador cargue el registro de índice de 16 bits. Por este motivo, los accesos a la memoria RAM con direcciones de 16 bits son sustancialmente más lentos.

Algunas CPU permiten que la dirección indirecta de 8 bits use cualquier registro de propósito general de 8 bits.

Para permitir el uso de esta función, algunos microcontroladores compatibles con 8051 con RAM interna de más de 256 bytes, o que no pueden acceder a la RAM externa, acceden a la RAM interna como si fuera externa y tienen un registro de función especial (por ejemplo, PDATA) eso les permite establecer la dirección superior de la página de 256 bytes. Esto emula el modo MCS8051 que puede paginar el byte superior de una dirección de RAM configurando los pines de E/S de propósito general.

Cuando se requiere una RAM de más de 64 K, un sistema común hace que la RAM cambie de banco, con E/S de uso general seleccionando los bits de dirección superiores. Algunos compiladores 8051 hacen provisiones para acceder automáticamente a los datos paginados.

Registros

El único registro en un 8051 que no está mapeado en memoria es el contador de programa (PC) de 16 bits. Esto especifica la dirección de la siguiente instrucción a ejecutar. Las instrucciones de bifurcación relativas proporcionan un desplazamiento con signo de 8 bits que se agrega a la PC.

Se puede acceder a ocho registros de propósito general R0–R7 con instrucciones un byte más cortas que otras. Están asignados a IRAM entre 0x00 y 0x1F. Solo se utilizan ocho bytes de ese rango en un momento dado, determinado por los dos bits de selección de banco en la PSW.

La siguiente es una lista parcial de los registros del 8051, que están mapeados en memoria en el espacio de registro de funciones especiales:

- Stack pointer, SP (0x81)

- Este es un registro de 8 bits utilizado por las instrucciones de llamada y retorno de la subrutina. La pila crece hacia arriba; el SP es incrementado antes de empujar, y decrementado después de cortar un valor.

- Data pointer, DP (0x82–83)

- Este es un registro de 16 bits que se utiliza para acceder a PMEM y XRAM.

- Palabra de estado del programa, PSW (0xD0)

- Esto contiene importantes banderas de estado, por número de bits:

- Paridad, P. da la paridad (XOR de los bits) del acumulador, A.

- Usuario definido, UD. Puede ser leído y escrito por software; no afectado de otra manera por hardware.

- Bandera de desbordamiento, OV. Se establece cuando la adición produce un flujo firmado.

- Regístrate select 0, RS0. El bajo pedido del banco registrador. Establece cuando los bancos en 0x08 o 0x18 están en uso.

- Registro selecto 1, RS1. La parte de alto orden del banco registrado. Establece cuando los bancos de 0x10 o 0x18 están en uso.

- Bandera 0, F0. Puede ser leído y escrito por software; no afectado de otra manera por hardware.

- Carga auxiliar, AC. Conjunto cuando la adición produce una carga de bit 3 a bit 4.

- Carry bit, C. A menudo utilizado como el registro general de cálculos de bits, o el "acumulador booleano".

- Acumulador, A (0xE0)

- Este registro es utilizado por la mayoría de las instrucciones.

- B register (0xF0)

- Esto se utiliza como una extensión al acumulador para multiplicar y dividir instrucciones.

256 bits individuales son directamente direccionables. Estas son las 16 ubicaciones IRAM desde 0x20–0x2F, y los 16 registros de funciones especiales 0x80, 0x88, 0x90,..., 0xF8. Se puede acceder directamente a cualquier bit de estos bytes mediante una variedad de operaciones lógicas y ramas condicionales.

Tenga en cuenta que el PSW no contiene los indicadores negativos (N) o cero (Z) comunes. Para el primero, el bit más significativo del acumulador se puede direccionar directamente, ya que es un SFR direccionable por bits. Para este último, hay instrucciones explícitas para saltar sobre si el acumulador es cero o no. También hay una operación de comparación y salto de dos operandos.

El bit de paridad (P) se usa a menudo para implementar modos en serie que incluyen paridad. Para respaldar esto, los UART MCS51 estándar podrían enviar 9 bits.

Microarquitectura

La microarquitectura del Intel MCS8051 es propietaria, pero las características publicadas sugieren cómo funciona. Es un procesador multiciclo. El MCS8051 usó 12 ciclos de reloj para la mayoría de las instrucciones. Muchas instrucciones utilizan un acumulador. Por el contrario, la mayoría de las computadoras compatibles ejecutan instrucciones en uno a tres ciclos, excepto las instrucciones de multiplicación y división. La velocidad mucho más alta es una de las principales razones por las que estos han reemplazado al MCS8051 en la mayoría de las aplicaciones.

Cada interrupción tiene cuatro prioridades. Dentro de cada prioridad, las interrupciones de los dispositivos tienen una prioridad fija.

Conjunto de instrucciones

Las instrucciones tienen entre 1 y 3 bytes de longitud y constan de un byte de código de operación inicial, seguido de hasta 2 bytes de operandos.

1⁄4 del código de operación bytes, x0–x3, se utilizan para códigos de operación irregulares.

3⁄4 del código de operación bytes, x4–xF, se asignan a 16 instrucciones ALU básicas con 12 operandos posibles. El nibble menos significativo del código de operación selecciona el operando principal de la siguiente manera:

- x8-xF: Registro directo, R0-R7.

- x6 –x7: Registro indirecto, @R0 o @R1.

- x5: Memoria directa, un byte especifica una ubicación IRAM o SFR.

- x4: Inmediatamente, un byte siguiente especifica una constante de 8 bits. Cuando el operand es un destino (

INC operand,DEC operand) o la operación ya incluye una fuente inmediata (MOV operand,#data,CJNE operand,#data,offset), esto en cambio especifica que el acumulador es utilizado.

El cuarteto más significativo especifica la operación de la siguiente manera. No todos admiten todos los modos de direccionamiento; el modo inmediato en particular no está disponible cuando se escribe en el operando principal. Los nemotécnicos de instrucciones utilizan el orden de operandos destino, origen.

- 0Sí.:

INC operand - Incremento del operario especificado. Modo inmediato (código 0x04) especifica el acumulador,

INC A. - 1Sí.:

DEC operand - Decrementar el operand especificado. Modo inmediato (código 0x14) especifica el acumulador,

DEC A. - 2Sí.:

ADD A,operand - Añadir el operando al acumulador, A. Opcode 0x23 (

RL A, "rotate izquierda" pero en realidad un turno izquierda) puede ser pensado comoADD A,A. - 3Sí.:

ADDC A,operand - Añadir el operand, más el bit C, al acumulador. Opcode 0x33 (oculto)

RLC A, girar a la izquierda a través del transporte) se puede considerar comoADDC A,A. - 4Sí.:

ORL A,operand - Lógica o operando en el acumulador. Dos formas de memoria-destinación de esta operación,

ORL address,#datayORL address,A, se especifican por opcodes 0x43 y 0x42. - 5Sí.:

ANL A,operand - Lógica y operada en el acumulador. Dos formas de memoria-destinación de esta operación,

ANL address,#datayANL address,A, se especifican por opcodes 0x53 y 0x52. - 6Sí.:

XRL A,operand - Lógica exclusiva-O el operado en el acumulador. Dos formas de memoria-destinación de esta operación,

XRL address,#datayXRL address,A, se especifican por opcodes 0x63 y 0x62. - 7Sí.:

MOV operand,#data - Muévete inmediatamente al operand. Modo inmediato (código 0x74) especifica el acumulador,

MOV A,#data. - 8Sí.:

MOV address,operand - Mover valor a un registro IRAM o SFR. El modo inmediato (opcode 0x84) no se utiliza para esta operación, ya que duplica el opcode 0x75.

- 9Sí.:

SUBB A,operand - Retira el operand del acumulador. Esta operación presta y no hay subtracto sin prestado.

- ASí.:

MOV operand,address - Mover el valor de un registro IRAM o SFR. El modo inmediato (opcode 0xA4) no se utiliza, ya que los inmediatos sólo sirven como fuentes. El modo directo de memoria (opcode 0xA5) no se utiliza, ya que duplica 0x85.

- BSí.:

CJNE operand,#data,offset - Compare que operan de inmediato

#data, y saltar a PC + offset si no es igual. Modos directos inmediatos y de memoria (opcodes 0xB4 y 0xB5) comparan el operario con el acumulador,CJNE A,operand,offset. Tenga en cuenta que no hay comparación y salto si la instrucción igual,CJE. - CSí.:

XCH A,operand - Intercambia el acumulador y el operando. El modo inmediato (opcode 0xC4) no se utiliza para esta operación.

- DSí.:

DJNZ operand,offset - Decrementar el operand, y saltar a PC + offset si el resultado no es cero. Modo inmediato (opcode 0xD4), y registro modo indirecto (0xD6, 0xD7) no se utilizan.

- ESí.:

MOV A,operand - Muévete operando al acumulador. El modo inmediato no se utiliza para esta operación (opcode 0xE4), ya que duplica el opcode 0x74.

- FSí.:

MOV operand,A - Mueva el acumulador al operario. El modo inmediato (opcode 0xF4) no se utiliza, ya que no tendría ningún efecto.

Solo AGREGAR, ADDC y SUBB instrucciones establecer banderas PSW. El INC, DEC y las instrucciones lógicas no. El CJNE modifica el bit C únicamente, al préstamo que resulta de operand1 − operand2.

Las instrucciones irregulares comprenden 64 códigos de operación, con modos de direccionamiento más limitados, además de varios códigos de operación eliminados de modos no aplicables en las instrucciones regulares.

| Opcode | x0 | x1 | x2 | x3 | x4 |

|---|---|---|---|---|---|

| 0Sí. | NOP |

| LJMP addr16 | RR A (gire a la derecha) | INC A |

| 1Sí. | JBC bit,offset (jump si bit set with clear)

| LCALL addr16 | RRC A (rotar derecho a través del transporte) | DEC A | |

| 2Sí. | JB bit,offset (golpe si juego de bits)

| RET | RL A (rota a la izquierda) | ADD A,#data | |

| 3Sí. | JNB bit,offset (salto si poco claro)

| RETI | RLC A (rotación izquierda a través de la carga) | ADDC A,#data | |

| 4Sí. | JC offset (salto si se pone)

| ORL address,A | ORL address,#data | ORL A,#data | |

| 5Sí. | JNC offset (salto si sigue claro)

| ANL address,A | ANL address,#data | ANL A,#data | |

| 6Sí. | JZ offset (salto si cero)

| XRL address,A | XRL address,#data | XRL A,#data | |

| 7Sí. | JNZ offset (salto si no cero)

| ORL C,bit | JMP @A+DPTR | MOV A,#data | |

| 8Sí. | SJMP offset (salto corto)

| ANL C,bit | MOVC A,@A+PC | DIV AB | |

| 9Sí. | MOV DPTR,#data16 | MOV bit,C | MOVC A,@A+DPTR | SUBB A,#data | |

| ASí. | ORL C,/bit | MOV C,bit | INC DPTR | MUL AB | |

| BSí. | ANL C,/bit | CPL bit | CPL C | CJNE A,#data,offset | |

| CSí. | PUSH address | CLR bit | CLR C | SWAP A | |

| DSí. | POP address | SETB bit | SETB C | DA A (Ajuste decimal)

| |

| ESí. | MOVX A,@DPTR | MOVX A,@R0 | MOVX A,@R1 | CLR A | |

| FSí. | MOVX @DPTR,A | MOVX @R0,A | MOVX @R1,A | CPL A |

- A5

- No utilizados

- B5

CJNE A,address,offset- D6–7

XCHD A,@R0–1intercambio de nibble de operandos de bajo orden.

El SJMP (salto corto) el código de operación toma un operando de byte de desplazamiento relativo firmado y transfiere el control allí en relación con la dirección de la siguiente instrucción. El AJMP/ACALL combinan los tres bits más significativos del byte del código de operación con el siguiente byte para especificar un 11- destino de bit que se utiliza para reemplazar los 11 bits inferiores del registro de PC (los 5 bits superiores del registro de PC permanecen intactos). Para direcciones más grandes, LJMP y LCALL permiten un destino de 16 bits.

Una de las razones de la popularidad del 8051 es su variedad de operaciones en bits individuales. Los bits siempre se especifican mediante direcciones absolutas; no hay direccionamiento indexado o indirecto por registro. Las instrucciones que operan en bits individuales son:

SETB bit,CLR bit,CPL bit: Establecer, aclarar o complementar el bit especificadoJB bit,offset: Salta si el bit setJNB bit,offset: Saltar si poco claroJBC bit,offset: Salta si el bit se fija, y el bit claroMOV C,bit,MOV bit,C: Mueva el bit especificado al bit de carga, o viceversaORL C,bit,ORL C,/bit: O el bit (o su complemento) al bit de cargaANL C,bit,ANL C,/bit: Y el bit (o su complemento) al bit de carga

Un operando de bit se escribe en la forma address.number. Debido a que la bandera de acarreo es el bit 7 de la palabra de estado del programa direccionable por bits, el SETB C, CLR C y CPL C las instrucciones son equivalentes más breves a SETB PSW.7, CLR PSW.7 y CPL PSW.7.

Aunque la mayoría de las instrucciones requieren que un operando sea el acumulador o una constante inmediata, el código de operación 0x85 realiza MOV directamente entre dos ubicaciones de RAM internas.

Programación

Hay varios compiladores de lenguaje de programación de alto nivel para el 8051. Hay varios compiladores de C disponibles para el 8051, la mayoría de los cuales permiten al programador especificar dónde debe almacenarse cada variable en sus seis tipos de memoria y brindan acceso a Características de hardware específicas del 8051, como los bancos de registros múltiples y las instrucciones de manipulación de bits. Hay muchos compiladores de C comerciales. Small Device C Compiler (SDCC) es un popular compilador C de código abierto. Otros lenguajes de alto nivel como C++, Forth, BASIC, Object Pascal, Pascal, PL/M y Modula-2 están disponibles para el 8051, pero se usan menos que C y ensamblador.

Debido a que IRAM, XRAM y PMEM (solo lectura) tienen una dirección 0, los compiladores de C para la arquitectura 8051 proporcionan pragmas específicos del compilador u otras extensiones para indicar dónde se debe almacenar un dato en particular (es decir, constantes en PMEM o variables que necesitan acceso rápido en IRAM). Dado que los datos pueden estar en uno de los tres espacios de memoria, generalmente se proporciona un mecanismo para permitir determinar a qué memoria se refiere un puntero, ya sea restringiendo el tipo de puntero para incluir el espacio de memoria o almacenando metadatos con el puntero.

Procesadores relacionados

Intel descontinuó su línea de productos MCS-51 en marzo de 2007; sin embargo, hay muchos productos 8051 mejorados o propiedad intelectual de silicio agregada regularmente por otros proveedores.

El predecesor del 8051, el 8048, se usó en el teclado de la primera PC de IBM, donde convertía las pulsaciones de teclas en el flujo de datos en serie que se envía a la unidad principal de la computadora. Un Intel 8049 desempeñó un papel similar en Sinclair QL. El 8048 y sus derivados todavía se utilizan hoy en día para los teclados de modelos básicos.

El 8031 era una versión reducida del 8051 original que no tenía memoria de programa interna (memoria de solo lectura, ROM). Para usar este chip, se tuvo que agregar una ROM externa que contuviera el programa que el 8031 buscaría y ejecutaría. Un chip 8051 podría venderse como un 8031 sin ROM, ya que la ROM interna del 8051 está desactivada por el estado normal del pin EA en un diseño basado en 8031. Un proveedor puede vender un 8051 como un 8031 por varias razones, como un código defectuoso en la ROM del 8051 o simplemente un exceso de oferta de 8051 y una escasez de 8031.

El 8052 era una versión mejorada del 8051 original que presentaba 256 bytes de RAM interna en lugar de 128 bytes, 8 KB de ROM en lugar de 4 KB y un tercer temporizador de 16 bits. La mayoría de los microcontroladores compatibles con 8051 modernos incluyen estas características.

El 8032 tenía las mismas características que el 8052 excepto que carecía de memoria de programa ROM interna.

El 8751 era un 8051 con 4 KB de EPROM en lugar de 4 KB de ROM. Eran idénticos excepto por el tipo de memoria no volátil. Esta parte estaba disponible en un paquete de cerámica con una ventana de cuarzo transparente sobre la parte superior de la matriz para que la luz ultravioleta pudiera usarse para borrar la EPROM. Las partes relacionadas son: 8752 tenía EPROM de 8 KB, 8754 tenía EPROM de 16 KB, 8758 tenía EPROM de 32 KB.

El 80C537 (sin ROM) y el 80C517 (ROM de 8 KB) son versiones CMOS, diseñadas para la industria automotriz. Las mejoras incluyen principalmente periféricos nuevos y mejorados. El 80C5x7 tiene mecanismos a prueba de fallas, funciones de procesamiento de señales analógicas, capacidades de temporizador mejoradas y un periférico aritmético de 32 bits. Otras características incluyen:

- 256-byte on-chip RAM

- 256 bits directamente accesibles

- Programa externo y memoria de datos expandibles hasta 64 KB

- Conversor A/D de 8 bits con 12 entradas multiplexadas

- Arithmetic peripheral puede realizar 16×16→32-bit multiplication, 32/16→16-bit division, 32-bit shift and 32-bit normalize operations

- Ocho puntos de datos en lugar de uno para el tratamiento indirecto del programa y la memoria de datos externa

- Instalaciones de vigilancia ampliadas

- Nueve puertos I/O

- Dos interfaces de serie de dúplex completo con generadores de frecuencia de baud individuales

- Cuatro sistemas de interrupción de nivel prioritario, 14 vectores interrumpidos

- Tres modos de ahorro de energía

- Fuentes Intel MCS-51

Proveedores de derivados

Más de 20 fabricantes independientes producen procesadores compatibles con MCS-51.

- Microcontroladores derivados Intel MCS-51

Analog Devices ha desarrollado otros IC o IP compatibles con el MCS-51, integralminsk, Kristall Kyiv y NIEET Voronezh.

Usar como propiedad intelectual

Hoy en día, los 8051 todavía están disponibles como piezas discretas, pero se usan principalmente como núcleos de propiedad intelectual de silicio. Disponibles en código fuente de lenguaje de descripción de hardware (como VHDL o Verilog) o formularios de lista de conexiones FPGA, estos núcleos generalmente se integran dentro de sistemas integrados, en productos que van desde unidades flash USB hasta lavadoras y complejos sistemas de comunicación inalámbrica en un chip. Los diseñadores utilizan núcleos IP de silicio 8051, debido al tamaño más pequeño y la menor potencia, en comparación con los procesadores de 32 bits como la serie ARM Cortex-M, MIPS y BA22.

Los núcleos 8051 modernos son más rápidos que las versiones empaquetadas anteriores. Las mejoras de diseño han aumentado el rendimiento del 8051 al tiempo que conservan la compatibilidad con el conjunto de instrucciones MCS 51 original. El Intel 8051 original funcionaba a 12 ciclos de reloj por ciclo de máquina y la mayoría de las instrucciones se ejecutaban en uno o dos ciclos de máquina. Una frecuencia de reloj máxima típica de 12 MHz significaba que estos viejos 8051 podían ejecutar un millón de instrucciones de un solo ciclo, o 500 000 instrucciones de dos ciclos, por segundo. Por el contrario, los núcleos IP de silicio 8051 mejorados ahora funcionan a un ciclo de reloj por ciclo de máquina y tienen frecuencias de reloj de hasta 450 MHz. Eso significa que un procesador compatible con 8051 ahora puede ejecutar 450 millones de instrucciones por segundo.

MCU basadas en 8051

- ABOV: MC94F, MC95F, MC96F series

- Infineon: XC800

- Maxim Integrated (antes Dallas): serie DS80, etc.

- Mentor Graphics: M8051EW etc. diseñado para Mentor por SYNTILL8

- Megawin: serie 74, 82, 84, 86, 87 y 89

- Microchip (antes Atmel): AT89C51, AT89S51, AT83C5134, etc.

- NXP: serie NXP700 y NXP900

- Siemens SAB 80532-N

- Siemens SDA 30C164-2 (procesador sin romero)

- Medición de electricidad Silergy SoCs: 71M6511, 71M6513, 71M6531, 71M6533, 71M6534, 71M6542, 71M6543 Medición de energía SoCs: 78M6631, 78M6618, 78M6613, 78M6612

- Laboratorios de silicona: serie C8051 y serie EFM8

- Silicon Storage Technology: FlashFlex51 MCU (SST89E52RD2, SST89E54RD2, SST89E58RD2, SST89E516RD2SST89V52RD2, SST89V54RD2, SST89V58RD2, SST89V516RD2)

- STC STC89C51RC, STC90C51RC, STC90C58AD, STC10F08XE, STC11F60XE, STC12C5410AD, STC12C5202AD, STC12C5A60S2, STC12C5628AD, STC15F100, STC15F204EA, STC15F2

- Texas Instruments CC111x, CC24xx y CC25xx familias de RF SoCs

- WCH (Nanjing Qinheng Microelectronics): CH551, CH552, CH554, CH546, CH547, CH548, CH558, CH559

Variantes del procesador de señal digital (DSP)

Existen varias variantes con un procesador de señal digital (DSP) adicional de 16 bits (por ejemplo, para codificación/descodificación de MP3 o Vorbis) con hasta 675 millones de instrucciones por segundo (MIPS) e interfaz USB 2.0 integrada o como propiedad intelectual.

Microcontrolador mejorado compatible con binario de 8 bits: familia MCS-151

En 1996, Intel anunció la familia MCS-151, una variante hasta 6 veces más rápida, totalmente binaria y con un conjunto de instrucciones compatible con 8051. A diferencia de su 8051, MCS-151 es una CPU segmentada, con 16 bits bus de código interno y es 6 veces la velocidad. Intel también descontinuó la familia MCS-151, pero está ampliamente disponible en variantes parcialmente mejoradas y compatibles binariamente.

Microcontrolador compatible con binario de 8/16/32 bits: familia MCS-251

Intel presentó en 1996 el microcontrolador 80251 de 8/16/32 bits con un espacio de direcciones de 16 MB (24 bits) y un ciclo de instrucciones 6 veces más rápido. Puede funcionar como un 8051 de 8 bits, tiene 24 direccionamiento lineal de bits, una ALU de 8 bits, instrucciones de 8 bits, instrucciones de 16 bits, un conjunto limitado de instrucciones de 32 bits, 16 registros de 8 bits, 16 registros de 16 bits (8 registros de 16 bits que no comparten espacio con cualquier registro de 8 bits y 8 registros de 16 bits que contienen 2 registros de 8 bits por registro de 16 bits) y 10 registros de 32 bits (2 registros dedicados de 32 bits y 8 registros de 32 bits que contienen 2 registros de 16 bits por registro de 32 bits).

Cuenta con instrucciones ampliadas (consulte también la guía del programador) y variantes posteriores con mayor rendimiento, también disponibles como propiedad intelectual (IP). Está canalizado en 3 etapas. Intel también descontinuó la familia MCS-251, pero está ampliamente disponible en variantes parcialmente mejoradas y compatibles binariamente de muchos fabricantes.

Contenido relacionado

Steve Wozniak

Motorola 6800

PowerPC