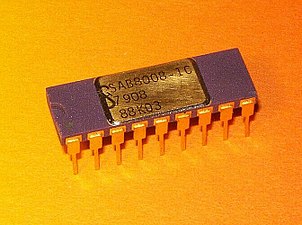

Intel 8008

El Intel 8008 ("ocho mil ocho" o "ochenta y ocho") es uno de los primeros microprocesadores orientados a bytes diseñado por Computer Terminal Corporation (CTC), implementado y fabricado por Intel, y presentado en abril de 1972. Es una CPU de 8 bits con un bus de direcciones externo de 14 bits que podría abordar 16 KB de memoria. Originalmente conocido como el 1201, el chip fue encargado por Computer Terminal Corporation (CTC) para implementar un conjunto de instrucciones de su diseño para su terminal programable Datapoint 2200. Como el chip se retrasó y no cumplió con los objetivos de rendimiento de CTC, el 2200 terminó usando la propia CPU basada en TTL de CTC. Un acuerdo permitió a Intel comercializar el chip a otros clientes después de que Seiko expresó su interés en usarlo para una calculadora.

Historia

CTC se formó en San Antonio en 1968 bajo la dirección de Austin O. "Gus" Roche y Phil Ray, ambos ingenieros de la NASA. Roche, en particular, estaba principalmente interesado en producir una computadora de escritorio. Sin embargo, dada la inmadurez del mercado, el plan de negocios de la compañía mencionaba solo un reemplazo del Teletype Model 33 ASR, que se envió como Datapoint 3300. El gabinete fue diseñado deliberadamente para caber en el mismo espacio que una máquina de escribir IBM Selectric y usó una pantalla de video con la misma relación de aspecto que una tarjeta perforada de IBM. Aunque comercialmente exitoso, el 3300 tenía problemas de calor continuos debido a la cantidad de circuitos empaquetados en un espacio tan pequeño.

Para abordar el calentamiento y otros problemas, se inició un rediseño que presentaba la parte de la CPU del circuito interno reimplementada en un solo chip. En busca de una empresa capaz de producir su diseño de chip, Roche recurrió a Intel, entonces principalmente un proveedor de chips de memoria. Roche se reunió con Bob Noyce, quien expresó su preocupación por el concepto; John Frassanito recuerda que 'Noyce dijo que era una idea intrigante y que Intel podría hacerlo, pero sería un movimiento tonto. Dijo que si tiene un chip de computadora, solo puede vender un chip por computadora, mientras que con memoria, puede vender cientos de chips por computadora. Otra preocupación importante era que la base de clientes existente de Intel compraba sus chips de memoria para usarlos con sus propios diseños de procesadores; si Intel introdujera su propio procesador, podrían ser vistos como un competidor y sus clientes podrían buscar memoria en otra parte. Sin embargo, Noyce acordó un contrato de desarrollo de $50,000 a principios de 1970. También se incorporó a Texas Instruments (TI) como segundo proveedor.

TI pudo hacer muestras del 1201 basándose en dibujos de Intel, pero resultaron tener errores y fueron rechazadas. Las propias versiones de Intel se retrasaron. CTC decidió volver a implementar la nueva versión de la terminal utilizando TTL discreto en lugar de esperar a una CPU de un solo chip. El nuevo sistema se lanzó como Datapoint 2200 en la primavera de 1970, con su primera venta a General Mills el 25 de mayo de 1970. CTC detuvo el desarrollo del 1201 después del lanzamiento del 2200, ya que ya no era necesario. Seis meses después, Seiko se acercó a Intel y expresó su interés en usar el 1201 en una calculadora científica, probablemente después de ver el éxito del Intel 4004 más simple que usa Busicom en sus calculadoras comerciales. Siguió un pequeño rediseño, bajo la dirección de Federico Faggin, el diseñador del 4004, ahora líder del proyecto del 1201, que se expandió de un diseño de 16 pines a 18 pines, y el nuevo 1201 se entregó a CTC a finales de 1971..

En ese momento, CTC se había mudado una vez más, esta vez al Datapoint 2200 II, que era más rápido. El 1201 ya no era lo suficientemente potente para el nuevo modelo. CTC votó para poner fin a su participación en el 1201, dejando la propiedad intelectual del diseño a Intel en lugar de pagar el contrato de $50,000. Intel le cambió el nombre a 8008 y lo puso en su catálogo en abril de 1972 a un precio de 120 dólares. Este cambio de nombre intentó aprovechar el éxito del chip 4004, presentando el 8008 simplemente como un puerto de 4 a 8, pero el 8008 no se basa en el 4004. El 8008 se convirtió en un diseño comercialmente exitoso. A esto le siguió el Intel 8080, y luego la exitosa familia Intel x86.

Uno de los primeros equipos en construir un sistema completo alrededor del 8008 fue Bill Pentz' equipo de la Universidad Estatal de California, Sacramento. El Sac State 8008 fue posiblemente la primera microcomputadora verdadera, con un sistema operativo de disco construido con lenguaje ensamblador IBM Basic en PROM, todo manejando una pantalla a color, disco duro, teclado, módem, lector de cinta de audio/papel e impresora. El proyecto comenzó en la primavera de 1972 y, con la ayuda clave de Tektronix, el sistema estaba en pleno funcionamiento un año después. Bill ayudó a Intel con el kit MCS-8 y proporcionó información clave para el conjunto de instrucciones Intel 8080, lo que ayudó a que fuera útil para la industria y los aficionados.

En el Reino Unido, un equipo de S. E. Laboratories Engineering (EMI) dirigido por Tom Spink construyó en 1972 una microcomputadora basada en una muestra preliminar del 8008. Joe Hardman amplió el chip con una pila externa. Esto, entre otras cosas, le permitió guardar y recuperar energía en caso de falla. Joe también desarrolló una impresora de pantalla directa. El sistema operativo se escribió utilizando un metaensamblador desarrollado por L. Crawford y J. Parnell para Digital Equipment Corporation PDP-11. El sistema operativo se grabó en una PROM. Fue impulsado por interrupciones, en cola y basado en un tamaño de página fijo para programas y datos. Se elaboró un prototipo operativo para la gerencia, quien decidió no continuar con el proyecto.

El 8008 fue la CPU de las primeras computadoras personales comerciales sin calculadora (excluyendo el propio Datapoint 2200): el kit SCELBI de EE. UU. y el Micral N francés y el MCM/70 canadiense prefabricados. También fue el microprocesador de control de los primeros modelos de la familia de terminales de computadora 2640 de Hewlett-Packard.

Intel ofreció un simulador de conjunto de instrucciones para el 8008 denominado INTERP/8. Fue escrito en FORTRAN.

Diseño

El 8008 se implementó en una lógica PMOS de modo de mejora de puerta de silicio de 10 μm. Las versiones iniciales podrían funcionar con frecuencias de reloj de hasta 0,5 MHz. Esto se aumentó más tarde en el 8008-1 a un máximo especificado de 0,8 MHz. Las instrucciones toman entre 5 y 11 estados T, donde cada estado T es de 2 ciclos de reloj. Las cargas de registro-registro y las operaciones de ALU toman 5T (20 μs a 0,5 MHz), la memoria de registro 8T (32 μs), mientras que las llamadas y los saltos (cuando se toman) toman 11 estados T (44 μs). El 8008 es un poco más lento en términos de instrucciones por segundo (36 000 a 80 000 a 0,8 MHz) que el Intel 4004 de 4 bits y el Intel 4040. la mayoría de las aplicaciones tiene una ventaja de velocidad significativa sobre estos procesadores. El 8008 tiene 3.500 transistores.

El chip (limitado por su DIP de 18 pines) tiene un solo bus de 8 bits y requiere una cantidad significativa de lógica de soporte externo. Por ejemplo, la dirección de 14 bits, que puede acceder a '16 K × 8 bits de memoria', debe quedar bloqueada por parte de esta lógica en un registro de dirección de memoria externa (MAR). El 8008 puede acceder a 8 puertos de entrada y 24 puertos de salida.

Para el uso de controladores y terminales CRT, este es un diseño aceptable, pero es bastante engorroso de usar para la mayoría de las demás tareas, al menos en comparación con las próximas generaciones de microprocesadores. Algunos de los primeros diseños de computadoras se basaron en él, pero la mayoría usaría el último y mejorado Intel 8080 en su lugar.

Diseños de procesadores relacionados

El posterior NMOS Intel 8080 de 40 pines amplió los registros 8008 y el conjunto de instrucciones e implementa una interfaz de bus externa más eficiente (usando los 22 pines adicionales). A pesar de una relación arquitectónica cercana, el 8080 no se hizo compatible binariamente con el 8008, por lo que un programa 8008 no se ejecutaría en un 8080. Sin embargo, como Intel usaba dos sintaxis de ensamblaje diferentes en ese momento, el 8080 podría usarse en un 8008 lenguaje ensamblador compatible con versiones anteriores.

El Intel 8085 es una versión eléctricamente modernizada del 8080 que usa transistores de modo de agotamiento y también agregó dos nuevas instrucciones.

El Intel 8086, el procesador x86 original, es una extensión no estricta del 8080, por lo que también se parece ligeramente al diseño original del Datapoint 2200. Casi todas las instrucciones de Datapoint 2200 y 8008 tienen un equivalente no solo en el conjunto de instrucciones de 8080, 8085 y Z80, sino también en el conjunto de instrucciones de los procesadores x86 modernos (aunque las codificaciones de instrucciones son diferentes).

Características

La arquitectura 8008 incluye las siguientes características:

- Siete registros de 8 bits "scratchpad": El principal acumulador (A) y otros seis registros (B, C, D, E, H y L).

- Programa de 14 bits (PC).

- Apilación de llamadas de dirección push-down de siete niveles. En realidad se utilizan ocho registros, siendo el registro más alto el PC.

- Cuatro banderas de estado del código de condiciones: port (C), incluso paridad (P), cero (Z), y signo (S).

- Acceso directo a la memoria usando los registros H y L (HL) como un puntero de datos de 14 bits (los dos bits superiores son ignorados).

Código de ejemplo

El siguiente código fuente ensamblador 8008 es para una subrutina llamada MEMCPY que copia un bloque de bytes de datos de un tamaño determinado de una ubicación a otra.

001700 000 001701 000 001702 000 001703 000 001704 000 001705 000 002000 066 304 002002 056 003 002004 327 002005 060 002006 317 002007 302 002010 261 002011 053 002012 302 002013 024 001 002015 320 002016 301 002017 034 000 002021 310 002022 066 300 002024 056 003 002026 302 002027 207 002030 340 002031 060 002032 301 002033 217 002034 350 002035 364 002036 337 002037 066 302 002041 056 003 002043 302 002044 207 002045 340 002046 060 002047 301 002050 217 002051 350 002035 364 002052 373 002053 104 007 004 002056 | ; MEMCPY --; Copiar un bloque de memoria de un lugar a otro.;; Parámetros de entrada; SRC: 14-bit dirección del bloque de datos de origen; DST: 14-bit address of target data block; CNT: cuenta de bytes de 14 bits para copiar ORG 1700Q ; Datos a 001700qSRC DFB 0 ;SRC, byte bajo DFB 0 ; alto byteDST DFB 0 ; DST, byte bajo DFB 0 ; alto byteCNT DFB 0 ;CNT, byte bajo DFB 0 ; alto byte ORG 2000Q ;Code at 002000qMEMCPY LLI CNT+0 ;HL = addr(CNT) LHI CNT+1 LCM ;BC = CNT INL LBMLOOP LAC ; Si BC = 0, ORB RTZ ; RetornoDECCNT LAC ;BC = BC - 1 SUI 1 LCA LAB OSE 0 LBAGETSRC LLI SRC+0 ;HL = addr(SRC) LHI SRC+1 LAC ;HL = SRC + BC ADM ;E = C + (HL) LEA ; (suma inferior) INL ;point to upper SRC LAB ACM ;H = B + (HL) + CY LHA ; (suma superior) LLE ;L = E LDM ; Carga D de (HL)GETDST LLI DST+0 ;HL = addr(DST) LHI DST+1 LAC ;HL = DST + BC ADM ;ADD code same as above LEA INL LAB ACM LHA LLE LMD ;Store D to (HL) JMP LOOP ; Repetir el bucle FIN |

En el código anterior, todos los valores se dan en octal. Ubicaciones SRC, DST, y CNT son parámetros de 16 bits para la subrutina llamada MEMCPY. En realidad, solo se utilizan 14 bits de los valores, ya que la CPU tiene solo un espacio de memoria direccionable de 14 bits. Los valores se almacenan en formato little-endian, aunque esta es una elección arbitraria, ya que la CPU es incapaz de leer o escribir más de un byte en la memoria a la vez. Dado que no hay ninguna instrucción para cargar un registro directamente desde una dirección de memoria determinada, primero se debe cargar el par de registros HL con la dirección, y luego se puede cargar el registro de destino desde el operando M, que es una carga indirecta desde la ubicación de la memoria. en el par de registros HL. El par de registros BC se carga con el valor del parámetro CNT y decrementado al final del bucle hasta que se convierte en cero. Tenga en cuenta que la mayoría de las instrucciones utilizadas ocupan un solo código de operación de 8 bits.

Diseñadores

- CTC ()Conjunto de instrucciones y arquitecturaVíctor Pobre y Harry Pyle.

- Intel ()Implementación en silicona):

- Ted Hoff, Stan Mazor y Larry Potter (IBM Chief Scientist) propusieron una implementación de un solo chip de la arquitectura CTC, utilizando memoria RAM-register en lugar de memoria de registro de cambios, y también añadió algunas instrucciones e instalación de interrupción. El diseño de chip 8008 (originalmente llamado 1201) comenzó antes del desarrollo 4004. Hoff y Mazor, sin embargo, no pudieron ni desarrollar un "diseño de silicon" porque no eran ni diseñadores de chips ni desarrolladores de procesos, y además la metodología y circuitos de diseño basados en silicio necesarios, bajo el desarrollo de Federico Faggin para los 4004, todavía no estaban disponibles.

- Federico Faggin, después de haber terminado el diseño de los 4004, se convirtió en líder del proyecto desde enero de 1971 hasta su finalización exitosa en abril de 1972, después de haber sido suspendido – por falta de progreso – durante unos siete meses.

- Hal Feeney, ingeniero de proyectos, hizo el diseño lógico detallado, el diseño de circuitos y el diseño físico bajo la supervisión de Faggin, empleando la misma metodología de diseño que Faggin había desarrollado originalmente para el microprocesador Intel 4004, y utilizando los circuitos básicos que había desarrollado para el 4004. Un logotipo combinado de "HF" se grabó en el chip aproximadamente a la mitad entre las almohadillas D5 y D6.

Segundas fuentes

- Fuentes Intel 8008

Contenido relacionado

Intel 8086

Dan Bricklin

Cinta perforada