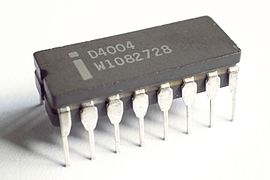

Intel 4004

El Intel 4004 es una unidad central de procesamiento (CPU) de 4 bits lanzada por Intel Corporation en 1971. Vendido por US$60, fue el primer microprocesador producido comercialmente y el primero en mucho tiempo. línea de CPU Intel.

El 4004 fue el primer ejemplo significativo de integración a gran escala, mostrando la superioridad de la tecnología de puerta de silicio MOS (SGT). En comparación con la tecnología establecida, el SGT integró en la misma área del chip el doble de transistores con cinco veces la velocidad de funcionamiento. Este aumento en el rendimiento de la función escalonada hizo posible una CPU de un solo chip, que reemplazó a las CPU de varios chips existentes. El innovador diseño del chip 4004 sirvió como modelo sobre cómo usar el SGT para circuitos lógicos y de memoria complejos, acelerando así la adopción del SGT por parte de la industria mundial de semiconductores. El desarrollador del SGT original en Fairchild fue Federico Faggin, quien diseñó el primer circuito integrado (IC) comercial que utilizó la nueva tecnología, demostrando su superioridad para aplicaciones analógicas/digitales (Fairchild 3708 en 1968). Más tarde utilizó el SGT de Intel para obtener la integración sin precedentes necesaria para fabricar el primer microprocesador de un solo chip.

El proyecto remonta su historia a 1969, cuando Busicom Corp. se acercó a Intel para diseñar una familia de siete chips para una calculadora electrónica, tres de los cuales constituían una CPU especializada para fabricar diferentes máquinas calculadoras. La CPU se basó en datos almacenados en registros de desplazamiento e instrucciones almacenadas en ROM (memoria de solo lectura). La complejidad del diseño lógico de la CPU de tres chips llevó a Marcian Hoff a proponer una arquitectura de CPU más convencional basada en datos almacenados en RAM (memoria de acceso aleatorio). Esta arquitectura era mucho más simple y de propósito más general y potencialmente podría integrarse en un solo chip, reduciendo así el costo y mejorando la velocidad. El diseño comenzó en abril de 1970 bajo la dirección de Federico Faggin con la ayuda de Masatoshi Shima, quien contribuyó a la arquitectura y luego al diseño lógico. La primera entrega de un 4004 en pleno funcionamiento fue en marzo de 1971 a Busicom para su prototipo de ingeniería de calculadora de impresión 141-PF (ahora exhibido en el Museo de Historia de la Computación en Mountain View, California). Las ventas generales comenzaron en julio de 1971.

Varias innovaciones desarrolladas por Faggin mientras trabajaba en Fairchild Semiconductor permitieron que el 4004 se produjera en un solo chip. El concepto principal fue el uso de la compuerta autoalineada, hecha de polisilicio en lugar de metal, lo que permitió que los componentes estuvieran mucho más juntos y funcionaran a mayor velocidad. Para hacer posible el 4004, Faggin también desarrolló la "carga de arranque", considerada inviable con la puerta de silicio, y el "contacto enterrado" eso permitió que las puertas de silicio se conectaran directamente a la fuente y al drenaje de los transistores sin el uso de metal. Juntas, estas innovaciones duplicaron la densidad del circuito y, por lo tanto, redujeron a la mitad el costo, lo que permitió que un solo chip contuviera 2300 transistores y funcionara cinco veces más rápido que los diseños que usaban la tecnología MOS anterior con puertas de aluminio.

Faggin mejoró posteriormente el diseño 4004 como Intel 4040 en 1974. Intel 8008 y 8080 eran diseños no relacionados a pesar de tener nombres similares.

Historia

Concepto original

En abril de 1969, Busicom se acercó a Intel para producir un nuevo diseño para una calculadora electrónica. Basaron su diseño en la arquitectura de la Olivetti Programma 101 de 1965, una de las primeras calculadoras programables de mesa del mundo. La diferencia clave era que el diseño de Busicom usaría circuitos integrados para reemplazar las placas de circuito impreso llenas de componentes individuales y registros de desplazamiento de estado sólido para la memoria en lugar del costoso cable de magnetoestricción en el 101.

A diferencia de los diseños de calculadoras anteriores, Busicom había desarrollado un concepto de procesador de propósito general con el objetivo de introducirlo en una calculadora de impresión de escritorio de gama baja y luego usar el mismo diseño para otras funciones, como cajas registradoras y cajeros automáticos.. La empresa ya había producido una calculadora con circuitos integrados lógicos de integración a pequeña escala TTL y estaba interesada en que Intel redujera la cantidad de chips utilizando las técnicas de integración a escala media (MSI) de Intel.

Intel asignó al recientemente contratado Marcian Hoff, el empleado número 12, para actuar como enlace entre las dos empresas. A fines de junio, tres ingenieros de Busicom, Masatoshi Shima y sus colegas Masuda y Takayama, viajaron a Intel para presentar el diseño. Aunque solo se le había asignado la función de enlace con los ingenieros, Hoff comenzó a estudiar el concepto. Su propuesta inicial tenía siete circuitos integrados, control de programa, unidad aritmética (ALU), temporización, ROM de programa, registros de desplazamiento para memoria temporal, controlador de impresora y control de entrada/salida.

A Hoff le preocupaba que la cantidad de chips y las interconexiones requeridas entre ellos hicieran que los objetivos de precios de Busicom fueran imposibles de cumplir. Combinar los chips reduciría la complejidad y el costo. También le preocupaba que Intel, todavía pequeño, no tuviera suficiente personal de diseño para fabricar siete chips separados al mismo tiempo. Expresó estas preocupaciones a la alta dirección, y Bob Noyce, el director ejecutivo, le dijo a Hoff que apoyaría un enfoque diferente si le pareciera factible.

Diseño simplificado

Un concepto clave en el diseño de Busicom fue que el programa de control y ALU no estaban dirigidos específicamente al mercado de las calculadoras, era el programa en ROM el que la convertía en una calculadora. La idea original era que la empresa pudiera usar los mismos chips con diferentes cantidades de RAM de registro de desplazamiento y ROM de programa para producir una gama de máquinas calculadoras. A Hoff le llamó la atención lo cerca que la arquitectura del conjunto de instrucciones de Busicom coincidía con la de las computadoras de propósito general. Empezó a considerar si se podía fabricar un verdadero procesador de propósito general lo suficientemente barato como para usarlo en una calculadora. Cuando más tarde se le preguntó de dónde había sacado las ideas para la arquitectura del primer microprocesador, Hoff relató que Plessey, 'una compañía británica de tractores', había donado una minicomputadora a Stanford, y él había 'jugado con ella'. algunos" mientras estuvo allí. Tadashi Sasaki atribuye la idea de dividir la calculadora en cuatro partes a una mujer anónima del Nara Women's College presente en una reunión de lluvia de ideas que se llevó a cabo en Japón antes de su primera reunión con Intel.

Otro desarrollo que permitió que este diseño fuera práctico fue el trabajo de Intel en los primeros chips de RAM dinámica (DRAM). Los registros de desplazamiento en ese momento se encontraban entre los únicos dispositivos de memoria de lectura y escritura de bajo costo. No permiten el acceso aleatorio; en cambio, con cada pulso de reloj mueven los datos almacenados una celda a lo largo de una cadena de celdas. El tiempo para recuperar cualquier dato dado, un byte por ejemplo, es una función de la velocidad del reloj y el número de celdas en una cadena. Si el procesador tuviera que esperar a que cada bit pasara por el registro, la velocidad efectiva resultante sería demasiado baja para ser práctica. DRAM, por otro lado, permitía el acceso aleatorio a cualquier dato que almacenaran, mientras que también tenía aproximadamente el doble de capacidad y, por lo tanto, era menos costoso.

Finalmente, Hoff notó que gran parte de la complejidad del chip de control del programa se debía a que cada instrucción se implementaba por separado. Sugirió que, en cambio, el chip admita llamadas a subrutinas y que las instrucciones se implementen como subrutinas siempre que sea posible. La aplicación sugirió naturalmente un diseño de 4 bits, ya que esto permitía la manipulación directa de los valores decimales codificados en binario (BCD) utilizados por las calculadoras. Hoff trabajó en el concepto de diseño general durante julio y agosto de 1969, pero descubrió que los ejecutivos de Busicom no parecían interesados en su propuesta.

Mazor se une

Desconocido para Hoff, el equipo de Busicom estaba muy interesado en su propuesta. Sin embargo, había una serie de cuestiones específicas que les preocupaban. Un problema clave fue que ciertas rutinas como el ajuste decimal y el manejo del teclado usarían grandes cantidades de espacio ROM si se implementaran como subrutinas. Otro fue que el diseño no presentaba ningún tipo de interrupción, por lo que sería difícil lidiar con eventos en tiempo real. Finalmente, almacenar los números como BCD de 4 bits requeriría memoria adicional para almacenar el signo y el lugar decimal.

En septiembre de 1969, Stanley Mazor se incorporó a Intel procedente de Fairchild. Hoff y Mazor propusieron rápidamente soluciones a las preocupaciones de Busicom. Para abordar la complejidad de las subrutinas, originalmente resueltas en el diseño de Busicom usando macroinstrucciones de un byte y circuitos decodificadores complejos, Mazor desarrolló un intérprete de 20 bytes de largo que ejecutaba las mismas macroinstrucciones. Shima sugirió agregar una nueva interrupción que sería activada por un pin, lo que permitiría que el teclado fuera controlado por interrupciones. También modificó la instrucción Branch Back (regreso de la subrutina) para borrar el acumulador.

Para alcanzar los objetivos de precio, era importante que el chip fuera lo más pequeño posible y utilizara la menor cantidad de clientes potenciales. Como los datos eran de 4 bits y el espacio de direcciones era de 12 bits (4096 bytes), no había forma de que el acceso directo pudiera organizarse con menos de 24 pines. Esto no era lo suficientemente pequeño, por lo que el diseño usaría un diseño de paquete en línea dual (DIP) de 16 pines y usaría multiplexación de un solo conjunto de 4 líneas. Esto significaba especificar a qué dirección en ROM acceder requería tres ciclos de reloj y otros dos para leerlo de la memoria. Funcionar a 1 MHz le permitiría realizar operaciones matemáticas en los valores BCD a aproximadamente 80 microsegundos por dígito.

El resultado de las discusiones entre Intel y Busicom fue una arquitectura que redujo el diseño de Busicom de 7 chips a una propuesta de Intel de 4 chips compuesta por CPU, ROM, RAM y dispositivos de E/S (entrada-salida). Dicha propuesta se presentó a un equipo visitante de ejecutivos de Busicom en octubre de 1969. Estuvieron de acuerdo en que el nuevo concepto era superior y dieron a Intel el visto bueno para comenzar el desarrollo. Hoff se molestó al enterarse de que el contrato asignaba todos los derechos del diseño a Busicom, a pesar de haber sido diseñado en su totalidad por Intel. Luego, el equipo se fue a Japón, pero Shima permaneció en California hasta diciembre, desarrollando muchas de las subrutinas.

Faggin se une

Ni Hoff ni Mazor, que trabajaban en el grupo de investigación de aplicaciones, tenían experiencia en el diseño del silicio real, y el grupo de diseño ya estaba sobrecargado de trabajo con el desarrollo de dispositivos de memoria. En abril de 1970, Leslie Vadász, que dirigía el grupo de diseño MOS, contrató a Federico Faggin de Fairchild Semiconductor para hacerse cargo del proyecto. Faggin ya se había hecho un nombre al liderar todo el desarrollo de la tecnología de puerta de silicio MOS y el diseño del primer circuito integrado comercial (IC) hecho con ella. La nueva tecnología iba a cambiar todo el mercado de los semiconductores.

Los circuitos integrados constan de una serie de componentes individuales, como transistores y resistencias, que se producen mezclando el silicio subyacente con "dopantes". Esto normalmente se logra calentando el chip en presencia de un gas químico, que se difunde en la superficie. Anteriormente, los componentes individuales se conectaban entre sí para formar un circuito usando alambres de aluminio depositados en la superficie. Como el aluminio se funde a 600 grados y el silicio a 1000, las trazas normalmente tenían que depositarse como último paso, lo que a menudo complicaba el ciclo de producción.

En 1967, Bell Labs publicó un artículo sobre la fabricación de transistores MOS con puertas autoalineadas hechas de silicio en lugar de metal. Sin embargo, estos dispositivos eran una prueba de concepto y no podían usarse para fabricar circuitos integrados. Faggin y Tom Klein tomaron lo que era una curiosidad y desarrollaron toda la tecnología de proceso necesaria para fabricar circuitos integrados confiables. Faggin también diseñó y produjo el Fairchild 3708, el primer circuito integrado fabricado con SGT, vendido por primera vez a fines de 1968 y que apareció en la portada de Electronics (29 de septiembre de 1969). en 1968. La tecnología de puerta de silicio también redujo la corriente de fuga en más de 100 veces, haciendo posibles circuitos dinámicos sofisticados como DRAM (memorias dinámicas de acceso aleatorio). También permitió que el silicio altamente dopado utilizado para las puertas formara las interconexiones, mejorando en gran medida la densidad del circuito de los circuitos integrados de lógica aleatoria como los microprocesadores.

Esta técnica significaba que las interconexiones podían realizarse en cualquier momento del proceso. Más importante aún, el cableado se depositó utilizando el mismo equipo que hizo el resto de los componentes. Esto significó que se eliminaron las ligeras diferencias en el diseño entre los diferentes tipos de máquinas. Anteriormente, las interconexiones tenían que ser mucho más grandes de lo necesario para garantizar que el aluminio tocara los componentes de silicio que se desplazarían debido a imprecisiones en la maquinaria. Con este problema eliminado, los circuitos podrían colocarse mucho más juntos, duplicando inmediatamente la densidad de los componentes y, por lo tanto, reduciendo su costo en la misma cantidad. Además, el cableado de aluminio actuaba como condensadores que limitaban la velocidad de la señal; eliminarlos permitió que los chips funcionaran a velocidades más rápidas.

En Intel, Faggin comenzó el diseño del nuevo procesador utilizando este proceso de compuerta autoalineada. Solo unos días después de que Faggin se uniera a la empresa Intel, Shima llegó de Japón. Se sintió decepcionado al enterarse de que no se había realizado ningún trabajo en el proyecto desde que se fue en diciembre, y expresó su preocupación porque el cronograma original ahora era imposible. Faggin respondió trabajando hasta bien entrada la noche todos los días, y Shima se quedó otros seis meses para ayudar. Fueron necesarios avances adicionales para alcanzar la densidad de circuito requerida. Uno de estos avances fue el uso de "contactos enterrados" eso permitió que los cables de conexión de silicio se conectaran directamente a los componentes. Otro fue descubrir cómo hacer que agregar "cargas de arranque" con puerta de silicio como parte de uno de los pasos de enmascaramiento, eliminando un paso del procesamiento. Sin estas dos innovaciones de Faggin, la arquitectura de Hoff no podría haberse realizado en un solo chip.

En producción

El esquema de nombres de chips de Intel en ese momento usaba un número de cuatro dígitos para cada componente. El primer dígito indicaba la tecnología de proceso utilizada, el segundo dígito indicaba la función genérica y los dos últimos dígitos especificaban el número secuencial en el desarrollo de ese tipo de componente. Usando esta convención, los chips se habrían conocido como 1302, 1105, 1507 y 1202. Faggin sintió que esto oscurecería el hecho de que formaban un conjunto coherente y decidió nombrarlos como la "familia 4000".;. Los cuatro chips eran los siguientes: la ROM 4001 de 256 bytes y 4 bits; el 4002, DRAM con cuatro registros de 20 nibbles; el 4003, E/S con un registro de desplazamiento estático de 10 bits con salidas en serie y en paralelo; y la CPU 4004. Un sistema completamente expandido podría admitir 16 4001's para un total de 4 kB de ROM, 16 4002's para un total de 1280 nibbles (640) bytes de RAM y un número ilimitado de 4003's. Los 4003 se conectaron a pines de entrada y salida programables en el 4001 y a pines de salida en el 4002, no directamente a la CPU.

Con el diseño completo, Shima regresó a Japón para comenzar a construir un prototipo de la calculadora. Las primeras obleas del 4001 se procesaron en octubre de 1970, seguidas por el 4003 y el 4002 en noviembre. El 4002 demostró tener un problema menor que se corrigió fácilmente. Los primeros 4004 llegaron a fines de diciembre y no funcionaban en absoluto. Al probar el chip, Faggin descubrió que el paso de fabricación de contactos enterrados se había omitido. Se fabricó una segunda carrera en enero de 1971 y el 4004 funcionó perfectamente excepto por dos problemas menores.

Faggin estaba enviando muestras de estos chips a Shima a medida que llegaban. En abril, supieron que el prototipo de la calculadora estaba operativo. Más tarde ese mes, Shima envió a Intel las máscaras finales para las ROM 4001, el diseño ahora estaba completo. Consistía en un 4004, dos 4002, tres 4003 y cuatro chips 4001. Un 4001 adicional suministró la función de raíz cuadrada opcional. Se agregó un cambio final después de que Faggin encontrara un problema frustrante en el 4001 que solo ocurría cuando los chips estaban calientes. Agregar un nuevo circuito decodificador de registro fue la solución de Faggin. El mismo problema también se vio en el 4002 y se utilizó la misma solución. La producción comenzó en cantidad en agosto de 1971.

Comercialización del 4004

Durante una llamada a Shima, Faggin se enteró de que Busicom tenía dificultades financieras y probablemente fracasaría si no se reducía el precio del chip. Faggin luego convenció a Noyce de que bajara el precio a cambio de liberar a Intel del acuerdo de exclusividad. En mayo de 1971, Busicom accedió a esto, con la condición de que no se usara para ningún otro proyecto de calculadora y que Intel pagara sus costos de desarrollo de $ 60,000. Con este cambio de enfoque de marketing, el nombre de la familia de chips se cambió a MCS-4, abreviatura de Micro Computer System, de 4 bits.

La gerencia de Intel se mostró escéptica de que su equipo de ventas pudiera explicar el producto a sus clientes. Como Intel ahora tenía éxito en el mercado de la memoria, les preocupaba que el 4004 pudiera confundir al mercado y dudaban en anunciarlo. Temían que los clientes actuales de Intel pudieran ver el nuevo producto como competencia y, en cambio, compraran memoria de la competencia. A Hoff y Mazor también les preocupaba que las limitaciones del diseño lo hicieran menos interesante para los usuarios que estaban acostumbrados a las nuevas minicomputadoras de 16 bits que ingresaban al mercado en ese momento.

Todo esto cambió en el verano de 1971, cuando Ed Gelbach, antes de Texas Instruments, se hizo cargo del departamento de marketing e inmediatamente comenzó a planear anunciar públicamente el producto. Esto tuvo lugar en noviembre de 1971 cuando Intel publicó anuncios "Anunciando una nueva era de electrónica integrada" apareciendo por primera vez en la edición del 15 de noviembre de Electronic News.

La 8008

(feminine)El 4004 se convirtió en el primer microprocesador comercial disponible para uso general. Este casi no fue el caso.

En diciembre de 1969, Computer Terminal Corporation (CTC) se acercó a Intel para producir un chip de memoria bipolar personalizado para una terminal de computadora que estaban diseñando, el Datapoint 2200. Mazor y Hoff consideraron el diseño de su CPU y concluyeron que no era mucho más complicado que el 4004, y que podría implementarse como una CPU de 8 bits de un solo chip. Unas semanas antes de contratar a Faggin, en marzo de 1970, Intel contrató a Hal Feeney para diseñar el 8008, en ese momento llamado 1201 siguiendo la convención de nombres de Intel. Sin embargo, CTC decidió proceder inicialmente con una implementación TTL convencional de su CPU y se redujo la prioridad del proyecto. Feeney fue asignado a otros proyectos y finalmente terminó ayudando a Faggin a probar los chips de la familia 4000.

En enero de 1971, Feeney fue reasignado al 1201 bajo la supervisión de Faggin y los chips de producción estuvieron disponibles en marzo de 1972. En mayo, Hoff y Mazor realizaron una gira de conferencias para presentar los dos diseños de CPU en los EE. UU. Las compensaciones entre los dos diseños fueron que con el 4004 y su memoria y chips de E/S era mucho más fácil construir un sistema informático completo, mientras que el 8008 era más flexible, tenía un espacio de direcciones de 16 kB más grande y ofrecía más instrucciones. Una diferencia significativa es que mientras que un sistema 4004 mínimo podría construirse usando solo dos chips, uno 4004 y otro 4001 (ROM de 256 bytes), el 8008 requeriría al menos 20 componentes TTL adicionales para interactuar con la memoria y las funciones de E/S.

Los dos diseños se usaron en diferentes roles. El 4004 se usó donde el costo de implementación era la principal preocupación y se usó ampliamente en controladores integrados para aplicaciones como hornos de microondas o semáforos y funciones similares. En cambio, el 8008 se utilizó principalmente en aplicaciones programables por el usuario, como terminales de computadora, microcomputadoras y funciones similares. Esta división en la funcionalidad permanece hasta el día de hoy, y el primero se conoce como microcontrolador.

Chips de CPU contemporáneos

Otros tres diseños de chips de CPU se produjeron aproximadamente al mismo tiempo: el Four-Phase Systems AL1, realizado en 1969; el MP944, completado en 1970 y utilizado en el avión de combate F-14 Tomcat; y el chip Texas Instruments TMS-0100, anunciado el 17 de septiembre de 1971. El MP944 era una colección de seis chips que formaban una sola unidad de procesador. El chip TMS0100 se presentó como una "calculadora en un chip" con la designación original TMS1802NC. Este chip contiene una CPU muy primitiva y solo se puede usar para implementar varias calculadoras simples de cuatro funciones. Es el precursor del TMS1000, introducido en 1974, que se considera el primer microcontrolador, es decir, una computadora en un chip que contiene no solo la CPU, sino también las funciones de ROM, RAM y E/S. La familia de cuatro chips MCS-4 desarrollada por Intel, de los cuales el 4004 es la CPU o el microprocesador, era mucho más versátil y potente que el TMS1000 de un solo chip, lo que permitía la creación de una variedad de computadoras pequeñas para diversas aplicaciones.

Zilog, la primera empresa dedicada por completo a los microprocesadores y microcontroladores, fue iniciada por Federico Faggin y Ralph Ungermann a fines de 1974.

Nota: Si la palabra "microprocesador" se usa para especificar una CPU de propósito general integrada en un solo chip, ninguno de los llamados chips de microprocesador que existían antes del 4004 merece ese nombre.

Descripción

El 4004 emplea una tecnología pMOS de carga mejorada de puerta de silicio de proceso de 10 μm en un troquel de 12 mm2 y puede ejecutar aproximadamente 92000 instrucciones por segundo; un solo ciclo de instrucción es 10,8 microsegundos. El objetivo original del diseño de frecuencia de reloj era 1 MHz, el mismo que el IBM 1620 Model I.

El Intel 4004 se fabricó con máscaras producidas cortando físicamente cada patrón con un aumento de 500x en una hoja grande de Rubylith, fotoreduciéndolo y repitiéndolo, un proceso que quedó obsoleto debido a las capacidades actuales de diseño gráfico por computadora.

Con el fin de probar los chips producidos, Faggin desarrolló un probador para obleas de silicio de la familia MCS-4 que a su vez estaba impulsado por un chip 4004. El probador también sirvió como prueba para la administración de que el microprocesador Intel 4004 podría usarse no solo en productos similares a calculadoras, sino también para aplicaciones de control.

El 4004 incluye funciones para el control directo de bajo nivel de selección de chip de memoria y E/S, que normalmente no maneja el microprocesador; sin embargo, su funcionalidad está limitada en el sentido de que no puede ejecutar código desde la RAM y está limitada a cualquier instrucción que se proporcione en la ROM (o una RAM cargada de forma independiente que funcione como ROM; en cualquier caso, el procesador no puede escribir o transferir datos en un espacio de memoria ejecutable). Los chips de partes de RAM y ROM también son inusuales en su integración de funciones de E/S junto con su función de memoria principal. esta partición redujo significativamente el recuento mínimo de piezas en un sistema MCS-4, pero requirió la inclusión de una cierta cantidad de lógica similar a un procesador en los propios chips de memoria para aceptar, decodificar y ejecutar instrucciones de transferencia de datos de nivel relativamente alto.

La disposición estándar para un sistema 4004 es de hasta 16 chips de ROM 4001 × (en un solo banco) y 16 chips de RAM × 4002 (en cuatro bancos de cuatro), que juntos proporcionan el almacenamiento de programa de 4 KB, 1024 + 256 nibbles de almacenamiento de datos/estado, más 64 líneas de control/datos externos de salida y 64 de entrada/salida (que se pueden usar para operar, por ejemplo, un 4003). Sin embargo, la documentación del MCS-4 de Intel afirma que hasta 48 chips de ROM y RAM (que proporcionan hasta 192 líneas de control externo) 'en cualquier combinación' se puede conectar al 4004 "con hardware de activación simple", pero se niega a dar más detalles o ejemplos de cómo se lograría realmente.

Especificaciones técnicas

- La velocidad máxima del reloj es de 740 kHz. El 4004 tenía esta calificación máxima del reloj en su lanzamiento inicial de 1971.

- Tiempo de ciclo de instrucción: mínimo 10.8 μs (8 ciclos de reloj por ciclo de máquina).

- Tiempo de ejecución de instrucciones 1 o 2 ciclos de máquina (10.8 o 21.6 μs), 46250 a 92500 instrucciones por segundo.

- Añadiendo dos números decimales de 8 dígitos (32 bits cada uno, asumiendo dígitos BCD de 4 bits) toma un reclamado 850 μs, o aproximadamente 79 ciclos de máquinas (632 relojes), por un promedio de apenas menos de 10 ciclos (80 garrapatas) por par de dígitos y una velocidad de funcionamiento de 1176 × 8 dígitos adiciones por segundo

- Programa separado y almacenamiento de datos. Contrariamente a los diseños de arquitectura de Harvard, sin embargo, que utilizan autobuses separados, el 4004, con su necesidad de mantener la cuenta de pin, utiliza un solo bus de 4 bits múltiple para transferir:

- Dirección de 12 bits,

- Instrucciones de 8 bits,

- Palabras de datos de 4 bits.

- Able to directly address 5120 bits (equivallent to 640 bytes) of RAM, stored as 1280 4-bit "characters" and organized into groups representing 1024 "data" and 256 "status" characters (512 and 128 bytes).

- Able to directly address 32768 bits de ROM, equivalente y arreglado como 4096 palabras de 8 bits (es decir, bytes).

- El conjunto de instrucciones contenía 46 instrucciones (de las cuales 41 eran 8 bits de ancho y 5 eran 16 bits de ancho).

- Registro conjunto contiene 16 registros de 4 bits cada uno.

- Apilación interna de subrutina, 3 niveles de profundidad.

Niveles lógicos

| Signatura | Min. | Max |

|---|---|---|

| VSS-DD | +15 V - 5% | +15 V + 5% |

| VIL | VDD | VSS 5,5 V |

| VIH | VSS, 1.5 V | VSS + 0,3 V |

| VOL | VSS 12 - V | VSS − 6,5 V |

| VOh. | VSS, 0,5 V | VSS |

Fichas de apoyo

- 4001: 256 bytes ROM (256 8-bit programa instrucciones) y un puerto I/O integrado de 4 bits. Un chip ROM+I/O 4001 no se puede utilizar en un sistema junto con un par 4008/4009.

- 4002: RAM de 40 bytes (80 de 4 bits datos palabras) y un puerto de salida integrado de 4 bits; la parte RAM del chip se organiza en 4 "registros" de 20 palabras de 4 bits:

- 16 palabras de datos (utilizadas para dígitos de mantissa en el diseño original de la calculadora), accedidas de manera relativamente estándar,

- 4 palabras de estado (utilizadas para dígitos exponentes y signos en el diseño original de la calculadora), accedieron a través de comandos tipo I/O en lugar del canal de entrada del ROM.

- 4003: Registro de cambios de salida paralelo de 10 bits para escanear teclados, pantallas, impresoras, etc.

- 4008: cierre de 8 bits de dirección para el acceso a chips de memoria estándar y un puerto de 4 bits integrado e I/O.

- 4009: programa y convertidor de acceso I/O a la memoria estándar y chips I/O.

- 4269: interfaz teclado/display.

- 4289: interfaz de memoria (funciones combinadas de 4008 y 4009).

La especificación mínima del sistema descrita por Intel consiste en un 4004 con una sola ROM de programa 4001 de 256 bytes; no hay una necesidad explícita de RAM separada en aplicaciones de complejidad mínima gracias a la gran cantidad de registros de índice integrados del 4004, que representan el equivalente a 16 caracteres de 4 bits u 8 caracteres de 8 bits (o una combinación) de RAM en funcionamiento, ni para chips de interfaz simples gracias a las líneas de E/S integradas de la ROM. Sin embargo, a medida que aumenta la complejidad del proyecto, los otros chips de soporte comienzan a ser útiles.

Embalaje

Se produjeron numerosas versiones de la línea de procesadores Intel MCS-4. Las primeras versiones, marcadas con C (como C4004), eran de cerámica y usaban un patrón de cebra de blanco y gris en la parte posterior de las fichas, a menudo llamados "trazos grises". La próxima generación de chips fue de cerámica blanca simple (también marcada con C), y luego de cerámica gris oscuro (D). Muchas de las versiones más recientes de la familia MCS-4 también se fabricaron con plástico (P).

Usar

El primer producto comercial que usó un microprocesador fue la calculadora Busicom 141-PF. El 4004 también se utilizó en el primer juego de pinball controlado por microprocesador, un prototipo producido por Dave Nutting Associates para Bally en 1974.

En 1996, la Oficina de Patentes de EE. UU. reconoció oficialmente al Sr. Gary W. Boone y su empleador, Texas Instruments, como los inventores del microcontrolador de un solo chip, anulando la concesión de la patente a Gilbert P. Hyatt en 1990. Aunque la la patente había expirado, se pensó que podría tener un impacto financiero potencial según los detalles de los contratos anteriores con Gilbert Hyatt. Según Nick Tredennick, diseñador de microprocesadores y testigo experto en el caso de la patente de Boone/Hyatt:

Aquí están mis opiniones de [el] estudio [he realizado para el caso de patente]. El primer microprocesador en un producto comercial fue el Four Phase Systems AL1. El primer microprocesador comercialmente disponible (vendido como componente) fue el 4004 de Intel.

Un mito popular dice que la Pioneer 10, la primera nave espacial que abandonó el sistema solar, utilizó un microprocesador Intel 4004. Según el Dr. Larry Lasher del Ames Research Center, el equipo de Pioneer evaluó el 4004, pero decidió que era demasiado nuevo en ese momento para incluirlo en cualquiera de los proyectos de Pioneer. El mito fue repetido por el propio Federico Faggin en una conferencia para el Computer History Museum en 2006.

Legado y valor

Federico Faggin firmó el 4004 con sus iniciales porque sabía que su diseño de puerta de silicio encarnaba "la esencia del microprocesador". Una esquina del dado dice "F.F."

El 15 de noviembre de 2006, el 35.° aniversario del 4004, Intel celebró el lanzamiento de los esquemas, la máscara y el manual del usuario del chip. Se construyó una réplica completamente funcional de 41 × 58 cm y 130 × escala del Intel 4004 utilizando transistores discretos y se exhibió en 2006 en el Museo Intel en Santa Clara, California.

El 15 de octubre de 2010, el presidente Barack Obama otorgó a Faggin, Hoff y Mazor la Medalla Nacional de Tecnología e Innovación por su trabajo pionero en el 4004.

Documentos históricos

Los primeros documentos sobre la tecnología de puerta de silicio MOS para circuitos integrados que permitieron el 4004

Contenido relacionado

Cátodo frío

Subaru Forester

Motor fuera de borda