IBM 7030 estiramiento

La IBM 7030, también conocida como Stretch, fue la primera supercomputadora transistorizada de IBM. Fue la computadora más rápida del mundo desde 1961 hasta que el primer CDC 6600 entró en funcionamiento en 1964.

Diseñado originalmente para cumplir con un requisito formulado por Edward Teller en el Laboratorio Nacional Lawrence Livermore, el primer ejemplo se entregó al Laboratorio Nacional de Los Álamos en 1961 y una segunda versión personalizada, el IBM 7950 Harvest, a la Agencia de Seguridad Nacional en 1962 El Stretch en el Establecimiento de Investigación de Armas Atómicas en Aldermaston, Inglaterra, fue muy utilizado por los investigadores allí y en AERE Harwell, pero solo después del desarrollo del S2 Fortran Compiler, que fue el primero en agregar matrices dinámicas y que luego se transfirió al Ferranti Atlas del Atlas Computer Laboratory en Chilton.

El 7030 fue mucho más lento de lo esperado y no cumplió con sus agresivos objetivos de rendimiento. IBM se vio obligada a bajar su precio de $ 13,5 millones a solo $ 7,78 millones y retiró el 7030 de las ventas a clientes más allá de los que ya habían negociado contratos. La revista PC World nombró a Stretch como uno de los mayores fracasos de gestión de proyectos en la historia de TI.

Dentro de IBM, ser eclipsado por la más pequeña Control Data Corporation parecía difícil de aceptar. El líder del proyecto, Stephen W. Dunwell, se convirtió inicialmente en el chivo expiatorio de su papel en el 'fracaso', pero cuando el éxito de IBM System/360 se hizo evidente, recibió una disculpa oficial y, en 1966, se le nombró miembro de IBM.

A pesar de que Stretch no cumplió con sus propios objetivos de rendimiento, sirvió como base para muchas de las características de diseño del exitoso IBM System/360, que se anunció en 1964 y se envió por primera vez en 1965.

Historial de desarrollo

A principios de 1955, el Dr. Edward Teller del Laboratorio de Radiación de la Universidad de California quería un nuevo sistema informático científico para cálculos hidrodinámicos tridimensionales. Se solicitaron propuestas de IBM y UNIVAC para este nuevo sistema, que se llamará Calculadora de reacción automática de Livermore o LARC. Según el ejecutivo de IBM, Cuthbert Hurd, dicho sistema costaría aproximadamente 2,5 millones de dólares y funcionaría con uno o dos MIPS. La entrega debía ser de dos a tres años después de la firma del contrato.

En IBM, un pequeño equipo de Poughkeepsie, que incluía a John Griffith y Gene Amdahl, trabajó en la propuesta de diseño. Justo después de que terminaron y estaban a punto de presentar la propuesta, Ralph Palmer los detuvo y les dijo: 'Es un error'. El diseño propuesto se habría construido con transistores de contacto puntual o transistores de barrera de superficie, ambos probablemente pronto serían superados por el transistor de difusión recién inventado.

IBM volvió a Livermore y declaró que se rescindía del contrato y, en su lugar, propuso un sistema mucho mejor: "No vamos a construir esa máquina para usted; queremos construir algo mejor! No sabemos con precisión cuánto se necesitará, pero creemos que será otro millón de dólares y otro año, y no sabemos qué tan rápido funcionará, pero nos gustaría apuntar a diez millones de instrucciones por segundo." Livermore no quedó impresionado y, en mayo de 1955, anunciaron que UNIVAC había ganado el contrato LARC, ahora llamado Computadora automática de investigación de Livermore. LARC finalmente se entregaría en junio de 1960.

En septiembre de 1955, temiendo que el Laboratorio Nacional de Los Álamos también ordenara un LARC, IBM presentó una propuesta preliminar para una computadora binaria de alto rendimiento basada en la versión mejorada del diseño que Livermore había rechazado, que recibieron con interés. En enero de 1956, se inició formalmente el Proyecto Stretch. En noviembre de 1956, IBM ganó el contrato con el objetivo de rendimiento agresivo de una "velocidad de al menos 100 veces la IBM 704" (es decir, 4 MIPS). La entrega estaba prevista para 1960.

Durante el diseño, resultó necesario reducir las velocidades del reloj, lo que dejó en claro que Stretch no podía cumplir con sus agresivos objetivos de rendimiento, pero las estimaciones de rendimiento oscilaron entre 60 y 100 veces el IBM 704. En 1960, el precio de $ 13,5 millones se estableció para el IBM 7030. En 1961, los puntos de referencia reales indicaron que el rendimiento del IBM 7030 era solo unas 30 veces el del IBM 704 (es decir, 1,2 MIPS), lo que provocó una vergüenza considerable para IBM. En mayo de 1961, Thomas J. Watson Jr. anunció una reducción del precio de todos los 7030 en negociación a 7,78 millones de dólares y la retirada inmediata del producto de futuras ventas.

Su tiempo de adición de coma flotante es de 1,38 a 1,50 microsegundos, el tiempo de multiplicación es de 2,48 a 2,70 microsegundos y el tiempo de división es de 9,00 a 9,90 microsegundos.

Impacto técnico

Si bien el IBM 7030 no se consideró exitoso, generó muchas tecnologías incorporadas en futuras máquinas que tuvieron mucho éxito. La lógica de transistores Standard Modular System fue la base de la línea de computadoras científicas IBM 7090, las computadoras comerciales IBM 7070 y 7080, las líneas IBM 7040 e IBM 1400 y la pequeña computadora científica IBM 1620; el 7030 usó alrededor de 170,000 transistores. Las unidades IBM 7302 Model I Core Storage también se utilizaron en IBM 7090, IBM 7070 e IBM 7080. Multiprogramación, protección de memoria, interrupciones generalizadas, el byte de ocho bits para E/S fueron todos los conceptos incorporados más tarde en la línea de computadoras IBM System / 360, así como en la mayoría de las unidades centrales de procesamiento (CPU) posteriores.

Stephen Dunwell, el gerente de proyecto que se convirtió en el chivo expiatorio cuando Stretch fracasó comercialmente, señaló poco después del fenomenalmente exitoso lanzamiento de System/360 en 1964 que la mayoría de sus conceptos centrales fueron iniciados por Stretch. En 1966 recibió una disculpa y fue nombrado miembro de IBM, un gran honor que conllevaba recursos y autoridad para llevar a cabo la investigación deseada.

En diseños posteriores de supercomputadoras, como IBM System/360 Models 91, 95 y 195, y la serie IBM 3090, así como en computadoras de otros fabricantes, se usaron canalización de instrucciones, captación previa y decodificación, e intercalación de memoria. A partir de 2021, estas técnicas todavía se utilizan en la mayoría de los microprocesadores avanzados, comenzando con la generación de la década de 1990 que incluía Intel Pentium y Motorola/IBM PowerPC, así como en muchos microprocesadores y microcontroladores integrados de varios fabricantes.

Implementación de hardware

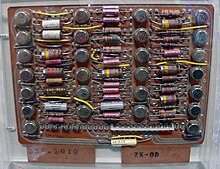

La CPU 7030 utiliza lógica acoplada por emisor (originalmente llamada lógica de dirección de corriente) en 18 tipos de tarjetas de sistema modular estándar (SMS). Utiliza 4.025 tarjetas dobles (como se muestra) y 18.747 tarjetas individuales, con 169.100 transistores, que requieren una potencia total de 21 kW. Utiliza transistores de deriva de germanio NPN y PNP de alta velocidad, con una frecuencia de corte de más de 100 MHz y utiliza ~50 mW cada uno. Algunos circuitos de tercer nivel utilizan un tercer nivel de voltaje. Cada nivel lógico tiene un retraso de unos 20 ns. Para ganar velocidad en áreas críticas, se utiliza la lógica emisor-seguidor para reducir el retardo a unos 10 ns.

Utiliza la misma memoria central que el IBM 7090.

Instalaciones

- Laboratorio Científico de Los Álamos (LASL) en abril de 1961, aceptado en mayo de 1961, y utilizado hasta el 21 de junio de 1971.

- Lawrence Livermore National Laboratory, Livermore, California, entregó noviembre de 1961.

- U.S. National Security Agency in February 1962 as the main CPU of the IBM 7950 Harvest system, used until 1976, when the IBM 7955 Tractor tape system developed problems due to wearing cams that could not be replaced.

- Atomic Weapons Establishment, Aldermaston, England, delivered February 1962

- U.S. Weather Bureau Washington D.C., entregó junio/julio 1962.

- MITRE Corporation, entregada en diciembre de 1962. y utilizado hasta agosto de 1971. En la primavera de 1972, fue vendida a la Universidad Brigham Young, donde fue utilizada por el departamento de física hasta que fue desechada en 1982.

- US Navy Dahlgren Naval Proving Ground, delivered Sep/Oct 1962.

- Commissariat à l'énergie atomique, Francia, entregó noviembre de 1963.

- IBM.

El IBM 7030 del Laboratorio Lawrence Livermore (excepto su memoria central) y partes del IBM 7030 de MITRE Corporation/Brigham Young University ahora residen en la colección del Computer History Museum, en Mountain View, California.

Arquitectura

Formatos de datos

- Los números de puntos fijos son de longitud variable, almacenados en formato binario (1 a 64 bits) o decimal (1 a 16 dígitos) y ya sea en formato no firmado o formato de signo/magnitud. En formato decimal, los dígitos son bytes de longitud variable (4 a 8 bits).

- Los números de puntos flotantes tienen una bandera exponente de 1 bit, un exponente de 10 bits, un signo exponente de 1 bit, una magnitud de 48 bits y un byte de 4 bits en formato de señal/magnitud.

- Los caracteres alfabéricos son longitud variable y pueden usar cualquier código de caracteres de 8 bits o menos.

- Los bytes son longitud variable (1 a 8 bits).

Formato de instrucción

Las instrucciones son de 32 bits o de 64 bits.

Registros

Los registros superponen las primeras 32 direcciones de memoria como se muestra.

| ! Dirección | Mnemonic | Registro | Almacenado en: |

|---|---|---|---|

| 0 | $Z | 64-bit cero: siempre se lee como cero, no se puede cambiar por escritos | Almacenamiento básico principal |

| 1 | $IT | temporizador de intervalos (bits 0..18): decrementado a 1024 Hz, recicla alrededor de cada 8,5 minutos, a cero gira en el "indicador de señal de tiempo" en el registro del indicador | Almacenamiento básico del índice |

| $TC | reloj de 36 bits (bits 28..63): conteo de 1024 Hz garrapatas, bits 38..63 aumento una vez por segundo, recicla cada ~777 días. | ||

| 2 | $IA | Dirección de interrupción de 18 bits | Almacenamiento básico principal |

| 3 | $UB | Dirección superior de 18 bits (bits 0-17) | Registro de transistores |

| $LB | Dirección inferior de 18 bits (bits 32-49) | ||

| Control de límites de 1 bit (bit 57): determina si las direcciones dentro o fuera de los límites están protegidas | |||

| 4 | bits de mantenimiento de 64 bits: solo utilizados para mantenimiento | Almacenamiento básico principal | |

| 5 | $CA | canal address (bits 12..18): readonly, set by the "exchange", an i/o processor | Registro de transistores |

| 6 | $CPUS | otros bits CPU (bits 0..18): mecanismo de señalización para un grupo de hasta 20 CPU | Registro de transistores |

| 7 | $LZC | cuenta de ceros izquierdos (bits 17..23): número de ceros principales de un resultado conectivo o operación de punto flotante | Registro de transistores |

| $AOC | todos los-ones cuentan (bits 44..50): cuenta de bits fijados en resultado conectivo o decimal múltiple o divide | ||

| 8 | $L | La mitad izquierda del acumulador de 128 bits | Registro de transistores |

| 9 | $R | La mitad derecha del acumulador de 128 bits | |

| 10 | SB | accumulator sign byte (bits 0..7) | |

| 11 | # | registro del indicador (bits 0..19) | Registro de transistores |

| 12 | $MASK | Registro de máscaras de 64 bits 0..19 siempre 1, bits 20..47 writable, bits 48..63 siempre 0 | Registro de transistores |

| 13 | $RM | Registro de 64 bits: fijado por instrucciones de división de puntos enteros y flotantes solamente | Almacenamiento básico principal |

| 14 | $FT | Registro de factores de 64 bits: cambiado sólo por la instrucción "factor de carga" | Almacenamiento básico principal |

| 15 | $TR | Registro de tránsito de 64 bits | Almacenamiento básico principal |

| 16 ... 31 | $X0 ... $X15 | Registros de índices de 64 bits (16) | Almacenamiento básico del índice |

Los registros acumulador e índice funcionan en formato de signo y magnitud.

Memoria

La memoria principal es de 16 000 a 256 000 palabras binarias de 64 bits, en bancos de 16 000.

La memoria se calentó/enfrió con aceite de inmersión para estabilizar sus características operativas.

Software

- STRETCH Assembly Program (STRAP)

- MCP (para no confundirse con el MCP Burroughs)

- Idiomas de programación COLASL y IVY

- Lenguaje de programación FORTRAN

Contenido relacionado

Crippleware

Submarino clase Los Ángeles

Protocolo de iniciación de sesión (SIP)