Hitachi 6309

El 6309 es la versión CMOS de Hitachi del microprocesador Motorola 6809, lanzado a fines de 1982. Inicialmente se comercializó como una versión de bajo consumo del 6809, sin hacer referencia a sus muchos mejoras internas.

Mientras está en "Modo de emulación" es totalmente compatible con el 6809. A las especificaciones del 6809, agrega frecuencias de reloj más altas, características mejoradas, nuevas instrucciones y registros adicionales. La mayoría de las nuevas instrucciones se agregaron para admitir registros adicionales, así como matemáticas de hasta 32 bits, división de hardware, manipulaciones de bits y transferencias de bloques. El 6309 es generalmente un 30 % más rápido en modo nativo que el 6809.

Esta información nunca fue publicada por Hitachi. El número de abril de 1988 de Oh! FM, una revista japonesa para usuarios de computadoras personales Fujitsu, contenía la primera descripción de las capacidades adicionales del 6309. Más tarde, Hirotsugu Kakugawa publicó detalles de las nuevas funciones e instrucciones del 6309 en comp.sys.m6809. Esto condujo al desarrollo de NitrOS-9 para Tandy Color Computer 3.

Modelo de programación

Diferencias con el Motorola 6809

El 6309 difiere del 6809 en varias áreas clave.

Tecnología de procesos

El 6309 está fabricado con tecnología CMOS, mientras que el 6809 es un dispositivo NMOS. Como resultado, el 6309 requiere menos energía para funcionar que el 6809.

El bajo consumo de energía también significa que se puede pausar hasta 15 ciclos, ya que no tiene que actualizar constantemente su estado interno. Esto es útil para el acceso directo a la memoria, ya que permite a los dispositivos externos pausar la CPU para liberar el bus de memoria, leer o escribir pequeñas cantidades de memoria y luego reactivar la CPU nuevamente. No se requiere otra lógica.

Es un diseño dinámico. La hoja de datos especifica una frecuencia de reloj mínima y perderá su estado cuando la velocidad del reloj sea demasiado baja.

Velocidad del reloj

El 6309 tiene versiones B (2 MHz) al igual que el 6809. Sin embargo, un "C" La clasificación de velocidad se produjo con una frecuencia de reloj máxima de 3,0 o 3,5 MHz, según la hoja de datos a la que se haga referencia. (Varias computadoras japonesas tenían CPU 63C09 sincronizadas a 3,58 MHz, la frecuencia de ráfaga de colores NTSC, por lo que la calificación de 3,5 parece ser la más probable). Los informes anecdóticos e individuales indican que la variante 63C09 se puede sincronizar a 5 MHz sin efectos nocivos. Al igual que el 6809, la CPU Hitachi viene en versiones de reloj interno y externo (HD63B/C09 y HD63B/C09E respectivamente)

Eficiencia computacional

Cuando se cambia al modo nativo 6309 (a diferencia del modo predeterminado compatible con 6809), muchas instrucciones clave se completarán en menos ciclos de reloj. Esto a menudo mejora las velocidades de ejecución hasta en un 30%.

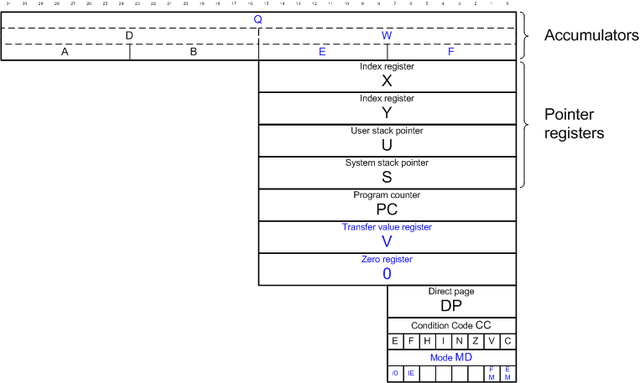

Registros adicionales

- Dos acumuladores de 8 bits: 'E' y 'F'. Estos pueden ser concatenados para formar 'W' acumulador de 16 bits. El acumulador D de 16 bits existente 6809 puede ser concatenado con W para formar un acumulador de 32 bits 'Q'. Es probable que D sea corto para 'Doble' y Q para 'Quad', el número de bytes que sostienen.

- Transfer register 'V' for inter-register instructions. Su valor no se ve afectado por un reseteo de hardware para que pueda conservar un valor constante, por lo tanto 'V'.

- 8/16-bit Cero registro '0' para acelerar las operaciones utilizando una constante cero. Este registro siempre lee cero y escribe a él son ignorados.

- Mode register 'MD', un registro secundario del Código de Estado que controla el modo operativo. Sólo 4 bits de este registro se definen.

Instrucciones adicionales

La mayoría de las instrucciones nuevas son modificaciones de instrucciones existentes para manejar la existencia de registros adicionales, como cargar, almacenar, agregar y similares. Las adiciones de Genuine 6309 incluyen aritmética entre registros, transferencias de bloques, división de hardware y manipulaciones a nivel de bits. Además, los registros D y W de 16 bits pueden ser objeto de aritmética de 16 bits con operaciones de acarreo y desplazamiento y rotación de 16 bits. En 6809, estas operaciones están limitadas a operandos de 8 bits.

A pesar de la facilidad de uso de las instrucciones adicionales, el análisis realizado por los gurús de la programación 6809 indica que muchas de las nuevas instrucciones son en realidad más lentas que el código 6809 equivalente, especialmente en bucles estrechos. Se debe realizar un análisis cuidadoso para garantizar que el programador utilice el código más eficiente para la aplicación en particular.

La mayoría de las instrucciones nuevas utilizan el código de operación de prefijo y eso las hace un ciclo más lentas en comparación con la instrucción 6809 similar. Por otro lado, el modo nativo 6309 ejecuta muchas instrucciones más rápido en uno o más ciclos. Aquí hay una comparación de tiempo de una instrucción LD de 8 bits para 'A' registrarse y 'E' registrarse en 6809 y 6309:

| instrucción | 6809 | Modo de emulación 6309 | modo nativo 6309 |

|---|---|---|---|

| LDA immediate | 2 ciclos | 2 ciclos | 2 ciclos |

| LDE immediate | n/a | 3 ciclos | 3 ciclos |

| LDA direct | 4 ciclos | 4 ciclos | 3 ciclos |

| LDE direct | n/a | 5 ciclos | 4 ciclos |

| LDA indexada | 4+ ciclos | 4+ ciclos | 4+ ciclos |

| LDE indexed | n/a | 5+ ciclos | 5+ ciclos |

| LDA extended | 5 ciclos | 5 ciclos | 4 ciclos |

| LDE extended | n/a | 6 ciclos | 5 ciclos |

También las operaciones entre registros y las nuevas operaciones de 16 bits son algo mixtas. Según el modo de direccionamiento y el modo 6309, el código 6809 equivalente puede ser más rápido. A modo de ilustración, veamos el momento de la exclusiva o la instrucción.

| instrucción | 6809 | Modo de emulación 6309 | modo nativo 6309 |

|---|---|---|---|

| EORA immediate | 2 ciclos | 2 ciclos | 2 ciclos |

| EORD immediate | n/a | 5 ciclos | 4 ciclos |

| EORA direct | 4 ciclos | 4 ciclos | 3 ciclos |

| EORD direct | n/a | 7 ciclos | 5 ciclos |

| EORA indexado | 4+ ciclos | 4+ ciclos | 4+ ciclos |

| Índice EORD | n/a | 7+ ciclos | 6+ ciclos |

| EORA extended | 5 ciclos | 5 ciclos | 4 ciclos |

| EORD extended | n/a | 8 ciclos | 6 ciclos |

| EORR interregister | n/a | 4 ciclos | 4 ciclos |

Como indica la tabla anterior, el registro D exclusivo o de 16 bits con parámetro inmediato se puede reemplazar por dos instrucciones de 8 bits EORA imm, EORB imm y se ejecutará más rápido cuando 6309 se ejecute en modo de emulación. Aunque uno debe darse cuenta de que la secuencia de instrucciones de 8 bits EORA imm, EORB imm no es el equivalente exacto de la instrucción EORD imm de 16 bits, ya que el registro CC del código de condición se establece según el resultado de la operación de 8 bits en el primer caso y según el resultado de la operación de 16 bits en el segundo. caso.

Ocurre un problema similar con la instrucción EORR entre registros. Acepta operandos de 8 y 16 bits y siempre se ejecuta en 4 ciclos. Sin embargo, para operandos de 8 bits, es más rápido usar las instrucciones EORA imm o EORB imm cuando corresponda. Además, cuando 6309 se ejecuta en modo nativo, las instrucciones EORA directa, EORB directa toman solo 3 ciclos, un ciclo menos que la operación entre registros.

Funciones de hardware adicionales

Es posible cambiar el modo de operación de la interrupción FIRQ. En lugar de apilar los registros PC y CC (comportamiento normal del 6809), la interrupción FIRQ se puede configurar para apilar todo el conjunto de registros, como lo hace la interrupción IRQ. Además, el 6309 tiene dos posibles modos de captura, uno para una búsqueda de instrucción ilegal y otro para la división por cero. La búsqueda ilegal de instrucciones no se puede enmascarar, y muchos usuarios de la computadora en color TRS-80 informaron que sus 6309 tenían errores. cuando en realidad era un indicador de características mejoradas y desconocidas.

Contenido relacionado

Kista

Telecomunicaciones en Grecia

Generación eléctrica