DEC Alfa

Alpha (nombre original Alpha AXP) es una arquitectura de conjunto de instrucciones (ISA) de computadora con conjunto de instrucciones reducido (RISC) de 64 bits desarrollada por Digital Equipment Corporation (DEC). Alpha fue diseñado para reemplazar las computadoras con conjunto de instrucciones complejas (CISC) VAX de 32 bits y para ser un procesador RISC altamente competitivo para estaciones de trabajo Unix y mercados similares.

Alpha se implementa en una serie de microprocesadores desarrollados y fabricados originalmente por DEC. Estos microprocesadores se utilizan de manera más destacada en una variedad de estaciones de trabajo y servidores DEC, que eventualmente formaron la base de casi toda su línea de escala media a alta. Varios proveedores externos también produjeron sistemas Alpha, incluidas placas base con factor de forma de PC.

Los sistemas operativos compatibles con Alpha incluyen OpenVMS (anteriormente denominado OpenVMS AXP), Tru64 UNIX (anteriormente denominado DEC OSF/1 AXP y Digital UNIX), Windows NT (descontinuado después de NT 4.0 y versión preliminar de Windows 2000 RC2), Linux (Debian, SUSE, Gentoo y Red Hat), BSD UNIX (NetBSD, OpenBSD y FreeBSD hasta 6.x), Plan 9 de Bell Labs y el kernel L4Ka::Pistachio. Se llevó a cabo un puerto de Ultrix a Alpha durante el desarrollo inicial de la arquitectura Alpha, pero nunca se lanzó como producto.

La arquitectura Alpha se vendió, junto con la mayor parte de DEC, a Compaq en 1998. Compaq, que ya era cliente de Intel x86, anunció que eliminaría Alpha a favor de la próxima arquitectura Hewlett-Packard/Intel Itanium, y vendió toda la propiedad intelectual de Alpha a Intel, en 2001, matando efectivamente el producto. Hewlett-Packard compró Compaq en 2002, continuó con el desarrollo de la línea de productos existente hasta 2004 y vendió sistemas basados en Alpha, en gran parte a la base de clientes existente, hasta abril de 2007.

Historia

PRISMA

Alpha surgió de un proyecto RISC anterior denominado Máquina de conjunto de instrucciones reducidas en paralelo (PRISM), producto de varios proyectos anteriores. PRISM estaba destinado a ser un diseño flexible, compatible con aplicaciones similares a Unix y el software VAX/VMS existente de Digital, después de una pequeña conversión. Un nuevo sistema operativo llamado MICA admitiría las interfaces ULTRIX y VAX/VMS en un kernel común, lo que permitiría que el software de ambas plataformas se transfiera fácilmente a la arquitectura PRISM.

Iniciado en 1985, el diseño de PRISM se modificó continuamente durante su desarrollo en respuesta a los cambios en el mercado de las computadoras, lo que provocó largas demoras en su introducción. No fue hasta el verano de 1987 que se decidió que sería un diseño de 64 bits, uno de los primeros diseños de este tipo en formato de microprocesador. En octubre de 1987, Sun Microsystems presentó Sun-4, su primera estación de trabajo que usaba su nuevo procesador SPARC. El Sun-4 funciona de tres a cuatro veces más rápido que sus últimos diseños de Sun-3 con el Motorola 68020 y cualquier oferta de Unix de DEC. Los planes cambiaron de nuevo; PRISM se realineó una vez más como una parte de 32 bits y se dirigió directamente al mercado de Unix. Esto retrasó aún más el diseño.

Habiendo observado que la fecha de entrega de PRISM seguía retrasándose y ante la posibilidad de más retrasos, un equipo de la oficina de Palo Alto decidió diseñar su propia estación de trabajo utilizando otro procesador RISC. Después de la diligencia debida, seleccionaron el MIPS R2000 y construyeron una estación de trabajo que funcionaba con Ultrix en un período de 90 días. Esto provocó un enconado debate dentro de la empresa, que llegó a un punto crítico en una reunión de gestión de julio de 1988. PRISM parecía ser más rápido que el R2000, pero las máquinas R2000 podrían estar en el mercado en enero de 1989, un año antes que PRISM. Cuando se aceptó esta propuesta, una de las dos funciones originales de PRISM desapareció. La decisión de hacer un VMS PRISM ya había terminado en este punto, por lo que no quedaba ningún rol. PRISM fue cancelado en la reunión.

RISCY VAX

Cuando terminó la reunión, Ken Olsen se acercó a Bob Supnik y dijo que los chips RISC parecían ser una amenaza futura para su línea VAX. Le pidió a Supnik que considerara qué se podría hacer con VAX para mantenerlo competitivo con los futuros sistemas RISC.

Esto llevó a la formación de "RISCy VAX" equipo. Inicialmente consideraron tres conceptos. Una era una versión reducida de la arquitectura del conjunto de instrucciones (ISA) de VAX que se ejecutaría en un sistema similar a RISC y dejaría instrucciones VAX más complejas para las subrutinas del sistema. Otro concepto era un sistema RISC puro que traduciría el código VAX existente en su propio ISA sobre la marcha y lo almacenaría en una memoria caché de la CPU. Finalmente, todavía existía la posibilidad de un procesador CISC mucho más rápido que ejecutara el VAX ISA completo. Desafortunadamente, todos estos enfoques introdujeron una sobrecarga y no serían competitivos con una máquina RISC pura que ejecuta código RISC nativo.

Luego, el grupo consideró sistemas híbridos que combinaran una de sus soluciones de un chip VAX existentes y un chip RISC como coprocesador utilizado para necesidades de alto rendimiento. Estos estudios sugirieron que el sistema inevitablemente se vería obstaculizado por la parte de menor rendimiento y no ofrecería ninguna ventaja convincente. Fue en este punto que Nancy Kronenberg señaló que las personas ejecutaban VMS, no VAX, y que VMS solo tenía algunas dependencias de hardware basadas en su modelado de interrupciones y paginación de memoria. No parecía haber ninguna razón convincente por la que VMS no pudiera ser portado a un chip RISC siempre que se conservaran estos pequeños fragmentos del modelo. El trabajo adicional sobre este concepto sugirió que este era un enfoque viable.

Supnik llevó el informe resultante al Grupo de trabajo de estrategia en febrero de 1989. Se plantearon dos preguntas: ¿podría el diseño RISC resultante ser también un líder en rendimiento en el mercado de Unix y debería la máquina ser un estándar abierto? Y con eso, se tomó la decisión de adoptar la arquitectura PRISM con las modificaciones apropiadas. Esto se convirtió en el "EVAX" concepto, una continuación de la implementación exitosa de CMOS CVAX. Cuando la gerencia aceptó los hallazgos, decidió darle al proyecto un nombre más neutral, eliminando "VAX" y finalmente decidiéndose por Alpha. Poco después, se comenzó a trabajar en un puerto de VMS a la nueva arquitectura.

Alfa

El nuevo diseño utiliza la mayoría de los conceptos básicos de PRISM, pero se reajustó para permitir que los programas VMS y VMS se ejecuten a una velocidad razonable sin ninguna conversión. Los principales arquitectos del conjunto de instrucciones Alpha fueron Richard L. Sites y Richard T. Witek. El Epicode de PRISM se convirtió en el PALcode de Alpha, lo que proporciona una interfaz abstracta para las funciones específicas de implementación de la plataforma y el procesador.

La principal contribución de Alpha a la industria de los microprocesadores, y la principal razón de su desempeño, no es tanto la arquitectura sino su implementación. En ese momento (como lo es ahora), la industria de los microchips estaba dominada por herramientas de diseño y diseño automatizadas. Los diseñadores de chips de Digital continuaron con el diseño de circuitos manuales sofisticados para lidiar con la compleja arquitectura VAX. Los chips Alpha muestran que el diseño manual de circuitos aplicado a una arquitectura más simple y limpia permite frecuencias operativas mucho más altas que las que son posibles con los sistemas de diseño más automatizados. Estos chips provocaron un renacimiento del diseño de circuitos personalizados dentro de la comunidad de diseño de microprocesadores.

Originalmente, los procesadores Alpha se designaron como la serie DECchip 21x64, con "DECchip" reemplazado a mediados de la década de 1990 con "Alpha". Los dos primeros dígitos, "21" significa el siglo XXI, y los dos últimos dígitos, "64" significa 64 bits. El Alpha fue diseñado como 64 bits desde el principio y no hay una versión de 32 bits. El dígito del medio corresponde a la generación de la arquitectura Alpha. Internamente, los procesadores Alpha también fueron identificados por números EV, EV significa oficialmente "VAX extendido" pero con un significado humorístico alternativo de "Electric Vlasic", que rinde homenaje al experimento Electric Pickle en Western Research Lab.

En mayo de 1997, DEC demandó a Intel por presuntamente infringir sus patentes Alpha al diseñar los chips Pentium, Pentium Pro y Pentium II originales. Como parte de un acuerdo, gran parte del negocio de fabricación y diseño de chips de DEC se vendió a Intel. Esto incluyó la implementación StrongARM de DEC de la arquitectura informática ARM, que Intel comercializó como los procesadores XScale comúnmente utilizados en Pocket PC. El núcleo de Digital Semiconductor, el grupo de microprocesadores Alpha, permaneció con DEC, mientras que los edificios de oficinas asociados fueron a Intel como parte de la fábrica de Hudson.

Modelos mejorados

Las primeras generaciones de chips Alpha fueron algunas de las más innovadoras de su época.

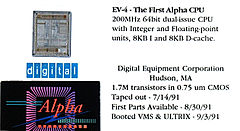

- La primera versión, la Alpha 21064 o EV4, es el primer microprocesador CMOS cuya frecuencia de funcionamiento rivalizó con minicomputadoras ECL de mayor potencia y mainframes.

- El segundo, 21164 o EV5, es el primer microprocesador para colocar un gran caché secundario en el chip.

- El tercero, 21264 o EV6, es el primer microprocesador para combinar tanto alta frecuencia de operación como la microarquitectura de ejecución fuera de orden más complicada.

- El 21364 o EV7 es el primer procesador de alto rendimiento para tener un controlador de memoria en chip.

- Los no producidos 21464 o EV8 habría sido el primero en incluir la multitección simultánea, pero esta versión fue cancelada después de la venta de DEC a Compaq. El Tarantula proyecto de investigación, que probablemente habría sido llamado EV9, habría sido el primer procesador Alfa para tener una unidad de procesador vectorial.

Un informe persistente atribuido a expertos de DEC sugiere que la elección de la etiqueta AXP para el procesador fue realizada por el departamento legal de DEC, que aún estaba dolido por el fiasco de la marca registrada VAX. Después de una larga búsqueda, la etiqueta "AXP" se encontró totalmente libre de cargas. Dentro de la industria informática, comenzó una broma de que el acrónimo AXP significaba "Casi exactamente PRISM".

Principios de diseño

La arquitectura Alpha fue pensada para ser un diseño de alto rendimiento. Digital pretendía que la arquitectura soportara un aumento de mil veces en el rendimiento durante veinticinco años. Para garantizar esto, se eliminó cualquier característica arquitectónica que impidiera la emisión de múltiples instrucciones, la frecuencia de reloj o el multiprocesamiento. Como resultado, el Alfa no tiene:

- Ranuras de demora de la Subdivisión

- Instrucciones suprimidas

- Instrucciones de carga o almacenamiento de byte (más tarde añadido con las extensiones de Word Byte (BWX))

Códigos de condición

El Alpha no tiene códigos de condición para instrucciones enteras para eliminar un cuello de botella potencial en el registro de estado de condición. Las instrucciones que resultan en un desbordamiento, como sumar dos números cuyo resultado no cabe en 64 bits, escriben los 32 o 64 bits menos significativos en el registro de destino. El acarreo se genera realizando una comparación sin signo en el resultado con cualquiera de los operandos para ver si el resultado es más pequeño que cualquiera de los operandos. Si la prueba fue verdadera, el valor uno se escribe en el bit menos significativo del registro de destino para indicar la condición.

Registros

La arquitectura define un conjunto de 32 registros de enteros y un conjunto de 32 registros de punto flotante además de un contador de programa, dos registros de bloqueo y un registro de control de punto flotante (FPCR). También define registros que eran opcionales, implementados solo si la implementación los requería. Por último, se definen los registros para PALcode.

Los registros de enteros se denotan por R0 a R31 y los registros de punto flotante se denotan por F0 a F31. Los registros R31 y F31 están cableados a cero y se ignoran las escrituras en esos registros mediante instrucciones. Digital consideró usar un archivo de registro combinado, pero se determinó que un archivo de registro dividido era mejor, ya que permite que las implementaciones de dos chips tengan un archivo de registro ubicado en cada chip y las implementaciones de solo números enteros omiten el archivo de registro de punto flotante que contiene el registros de punto flotante. También se determinó que un archivo de registro dividido era más adecuado para el problema de instrucciones múltiples debido a la cantidad reducida de puertos de lectura y escritura. También se consideró el número de registros por archivo de registro, siendo 32 y 64 contendientes. Digital concluyó que 32 registros era más adecuado ya que requería menos espacio en el troquel, lo que mejora las frecuencias de reloj. Se consideró que este número de registros no era un problema importante con respecto al rendimiento y el crecimiento futuro, ya que treinta y dos registros podrían admitir al menos el problema de instrucción de ocho vías.

El contador de programa es un registro de 64 bits que contiene una dirección de byte virtual alineada con una palabra larga, es decir, los dos bits inferiores del contador de programa siempre son cero. La PC se incrementa en cuatro a la dirección de la siguiente instrucción cuando se decodifica una instrucción. Las instrucciones de bloqueo de carga y almacenamiento condicional utilizan un indicador de bloqueo y un registro de dirección física bloqueado para el soporte de multiprocesador. El registro de control de punto flotante (FPCR) es un registro de 64 bits definido por la arquitectura destinado a ser utilizado por implementaciones Alpha con hardware de punto flotante compatible con IEEE 754.

Tipos de datos

En la arquitectura Alpha, un byte se define como un dato de 8 bits (octeto), una palabra como un dato de 16 bits, una palabra larga como dato de 32 bits, quadword como dato de 64 bits y octaword como dato de 128 bits.

La arquitectura Alpha definió originalmente seis tipos de datos:

- entero de cuádruplo (64-bit)

- entero de la palabra larga (32-bit)

- IEEE T-punto flotante (doble precisión, 64-bit)

- IEEE S-punto flotante (precisión total, 32 bits)

Para mantener un nivel de compatibilidad con VAX, la arquitectura de 32 bits que precedió a Alpha, se incluyen otros dos tipos de datos de coma flotante:

- VAX G-punto flotante (doble precisión, 64-bit)

- VAX F-punto flotante (precisión total, 32-bit)

- VAX El punto flotante de H (cuarta precisión, 128 bits) no fue soportado, pero otra opción flotante de 128 bits, punto flotante X, está disponible en Alpha, pero no en VAX.

H y X han sido descritos como similares, pero no idénticos. La emulación de software para H-floating está disponible en DEC, como es un convertidor de nivel de código fuente llamado DECmigrate.

Memoria

El Alpha tiene un espacio de direcciones virtuales lineales de 64 bits sin segmentación de memoria. Las implementaciones pueden implementar un espacio de direcciones virtuales más pequeño con un tamaño mínimo de 43 bits. Aunque los bits no utilizados no se implementaron en hardware como TLB, la arquitectura requirió implementaciones para verificar si son cero para garantizar la compatibilidad del software con implementaciones con un espacio de direcciones virtuales más grande (o completo).

Formatos de instrucción

El Alpha ISA tiene una longitud de instrucción fija de 32 bits. Tiene seis formatos de instrucciones.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | Tipo |

| Opcode | Ra | Rb | No utilizados | 0 | Función | Rc | Integer operate | |||||||||||||||||||||||||

| Opcode | Ra | Literal | 1 | Función | Rc | Integer operan, literal | ||||||||||||||||||||||||||

| Opcode | Ra | Rb | Función | Rc | Funcionamiento de punto flotante | |||||||||||||||||||||||||||

| Opcode | Ra | Rb | Desplazamiento | Formato de memoria | ||||||||||||||||||||||||||||

| Opcode | Ra | Desplazamiento | Formato de la Subdivisión | |||||||||||||||||||||||||||||

| Opcode | Función | CALL_PAL formato | ||||||||||||||||||||||||||||||

El formato de operación de enteros es usado por instrucciones de enteros. Contiene un campo de código de operación de 6 bits, seguido del campo Ra, que especifica el registro que contiene el primer operando y el campo Rb, especifica el registro que contiene el segundo operando. El siguiente es un campo de 3 bits que no se usa y está reservado. Un campo de 1 bit contiene un "0", que distingue este formato del formato literal entero. Sigue un campo de función de 7 bits, que se usa junto con el código de operación para especificar una operación. El último campo es el campo Rc, que especifica el registro en el que se debe escribir el resultado de un cálculo. Los campos de registro tienen una longitud de 5 bits, necesarios para direccionar 32 ubicaciones únicas, los 32 registros de enteros.

El formato de literal entero es usado por instrucciones de enteros que usan un literal como uno de los operandos. El formato es el mismo que el formato de operación de enteros excepto por el reemplazo del campo Rb de 5 bits y los 3 bits de espacio no utilizado con un campo literal de 8 bits que se extiende a cero a un operando de 64 bits.

El formato de operación de coma flotante se utiliza en las instrucciones de coma flotante. Es similar al formato de operación de número entero, pero tiene un campo de función de 11 bits que es posible mediante el uso de bits literales y no utilizados que están reservados en el formato de operación de número entero.

El formato de memoria se usa principalmente para las instrucciones de carga y almacenamiento. Tiene un campo de código de operación de 6 bits, un campo Ra de 5 bits, un campo Rb de 5 bits y un campo de desplazamiento de 16 bits.

Las instrucciones de bifurcación tienen un campo de código de operación de 6 bits, un campo Ra de 5 bits y un campo de desplazamiento de 21 bits. El campo Ra especifica un registro para ser probado por una instrucción de bifurcación condicional, y si se cumple la condición, el contador del programa se actualiza agregando el contenido del campo de desplazamiento con el contador del programa. El campo de desplazamiento contiene un entero con signo y si el valor del entero es positivo, si se toma la bifurcación, entonces se incrementa el contador del programa. Si el valor del entero es negativo, entonces el contador del programa se decrementa si se toma la bifurcación. El rango de una rama es, por lo tanto, ±1 Mi instrucciones, o ±4 MiB. Alpha Architecture se diseñó con una amplia gama como parte del objetivo de futuro de la arquitectura.

El formato CALL_PAL es utilizado por la instrucción CALL_PAL, que se utiliza para llamar a las subrutinas PALcode. El formato retiene el campo de código de operación pero reemplaza los otros con un campo de función de 26 bits, que contiene un número entero que especifica una subrutina PAL.

Conjunto de instrucciones

Instrucciones de control

Las instrucciones de control consisten en saltos y saltos condicionales e incondicionales. Las instrucciones de bifurcación condicionales e incondicionales usan el formato de instrucción de bifurcación, mientras que las instrucciones de salto usan el formato de instrucción de memoria.

Las bifurcaciones condicionales prueban si el bit menos significativo de un registro está activado o borrado, o comparan un registro como una palabra cuádruple con signo a cero, y bifurcan si la condición especificada es verdadera. Las condiciones disponibles para comparar un registro con cero son igualdad, desigualdad, menor que, menor o igual que, mayor que o igual que y mayor que. La nueva dirección se calcula mediante la alineación de palabras largas y el signo que extiende el desplazamiento de 21 bits y lo agrega a la dirección de la instrucción que sigue a la bifurcación condicional.

Las ramas incondicionales actualizan el contador del programa con una nueva dirección calculada de la misma manera que las ramas condicionales. También guardan la dirección de la instrucción que sigue a la bifurcación incondicional en un registro. Hay dos instrucciones de este tipo, y difieren solo en las sugerencias proporcionadas para el hardware de predicción de bifurcación.

Hay cuatro instrucciones de salto. Todos estos realizan la misma operación, guardando la dirección de la instrucción que sigue al salto y proporcionando al contador del programa una nueva dirección desde un registro. Difieren en las sugerencias proporcionadas al hardware de predicción de bifurcaciones. El campo de desplazamiento no utilizado se utiliza para este propósito.

Aritmética entera

Las instrucciones aritméticas de enteros realizan sumas, multiplicaciones y restas en palabras largas y cuádruples; y comparación en quadwords. No hay instrucciones para la división ya que los arquitectos consideraron que la implementación de la división en el hardware era adversa a la simplicidad. Además de las instrucciones estándar de suma y resta, hay versiones escaladas. Estas versiones desplazan el segundo operando a la izquierda dos o tres bits antes de sumar o restar. Las instrucciones Multiply Longword y Multiply Quadword escriben los 32 o 64 bits menos significativos de un resultado de 64 o 128 bits en el registro de destino, respectivamente. Dado que es útil para obtener la mitad más significativa, se proporciona la instrucción Unsigned Multiply Quadword High (UMULH). UMULH se utiliza para implementar algoritmos aritméticos y de división de precisión múltiple. El concepto de una instrucción separada para la multiplicación que devuelve la mitad más significativa de un resultado se tomó de PRISM.

Las instrucciones que operan en palabras largas ignoran la mitad más significativa del registro y el resultado de 32 bits se extiende con signo antes de que se escriba en el registro de destino. De forma predeterminada, las instrucciones de sumar, multiplicar y restar, con la excepción de UMULH y las versiones escaladas de sumar y restar, no se interceptan en caso de desbordamiento. Cuando se requiere dicha funcionalidad, se proporcionan versiones de estas instrucciones que realizan la detección de desbordamiento y atrapan el desbordamiento.

Las instrucciones de comparación comparan dos registros o un registro y un literal y escriben '1' al registro de destino si la condición especificada es verdadera o '0' si no. Las condiciones son igualdad, desigualdad, menor o igual que y menor que. Con la excepción de las instrucciones que especifican las dos condiciones anteriores, existen versiones que realizan comparaciones firmadas y no firmadas.

Las instrucciones aritméticas de enteros utilizan los formatos de instrucción de operación de enteros.

Lógica y shift

(feminine)Las instrucciones lógicas consisten en aquellas para realizar operaciones lógicas bit a bit y movimientos condicionales en los registros de enteros. Las instrucciones lógicas bit a bit realizan AND, NAND, NOR, OR, XNOR y XOR entre dos registros o un registro y un literal. Las instrucciones de movimiento condicional prueban un registro como una palabra cuádruple con signo a cero y se mueven si la condición especificada es verdadera. Las condiciones especificadas son igualdad, desigualdad, menor o igual que, menor que, mayor o igual que y mayor que. Las instrucciones de desplazamiento realizan desplazamientos aritméticos a la derecha y desplazamientos lógicos a la izquierda y a la derecha. La cantidad de cambio viene dada por un registro o literal. Las instrucciones lógicas y de cambio utilizan los formatos de instrucción de operación de enteros.

Extensiones

Extensiones de byte-palabra (BWX)

Alphas posteriores incluyen extensiones de byte-word, un conjunto de instrucciones para manipular tipos de datos de 8 y 16 bits. Estas instrucciones se introdujeron por primera vez en el microprocesador 21164A (EV56) y están presentes en todas las implementaciones posteriores. Estas instrucciones realizan operaciones que anteriormente requerían múltiples instrucciones para implementar, lo que mejora la densidad del código y el rendimiento de ciertas aplicaciones. BWX también facilita la emulación del código de máquina x86 y la escritura de controladores de dispositivos.

| Mnemonic | Instrucción |

|---|---|

LDBU | Carga Cero de carga de la memoria al registro |

LDWU | Cargar palabra Zero-Extended de la memoria al registro |

SEXTB | Sign Extend Byte |

SEXTW | Sign Extend Word |

STB | Tienda Byte de Registro a Memoria |

STW | Almacenar Word desde Registro a Memoria |

Instrucciones de video en movimiento (MVI)

Motion Video Instructions (MVI) era una extensión del conjunto de instrucciones de Alpha ISA que añadía instrucciones para operaciones de instrucción única, datos múltiples (SIMD). Las implementaciones Alpha que implementan MVI, en orden cronológico, son Alpha 21164PC (PCA56 y PCA57), Alpha 21264 (EV6) y Alpha 21364 (EV7). A diferencia de la mayoría de los otros conjuntos de instrucciones SIMD del mismo período, como MIPS' MDMX o el conjunto de instrucciones visuales de SPARC, pero al igual que las extensiones de aceleración multimedia de PA-RISC (MAX-1, MAX-2), MVI era un conjunto de instrucciones simple compuesto por unas pocas instrucciones que operan en tipos de datos enteros. almacenados en registros enteros existentes.

La simplicidad de MVI se debe a dos razones. En primer lugar, Digital había determinado que Alpha 21164 ya era capaz de realizar la decodificación de DVD a través del software, por lo que no requería provisiones de hardware para este propósito, pero era ineficiente en la codificación MPEG-2. La segunda razón es el requisito de conservar los tiempos de ciclo rápidos de las implementaciones. Agregar muchas instrucciones habría complicado y ampliado la lógica de decodificación de instrucciones, reduciendo la frecuencia de reloj de una implementación.

MVI consta de 13 instrucciones:

| Mnemonic | Instrucción |

|---|---|

MAXSB8 | Vector Signed Byte Maximum |

MAXSW4 | Vector Signed Word Maximum |

MAXUB8 | Vector Unsigned Byte Maximum |

MAXUW4 | Vector Unsigned Word Maximum |

MINSB8 | Vector Signed Byte Minimum |

MINSW4 | Vector Signed Word Minimum |

MINUB8 | Vector Unsigned Byte Minimum |

MINUW4 | Vector Unsigned Word Minimum |

PERR | Error de píxel |

PKLB | Pack Longwords a Bytes |

PKWB | Pack Words to Bytes |

UNPKBL | Unpack Bytes a Longwords |

UNPKBW | Unpack Bytes a Words |

Extensiones de coma flotante (FIX)

Las extensiones de punto flotante (FIX) son una extensión de la arquitectura Alpha. Introduce nueve instrucciones para la raíz cuadrada de coma flotante y para transferir datos hacia y desde los registros de números enteros y los registros de coma flotante. El Alpha 21264 (EV6) es el primer microprocesador que implementa estas instrucciones.

| Mnemonic | Instrucción |

|---|---|

FTOIS | Punto flotante para Integer Register Move, S_floating |

FTOIT | Punto de flotación para Integer Register Move, T_floating |

ITOFF | Integer to Floating-point Register Move, F_floating |

ITOFS | Integer to Floating-point Register Move, S_floating |

ITOFT | Integer to Floating-point Register Move, T_floating |

SQRTF | raíz cuadrada F_floating |

SQRTG | Base cuadrada G_flotación |

SQRTS | Base cuadrada S_floating |

SQRTT | Base cuadrada T_floating |

Extensiones de recuento (CIX)

Count Extensions (CIX) es una extensión de la arquitectura que introduce tres instrucciones para contar bits. Estas instrucciones se clasifican como instrucciones aritméticas enteras. Se implementaron por primera vez en Alpha 21264A (EV67).

| Mnemonic | Instrucción |

|---|---|

CTLZ | Conde liderando Zero |

CTPOP | Conde Población |

CTTZ | Conde Trailing Zero |

Implementaciones

En el momento de su anuncio, Alpha fue anunciada como una arquitectura para los próximos 25 años. Si bien esto no fue así, Alpha, sin embargo, ha tenido una vida razonablemente larga. La primera versión, el Alpha 21064 (también llamado EV4) se presentó en noviembre de 1992 y funcionaba hasta a 192 MHz; un ligero encogimiento de la matriz (el EV4S, encogido de 0,75 µm a 0,675 µm) funcionó a 200 MHz unos meses después. El procesador de 64 bits era un diseño superescalar y supercanalizado, como otros diseños de RISC, pero sin embargo los superó a todos y DEC lo promocionó como el procesador más rápido del mundo. La cuidadosa atención al diseño de circuitos, un sello distintivo del equipo de diseño de Hudson, como un enorme circuito de reloj centralizado, les permitió hacer funcionar la CPU a velocidades más altas, aunque la microarquitectura era bastante similar a la de otros chips RISC. En comparación, el Intel Pentium menos costoso funcionó a 66 MHz cuando se lanzó la primavera siguiente.

El Alpha 21164 o EV5 estuvieron disponibles en 1995 con frecuencias de procesador de hasta 333 MHz. En julio de 1996, la velocidad de la línea aumentó a 500 MHz, en marzo de 1998 a 666 MHz. También en 1998 se lanzó el Alpha 21264 (EV6) a 450 MHz, alcanzando finalmente (en 2001 con el 21264C/EV68CB< /i>) 1,25 GHz. En 2003, se lanzó el Alpha 21364 o EV7 Marvel, esencialmente un núcleo EV68 con cuatro enlaces de comunicación entre procesadores de 1,6 GB/s para mejorar rendimiento del sistema multiprocesador, funcionando a 1 o 1,15 GHz.

En 1996, se autorizó la producción de chips Alpha a Samsung Electronics Company. Tras la compra de Digital por parte de Compaq, la mayoría de los productos Alpha se colocaron en API NetWorks, Inc. (anteriormente Alpha Processor Inc.), una empresa privada financiada por Samsung y Compaq. En octubre de 2001, Microway se convirtió en el proveedor exclusivo de ventas y servicios de API NetWorks' Línea de productos basada en alfa.

El 25 de junio de 2001, Compaq anunció que Alpha se eliminaría paulatinamente en 2004 a favor de Itanium de Intel, canceló el chip EV8 planificado y vendió toda la propiedad intelectual de Alpha a Intel.. Hewlett-Packard se fusionó con Compaq en 2002; HP anunció que el desarrollo de la serie Alpha continuaría durante algunos años más, incluido el lanzamiento de una variante EV7 de 1,3 GHz denominada EV7z. Esta sería la iteración final de Alpha, el EV79 de 0,13 µm también se canceló.

Alpha también se implementa en Piranha, un prototipo de investigación desarrollado por los grupos de Investigación Corporativa y Desarrollo de Hardware Ininterrumpido de Compaq en el Laboratorio de Investigación Occidental y el Centro de Investigación de Sistemas. Piranha es un diseño multinúcleo para cargas de trabajo de procesamiento de transacciones que contiene ocho núcleos simples. Fue descrito en el 27º Simposio Internacional Anual sobre Arquitectura de Computadores en junio de 2000.

Historia del modelo

| Modelo | ISA | ||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| EV4 | 21064 | 1992 | 100–200 | 0,75 | 1.68 | 234 | 290 | 30 | 3.3 | 8 | 8 | – | 128 KB–16 MB | ||

| EV4S | 21064 | 1993 | 100–200 | 0.675 | 1.68 | 186 | 290 | 27 | 3.3 | 8 | 8 | – | 128 KB–16 MB | ||

| EV45 | 21064A | 1994 | 200 a 300 | 0.5 | 2.85 | 164 | 33 | 3.3 | 16 | 16 | – | 256 KB–16 MB | |||

| LCA4 | 21066 | 1993 | 100–166 | 0.675 | 1.75 | 209 | 21 | 3.3 | 8 | 8 | – | ||||

| LCA4 | 21068 | 1994 | 66 | 0.675 | 1.75 | 209 | 9 | 3.3 | 8 | 8 | – | ||||

| LCA45 | 21066A | 1994 | 100–266 | 0.5 | 1.8 | 161 | 23 | 3.3 | 8 | 8 | – | ||||

| LCA45 | 21068A | 1994 | 100 | 0.5 | 1.8 | 161 | 3.3 | 8 | 8 | – | |||||

| EV5 | 21164 | 1995 | 266–500 | 0.5 | 9.3 | 299 | 296 | 56 | 3.3/2.5 | 8 | 8 | 96 KB | Hasta 64 MB | R | |

| EV56 | 21164A | 1996 | 366 a 666 | 0,355 | 9.66 | 209 | 31 a 55 | 3.3/2.5 | 8 | 8 | 96 KB | Hasta 64 MB | R,B | ||

| PCA56 | 21164PC | 1997 | 400-533 | 0,355 | 3.5 | 141 | 264 | 26 a 35 | 3.3/2.5 | 8 | 16 | – | 512 KB–4 MB | R,B,M | |

| PCA57 | 21164PC | 600 a 666 | 0,28 | 5.7 | 101 | 283 | 18 a 23 | 2.5/2.0 | 16 | 32 | – | 512 KB–4 MB | R,B,M | ||

| EV6 | 21264 | 1998 | 450–600 | 0,355 | 15.2 | 314 | 389 | 73 | 2.0 | 64 | 64 | – | 2 a 8 MB | R,B,M,F | |

| EV67 | 21264A | 1999 | 600–750 | 0,25 | 15.2 | 210 | 389 | 2.0 | 64 | 64 | – | 2 a 8 MB | R,B,M,F,C | ||

| EV68AL | 21264B | 2001 | 800–833 | 0.18 | 15.2 | 125 | 1.7 | 64 | 64 | – | 2 a 8 MB | R,B,M,F,C,T | |||

| EV68CB | 21264C | 2001 | 1000–1250 | 0.18 | 15.2 | 125 | 65 a 75 | 1.65 | 64 | 64 | – | 2 a 8 MB | R,B,M,F,C,T | ||

| EV68CX | 21264D | 1.65 | 64 | 64 | – | 2 a 8 MB | R,B,M,F,C,T | ||||||||

| EV7 | 21364 | 2003 | 1000–1150 | 0.18 | 130 | 397 | 125 | 1,5 | 64 | 64 | 1.75 MB | – | R,B,M,F,C,T | ||

| EV7z | 21364 | 2004 | 1300 | 0.18 | 130 | 397 | 125 | 1,5 | 64 | 64 | 1.75 MB | – | R,B,M,F,C,T | ||

| Cancelada | |||||||||||||||

| EV78/EV79 | 21364A | Slated for 2004 | 1700 | 0,13 | 152 | 300 | 120 | 1.2 | 64 | 64 | 1.75 MB | – | R,B,M,F,C,T | ||

| EV8 | 21464 | Slated for 2003 | 1200–2000 | 0.125 | 250 | 420 | 1800 | ? | 1.2 | 64 | 64 | 3 MB | – | R,B,M,F,C,T | |

| Modelo | ISA | ||||||||||||||

- Extensiones ISA

- R – Soporte de hardware para redondear al infinito y el infinito negativo.

- B – BWX, "Byte/Word Extension", agregando instrucciones para permitir operaciones de 8- y 16-bit de memoria y I/O

- M – MVI, instrucciones "multimedia"

- F – FIX, instrucciones para mover datos entre registros enteros y puntos flotantes y para raíz cuadrada

- C – CIX, instrucciones para contar y encontrar bits

- T – soporte para prefetch con intención de modificar para mejorar el rendimiento del primer intento de adquirir una cerradura

Rendimiento

Para ilustrar el rendimiento comparativo de los sistemas basados en Alpha, a continuación se enumeran algunos números de rendimiento de Standard Performance Evaluation Corporation (SPEC) (SPECint95, SPECfp95). Tenga en cuenta que los resultados de SPEC afirman informar el rendimiento medido de un sistema informático completo (CPU, bus, memoria, optimizador del compilador), no solo de la CPU. Tenga en cuenta también que el punto de referencia y la escala cambiaron de 1992 a 1995. Sin embargo, las cifras dan una impresión aproximada del rendimiento de la arquitectura Alpha (64 bits), en comparación con las ofertas contemporáneas de HP (64 bits) y basadas en Intel (32 bits). Quizás la tendencia más obvia es que, si bien Intel siempre pudo acercarse razonablemente a Alpha en el rendimiento de números enteros, la diferencia fue considerable en el rendimiento de punto flotante. Por otro lado, HP (PA-RISC) también está razonablemente cerca de Alpha, pero estas CPU funcionan a velocidades de reloj (MHz) significativamente más bajas. Las tablas carecen de dos valores importantes: el consumo de energía y el precio de una CPU.

|

|

Sistemas basados en alfa

La primera generación de sistemas basados en DEC Alpha comprende las estaciones de trabajo y los servidores de gama baja de la serie DEC 3000 AXP, los servidores de gama media de la serie DEC 4000 AXP y los servidores de gama alta de las series DEC 7000 AXP y 10000 AXP. Los sistemas DEC 3000 AXP utilizan el mismo bus TURBOchannel que los modelos anteriores de DECstation basados en MIPS, mientras que el 4000 se basa en Futurebus+ y el 7000/10000 comparte una arquitectura con los modelos VAX correspondientes.

DEC también produjo una estación de trabajo Alpha con configuración de computadora personal (PC) con un bus EISA (Extended Industry Standard Architecture), la DECpc AXP 150 (nombre en clave Jensen, también llamada DEC 2000 AXP). Este es el primer sistema Alpha compatible con Windows NT. Más tarde, DEC produjo versiones Alpha de sus líneas de PC Celebris XL y Digital Personal Workstation, con 21164 procesadores.

Digital también produjo computadoras de placa única basadas en VMEbus para uso integrado e industrial. La primera generación incluye AXPvme 64 y AXPvme 64LC basados en 21068, y AXPvme 160 basado en 21066. Estos se introdujeron el 1 de marzo de 1994. Los modelos posteriores, como AXPvme 100, AXPvme 166 y AXPvme 230, se basan en el procesador 21066A., mientras que Alpha VME 4/224 y Alpha VME 4/288 se basan en el procesador 21064A. Los últimos modelos, Alpha VME 5/352 y Alpha VME 5/480, se basan en el procesador 21164.

El chip 21066 se usa en la estación de trabajo compacta DEC Multia VX40/41/42 y en la computadora portátil ALPHAbook 1 de Tadpole Technology.

En 1994, DEC lanzó una nueva gama de sistemas AlphaStation y AlphaServer. Estos utilizan procesadores 21064 o 21164 e introdujeron el bus PCI, búferes de cuadro compatibles con VGA y teclados y ratones estilo PS/2. La serie AlphaServer 8000 reemplaza a DEC 7000/10000 AXP y también emplea buses XMI y FutureBus+.

La AlphaStation XP1000 es la primera estación de trabajo basada en el procesador 21264. Los modelos AlphaServer/Station posteriores basados en el 21264 se clasifican en DS (servidor departamental), ES (servidor empresarial) o GS (servidor global) familias

El chip 21364 final se usa en los modelos AlphaServer ES47, ES80 y GS1280 y AlphaStation ES47.

DEC produjo varias placas base OEM, como la AXPpci 33 "NoName" basada en 21066 y 21068, que fue parte de un gran impulso en el mercado OEM por parte de la empresa, la 21164- AlphaPC 164 y AlphaPC 164LX basados en 21164PC, AlphaPC 164SX y AlphaPC 164RX basados en 21164PC y AlphaPC 264DP basados en 21264. Varios terceros, como Samsung y API, también produjeron placas base OEM, como API UP1000 y UP2000.

Para ayudar a terceros a desarrollar hardware y software para la plataforma, DEC produjo placas de evaluación, como EB64+ y EB164 para los microprocesadores Alpha 21064A y 21164, respectivamente.

NetApp usó los procesadores 21164 y 21264 en varios sistemas de almacenamiento conectados a la red, mientras que Cray usó los procesadores 21064 y 21164 en sus supercomputadoras paralelas masivas T3D y T3E.

Superordenadores

La supercomputadora más rápida basada en procesadores Alpha fue la ASCI Q en el Laboratorio Nacional de Los Álamos. La máquina se construyó como un HP AlphaServer SC45/GS Cluster. Tenía 4096 CPU Alpha (21264 EV-68, 1,25 GHz) y alcanzó un Rmax de 7,727 TFLOPS. Varios científicos afirman que la arquitectura Sunway que alimenta a Sunway TaihuLight es un descendiente autorizado de la arquitectura Alpha. Si se contara como una supercomputadora Alpha, TaihuLight sería el sistema Alpha más poderoso jamás construido, con una calificación LINPACK de 93 petaflops, en 40,960 núcleos.

Contenido relacionado

Espoleta de proximidad

Unidad tipografica

Cátodo frío