Convertidor analógico-digital de aproximación sucesiva

Un ADC de aproximación sucesiva es un tipo de convertidor analógico a digital (ADC) que convierte una forma de onda analógica continua en una representación digital discreta mediante una búsqueda binaria a través de todos los niveles de cuantificación posibles antes de converger finalmente en una salida digital para cada conversión.

Algoritm

El circuito convertidor analógico-digital de aproximación sucesiva normalmente consta de cuatro subcircuitos principales:

- Un circuito de muestra y retención para adquirir el voltaje de entrada Vdentro.

- Un comparador de tensión analógica que compara Vdentro a la salida del DAC interno y produce el resultado de la comparación con el registro de aproximación sucesiva (SAR).

- Subcircuito de registro de aproximación sucesiva diseñado para suministrar un código digital aproximado Vdentro al DAC interno.

- Un DAC de referencia interna que, para comparación con Vref, suministra la comparación con un voltaje analógico igual a la salida del código digital SARdentro.

El registro de aproximación sucesiva se inicializa de modo que el bit más significativo (MSB) sea igual a un 1 digital. Este código se introduce en el DAC, que luego suministra el equivalente analógico de este código digital (Vref/2) al circuito comparador para su comparación con el voltaje de entrada muestreado. Si este voltaje analógico excede Vin, entonces el comparador hace que el SAR restablezca este bit; de lo contrario, el bit se deja como 1. Luego, el siguiente bit se establece en 1 y se realiza la misma prueba, continuando esta búsqueda binaria hasta que se haya probado cada bit en el SAR. El código resultante es la aproximación digital del voltaje de entrada muestreado y finalmente es emitido por el SAR al final de la conversión (EOC).

Matemáticamente, sea Vin = xVref, por lo que x en [−1, 1] es el voltaje de entrada normalizado. El objetivo es digitalizar aproximadamente x con una precisión de 1⁄2n. El algoritmo procede de la siguiente manera:

- Estimación inicial x0 = 0.

- iT aproximación xi = xi−1 − s()xi−1 − x)/2i, donde, s()x) es la función signum (sgn(x) = +1 para x ≥ 0, −1 para x 0). Se sigue usando la inducción matemática que Silencioxn − x← ≤ 1/2n.

Como se muestra en el algoritmo anterior, un ADC SAR requiere:

- Fuente de tensión de entrada Vdentro.

- Fuente de tensión de referencia Vref para normalizar la entrada.

- A DAC to convert the iT aproximación xi a un voltaje.

- Una comparación para desempeñar la función s()xi − x) comparando el voltaje del DAC con el voltaje de entrada.

- Un registro para almacenar la salida de la comparación y aplicar xi−1 − s()xi−1 − x)/2i.

Ejemplos

Ejemplo 1: Los diez pasos para convertir una entrada analógica en digital de 10 bits, utilizando aproximaciones sucesivas, se muestran aquí para todos los voltajes de 5 V a 0 V en iteraciones de 0,1 V. Dado que el voltaje de referencia es 5 V, cuando el voltaje de entrada también es 5 V, todos los bits están configurados. A medida que el voltaje disminuye a 4,9 V, solo se borran algunos de los bits menos significativos. El MSB permanecerá configurado hasta que la entrada sea la mitad del voltaje de referencia, 2,5 V.

Los pesos binarios asignados a cada bit, comenzando por el bit más significativo (MSB), son 2,5, 1,25, 0,625, 0,3125, 0,15625, 0,078125, 0,0390625, 0,01953125, 0,009765625, 0,0048828125. Todos ellos suman 4,9951171875, es decir, 1111111111 en binario, o un bit menos que 5.

Cuando se compara la entrada analógica con la salida del DAC interno, se compara efectivamente con cada uno de estos pesos binarios, comenzando con el de 2,5 V y manteniéndolo o borrándolo como resultado. Luego, al sumar el siguiente peso al resultado anterior, comparar nuevamente y repetir hasta que todos los bits y sus pesos se hayan comparado con la entrada, se obtiene el resultado, un número binario que representa la entrada analógica.

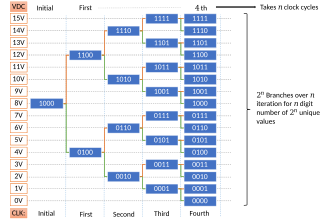

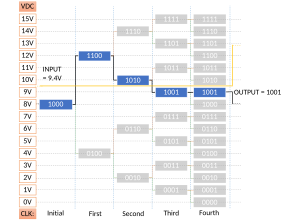

Ejemplo 2: El funcionamiento de un ADC de aproximación sucesiva de 4 bits se ilustra a continuación. El MSB se establece inicialmente en 1, mientras que los dígitos restantes se establecen en cero. Si el voltaje de entrada es inferior al valor almacenado en el registro, en el siguiente ciclo de reloj, el registro cambia su valor al que se ilustra en la figura siguiendo la línea verde. Si el voltaje de entrada es superior, entonces en el siguiente ciclo de reloj, el registro cambia su valor al que se ilustra en la figura siguiendo la línea roja. La estructura simplificada de este tipo de ADC que actúa en un rango de 2n voltios se puede expresar como un algoritmo:

- Iniciar el registro con MSB establecido a 1 y todos los demás valores fijados a cero.

- En ciclo de reloj n-th, si el voltaje es más alto que el voltaje equivalente digital del número registrado, el (n+1)-th dígito de la izquierda se establece a 1. Si el voltaje fue inferior al voltaje equivalente digital, entonces el n-th digit de la izquierda se establece a cero y el siguiente dígito se establece a 1. Para realizar una conversión, un N-bit ADC requiere N tales ciclos de reloj excluyendo el estado inicial.

La aproximación sucesiva del ADC se puede explicar alternativamente asignando primero de manera uniforme cada salida digital a los rangos correspondientes, como se muestra. Se puede ver que el algoritmo divide esencialmente el rango de voltaje en dos regiones y verifica a cuál de las dos regiones pertenece el voltaje de entrada. Los pasos sucesivos implican tomar la región identificada anteriormente y dividirla nuevamente en dos y continuar con la identificación. Esto ocurre hasta que se agotan todas las opciones posibles de representaciones digitales, dejando atrás una región identificada que corresponde solo a una de las representaciones digitales.

Variantes

- Contra tipo ADC: El convertidor D a A puede girarse fácilmente para proporcionar la función inversa A a D conversión. El principio es ajustar el código de entrada del DAC hasta que la salida del DAC entra dentro ±1.2 LSB a la entrada analógica que se convertirá en forma digital binaria.

- Seguimiento de Servo ADC: Es una versión mejorada de un ADC contable. El circuito consiste en un mostrador de arriba hacia abajo con el comparador controlando la dirección del conteo. La salida analógica del DAC se compara con la entrada analógica. Si la entrada es mayor que la señal de salida del DAC, la salida de la comparación es alta y el contador es causado a contar. El seguimiento ADC tiene la ventaja de ser simple. La desventaja, sin embargo, es el tiempo necesario para estabilizarse como nuevo valor de conversión es directamente proporcional a la tasa a la que cambia la señal analógica.

Carga-redistribución sucesiva-aproximación ADC

Una de las implementaciones más comunes del ADC de aproximación sucesiva, el ADC de aproximación sucesiva de redistribución de carga, utiliza un DAC de escalado de carga. El DAC de escalado de carga simplemente consiste en una matriz de capacitores ponderados en binario conmutados individualmente. La cantidad de carga en cada capacitor de la matriz se utiliza para realizar la búsqueda binaria antes mencionada junto con un comparador interno al DAC y el registro de aproximación sucesiva.

- La matriz capacitor se descarga completamente al voltaje offset de la comparación, VOS. Este paso proporciona cancelación automática de compensación (es decir, el voltaje offset no representa nada más que carga muerta, que no puede ser malversado por los condensadores).

- Todos los condensadores dentro del array se cambian a la señal de entrada Vdentro. Los condensadores ahora tienen una carga igual a sus respectivos tiempos de capacitancia el voltaje de entrada menos el voltaje offset sobre cada uno de ellos.

- Los condensadores se cambian para que esta carga se aplique a través de la entrada utilizada en la comparación, creando un voltaje de entrada igual a la comparación −Vdentro.

- El proceso de conversión real procede. Primero, el condensador MSB se cambia a Vref, que corresponde a la gama a gran escala de la ADC. Debido al peso binario de la matriz, el condensador MSB forma un divider de carga 1:1 con el resto de la matriz. Así pues, el voltaje de entrada al comparador es ahora −Vdentro + Vref.2 . Posteriormente, si Vdentro es mayor que Vref.2, entonces la comparación produce un digital 1 como el MSB, de lo contrario produce un 0 digital como el MSB. Cada condensador se prueba de la misma manera hasta que el voltaje de entrada comparador converge al voltaje offset, o al menos lo más cerca posible dada la resolución del DAC.

Uso con circuitos analógicos no ideales

Cuando se implementa como un circuito analógico, donde el valor de cada bit sucesivo no es exactamente 2N (por ejemplo, 1,1, 2,12, 4,05, 8,01, etc.), un enfoque de aproximación sucesiva podría no generar el valor ideal porque el algoritmo de búsqueda binaria elimina incorrectamente lo que cree que es la mitad de los valores que la entrada desconocida no puede ser. Dependiendo de la diferencia entre el rendimiento real y el ideal, el error máximo puede superar fácilmente varios LSB, especialmente a medida que el error entre el 2N real y el ideal se vuelve grande para uno o más bits. Dado que la entrada real es desconocida, es muy importante que la precisión del circuito analógico utilizado para implementar un ADC SAR sea muy cercana a los valores ideales 2N; de lo contrario, no se puede garantizar una búsqueda con la mejor coincidencia.

Véase también

- Ruido de cuantización

- Conversor digital a digital

Referencias

Más lectura

- Diseño de circuito CMOS, diseño y simulación, 3a edición; R. J. Baker; Wiley-IEEE; 1208 páginas; 2010; ISBN 978-0-470-88132-3

- Manual de conversión de datos; Dispositivos analógicos; Newnes; 976 páginas; 2004; ISBN 978-0750678414

Enlaces externos

- Comprender los ADC SAR: su arquitectura y comparación con otros ADCs - Maxim

- Elija el convertidor A/D adecuado para su aplicación - TI