Automatización de diseño electrónico

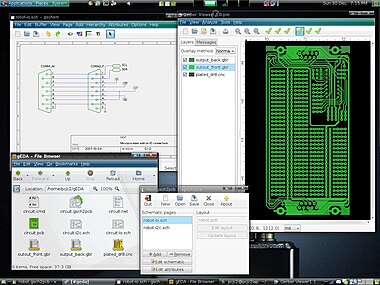

Automatización del diseño electrónico (EDA), también conocido como diseño electrónico asistido por ordenador (ECAD), es una categoría de herramientas de software para diseñar sistemas electrónicos como circuitos integrados y placas de circuito impreso. Las herramientas funcionan juntas en un flujo de diseño que los diseñadores de chips utilizan para diseñar y analizar chips semiconductores completos. Dado que un chip semiconductor moderno puede tener miles de millones de componentes, las herramientas EDA son esenciales para su diseño; este artículo en particular describe EDA específicamente con respecto a los circuitos integrados (CI).

Historia

Primeros días

La primera automatización del diseño electrónico se atribuye a IBM con la documentación de sus computadoras de la serie 700 en la década de 1950.

Antes del desarrollo de EDA, los circuitos integrados se diseñaban y disponían manualmente. Algunos talleres avanzados utilizaron software geométrico para generar cintas para un fotoplotter Gerber, responsable de generar una imagen de exposición monocromática, pero incluso copiaron grabaciones digitales de componentes dibujados mecánicamente. El proceso fue fundamentalmente gráfico, con la traducción de la electrónica a la gráfica hecha manualmente; la empresa más conocida de esta época fue Calma, cuyo formato GDSII todavía se utiliza en la actualidad. A mediados de la década de 1970, los desarrolladores comenzaron a automatizar el diseño de circuitos además del dibujo y se desarrollaron las primeras herramientas de ubicación y enrutamiento; cuando esto ocurrió, las actas de la Design Automation Conference catalogaron la gran mayoría de los desarrollos de la época.

La próxima era comenzó tras la publicación de "Introducción a los sistemas VLSI" por Carver Mead y Lynn Conway en 1980; considerado el libro de texto estándar para el diseño de chips. El resultado fue un aumento en la complejidad de los chips que podían diseñarse, con un mejor acceso a herramientas de verificación de diseño que usaban simulación lógica. Los chips eran más fáciles de diseñar y tenían más probabilidades de funcionar correctamente, ya que sus diseños podían simularse más a fondo antes de la construcción. Aunque los lenguajes y las herramientas han evolucionado, este enfoque general de especificar el comportamiento deseado en un lenguaje de programación textual y dejar que las herramientas obtengan el diseño físico detallado sigue siendo la base del diseño de circuitos integrados digitales en la actualidad.

Las primeras herramientas EDA se produjeron académicamente. Uno de los más famosos fue el "Berkeley VLSI Tools Tarball", un conjunto de utilidades de UNIX utilizadas para diseñar los primeros sistemas VLSI. Todavía se utilizan ampliamente el minimizador de lógica heurística Espresso, responsable de la reducción de la complejidad del circuito y Magic, una plataforma de diseño asistido por computadora. Otro desarrollo crucial fue la formación de MOSIS, un consorcio de universidades y fabricantes que desarrolló una forma económica de capacitar a los estudiantes diseñadores de chips mediante la producción de circuitos integrados reales. El concepto básico era utilizar procesos IC confiables, de bajo costo y de tecnología relativamente baja y empaquetar una gran cantidad de proyectos por oblea, conservando varias copias de chips de cada proyecto. Los fabricantes que cooperaron donaron las obleas procesadas o las vendieron al costo, ya que consideraron que el programa era útil para su propio crecimiento a largo plazo.

Nacimiento de EDA comercial

1981 marcó el comienzo de EDA como industria. Durante muchos años, las empresas electrónicas más grandes, como Hewlett-Packard, Tektronix e Intel, habían buscado EDA internamente, y los gerentes y desarrolladores comenzaron a salir de estas empresas para concentrarse en EDA como negocio. Daisy Systems, Mentor Graphics y Valid Logic Systems se fundaron en esta época y se denominaron colectivamente DMV. En 1981, el Departamento de Defensa de EE. UU. también comenzó a financiar VHDL como lenguaje de descripción de hardware. En unos pocos años, había muchas empresas especializadas en EDA, cada una con un énfasis ligeramente diferente.

La primera feria comercial de EDA se llevó a cabo en la Design Automation Conference en 1984 y en 1986, Verilog, otro popular lenguaje de diseño de alto nivel, fue presentado por primera vez como lenguaje de descripción de hardware por Gateway Design Automation. Los simuladores siguieron rápidamente estas introducciones, lo que permitió la simulación directa de diseños de chips y especificaciones ejecutables. En varios años, se desarrollaron back-ends para realizar síntesis lógica.

Hora moderna

Los flujos digitales actuales son extremadamente modulares, con interfaces que producen descripciones de diseño estandarizadas que se compilan en invocaciones de unidades similares a las células sin tener en cuenta su tecnología individual. Las células implementan funciones lógicas u otras funciones electrónicas a través de la utilización de una tecnología de circuito integrado particular. Los fabricantes generalmente proporcionan bibliotecas de componentes para sus procesos de producción, con modelos de simulación que se ajustan a las herramientas de simulación estándar.

La mayoría de los circuitos analógicos todavía se diseñan de forma manual, lo que requiere un conocimiento especializado exclusivo del diseño analógico (como la combinación de conceptos). Por lo tanto, las herramientas EDA analógicas son mucho menos modulares, ya que se requieren muchas más funciones, interactúan más fuertemente y los componentes son, en general, menos ideales.

EDA para la electrónica ha aumentado rápidamente en importancia con la escala continua de la tecnología de semiconductores. Algunos usuarios son operadores de fundición, que operan las instalaciones de fabricación de semiconductores ("fabs") y personas adicionales responsables de utilizar las empresas de servicios de diseño de tecnología que usan el software EDA para evaluar un diseño entrante para la preparación para la fabricación. Las herramientas EDA también se utilizan para programar la funcionalidad de diseño en FPGA o arreglos de puertas programables en campo, diseños de circuitos integrados personalizables.

Enfoques de software

Diseño

El flujo de diseño se caracteriza principalmente por varios componentes primarios; éstas incluyen:

- Síntesis de alto nivel (addicionalmente conocida como síntesis conductual o síntesis algorítmica) – La descripción de diseño de alto nivel (por ejemplo, en C/C++) se convierte en RTL o en el nivel de transferencia de registro, responsable de representar circuitos mediante la utilización de interacciones entre registros.

- Síntesis lógica – La traducción de la descripción de diseño RTL (por ejemplo, escrita en Verilog o VHDL) en una discreta redista o representación de las puertas lógicas.

- Captura esquemática – Para la CIS de Captura digital, analógica, similar a RF en Orcad por Cadence e ISIS en Proteus.

- Diseño – generalmente diseño con trama esquemática, como Layout en Orcad por Cadence, ARES en Proteus

Simulación

- Simulación de transistores de bajo nivel de la transistor-simulación de un comportamiento esquemático/apagado, exacto a nivel de dispositivo.

- Simulación lógica – digital-imulación de un comportamiento digital de RTL o gate-netlist (boolean 0/1), exacto a nivel booleano.

- Simulación conductual – simulación de alto nivel de la operación arquitectónica de un diseño, precisa a nivel de ciclo o de interfaz.

- Emulación de hardware – Uso de hardware de propósito especial para emular la lógica de un diseño propuesto. A veces se puede conectar en un sistema en lugar de un chip aún construido; esto se llama emulación en circuito.

- Tecnología CAD simula y analiza la tecnología de proceso subyacente. Las propiedades eléctricas de los dispositivos se derivan directamente de la física del dispositivo

Análisis y verificación

- Verificación funcional: asegura que el diseño lógico coincide con las especificaciones y ejecuta las tareas correctamente. Incluye verificación funcional dinámica mediante simulación, emulación y prototipos.

- RTL Formar la adhesión a reglas de codificación como sintaxis, semántica y estilo.

- Verificar el cruce de dominios (Comprobar CDC): similar al forro, pero estos controles/herramientas se especializan en detectar y reportar problemas potenciales como pérdida de datos, metaestabilidad debido al uso de múltiples dominios del reloj en el diseño.

- Verificación formal, también comprobación modelo: intentos de probar, por métodos matemáticos, que el sistema tiene ciertas propiedades deseadas, y que algunos efectos no deseados (como el estancamiento) no pueden ocurrir.

- Comprobación de la equidad: comparación algorítmica entre la descripción RTL de un chip y la computación sintetizada, para asegurar la equivalencia funcional en la lógica nivel.

- Análisis estadístico del tiempo: análisis del tiempo de un circuito de manera independiente, por lo que encontrar un peor caso sobre todos los insumos posibles.

- Extracción de diseño: comenzando con un diseño propuesto, computa las características eléctricas (aproximadas) de cada alambre y dispositivo. A menudo se utiliza en conjunto con el análisis de tiempo estático arriba para estimar el rendimiento del chip completado.

- Solvers de campo electromagnético, o simplemente solvers de campo, resolver las ecuaciones de Maxwell directamente para casos de interés en el diseño IC y PCB. Son conocidos por ser más lentos pero más precisos que la extracción de diseño anterior.

- Verificación física, PV: comprobar si un diseño es fabricable físicamente, y que los chips resultantes no tendrán defectos físicos que prevengan funciones, y cumplirán las especificaciones originales.

Preparación de fabricación

- Preparación de datos de máscaras o MDP - La generación de fotomasks de litografía real, utilizado para la fabricación física del chip.

- Acabado de chip que incluye designaciones y estructuras personalizadas para mejorar la fabricabilidad del diseño. Ejemplos de este último son un anillo de sello y estructuras de relleno.

- Producir un reticle layout con patrones de prueba y marcas de alineación.

- Preparación de diseño a máscara que mejora los datos de diseño con operaciones gráficas, tales como técnicas de mejora de resolución (RET) – métodos para aumentar la calidad de la fotomasca final. Esto también incluye corrección de proximidad óptica (OPC) o tecnología de litografía inversa (ILT) – la compensación inicial para efectos de difracción e interferencia ocurridos más adelante cuando el chip se fabrica con esta máscara.

- Mask generation – La generación de imagen de máscara plana del diseño jerárquico.

- Generación del patrón de prueba automática o ATPG – La generación de datos de patrón sistemáticamente para ejercer tantos componentes lógicos y otros componentes como sea posible.

- Pruebas automáticas incorporadas o BIST – La instalación de autocontroladores de pruebas para probar automáticamente una estructura lógica o de memoria en el diseño

Seguridad funcional

- Análisis de seguridad funcional, cómputo sistemático de las tasas de fracaso en el tiempo (FIT) y métricas de cobertura diagnóstica para los diseños con el fin de satisfacer los requisitos de cumplimiento para los niveles de integridad de seguridad deseados.

- Síntesis de seguridad funcional, añadir mejoras de fiabilidad a elementos estructurados (módulos, RAMs, ROMs, archivos de registro, FIFOs) para mejorar la detección de fallas / tolerancia a fallas. Estos incluyen (no limitado a), la adición de la detección de errores y / o códigos de corrección (Hamming), lógica redundante para la detección de fallas y la tolerancia de falla (duplicado / triplicado) y controles de protocolo (paridad de la interfaz, alineación de direcciones, cuenta de beat)

- Verificación de seguridad funcional, ejecución de una campaña de fallas, incluyendo la inserción de fallas en el diseño y verificación que el mecanismo de seguridad reacciona de una manera apropiada para las fallas que se consideran cubiertas.

Empresas

Empresas actuales

Capitalización de mercado y nombre de la empresa a marzo de 2023:

- $57.87 mil millones – Sinopias

- $56.68 billion – Cadence Design Systems

- AU$4.88 billion – Altium

- ¥77.25 mil millones – Zuken

Empresas antiguas

Capitalización de mercado y nombre de la empresa a diciembre de 2011:

- $2.33 billion – Mentor Graphics; Siemens adquirió Mentor en 2017 y renombrado como Siemens EDA en 2021

- $507 millones – Magma Design Automation; Synopsys adquirió Magma en febrero de 2012

- NT$6.44 mil millones – SpringSoft; Synopsys adquirió SpringSoft en agosto de 2012

Nota: EEsof probablemente debería estar en esta lista, pero no tiene una capitalización de mercado ya que es la división EDA de Keysight.

Adquisiciones

Muchas empresas de EDA adquieren pequeñas empresas con software u otra tecnología que se puede adaptar a su negocio principal. La mayoría de los líderes del mercado son fusiones de muchas empresas más pequeñas y esta tendencia se ve favorecida por la tendencia de las empresas de software a diseñar herramientas como accesorios que encajan naturalmente en el conjunto de programas de circuitos digitales de un proveedor más grande; muchas herramientas nuevas incorporan diseño analógico y sistemas mixtos. Esto sucede debido a la tendencia de colocar sistemas electrónicos completos en un solo chip.

Jornadas Técnicas sobre EDA

- Design Automation Conference

- International Conference on Computer-Aided Design

- Diseño Automatización y Prueba en Europa

- Conferencia de Automatización de Diseño de Asia y el Pacífico Sur

- Simposios sobre tecnología y circuitos VLSI

Contenido relacionado

Detector de anomalías magnéticas

Submarino clase Virginia

Acero