Autobús (informática)

En arquitectura informática, un bus (forma abreviada del latín omnibus, e históricamente también llamado autopista de datos o bus de datos) es un sistema de comunicación que transfiere datos entre componentes dentro de una computadora, o entre computadoras. Esta expresión cubre todos los componentes de hardware relacionados (cable, fibra óptica, etc.) y software, incluidos los protocolos de comunicación.

Los primeros buses de computadora eran cables eléctricos paralelos con múltiples conexiones de hardware, pero el término ahora se usa para cualquier disposición física que proporcione la misma función lógica que una barra colectora eléctrica paralela. Los buses de computadora modernos pueden usar conexiones paralelas y seriales de bits, y pueden conectarse en una topología multipunto (paralelo eléctrico) o en cadena, o conectarse mediante concentradores conmutados, como en el caso de Universal Serial Bus (USB).

Antecedentes y nomenclatura

Los sistemas informáticos generalmente constan de tres partes principales:

- La unidad central de procesamiento (CPU) que procesa datos,

- La memoria que contiene los programas y datos para ser procesados, y

- I/O (input/output) dispositivos como periféricos que se comunican con el mundo exterior.

Una de las primeras computadoras podría contener una CPU de tubos de vacío cableada a mano, un tambor magnético para la memoria principal y una cinta perforada y una impresora para leer y escribir datos, respectivamente. Un sistema moderno puede tener una CPU multinúcleo, DDR4 SDRAM para la memoria, una unidad de estado sólido para el almacenamiento secundario, una tarjeta gráfica y una pantalla LCD como sistema de visualización, un mouse y un teclado para la interacción y una conexión Wi-Fi para la red.. En ambos ejemplos, los buses de computadora de una forma u otra mueven datos entre todos estos dispositivos.

En la mayoría de las arquitecturas informáticas tradicionales, la CPU y la memoria principal tienden a estar estrechamente acopladas. Un microprocesador convencionalmente es un solo chip que tiene una serie de conexiones eléctricas en sus pines que se pueden usar para seleccionar una "dirección" en la memoria principal y otro conjunto de pines para leer y escribir los datos almacenados en esa ubicación. En la mayoría de los casos, la CPU y la memoria comparten características de señalización y funcionan en sincronía. El bus que conecta la CPU y la memoria es una de las características definitorias del sistema y, a menudo, se lo denomina simplemente bus del sistema.

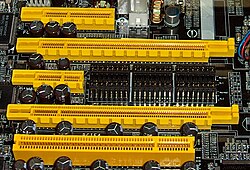

Es posible permitir que los periféricos se comuniquen con la memoria de la misma manera, conectando adaptadores en forma de tarjetas de expansión directamente al bus del sistema. Esto se logra comúnmente a través de algún tipo de conector eléctrico estandarizado, varios de los cuales forman el bus de expansión o el bus local. Sin embargo, como las diferencias de rendimiento entre la CPU y los periféricos varían ampliamente, generalmente se necesita alguna solución para garantizar que los periféricos no reduzcan el rendimiento general del sistema. Muchas CPU cuentan con un segundo conjunto de pines similares a los que se utilizan para comunicarse con la memoria, pero que pueden funcionar a velocidades muy diferentes y con protocolos diferentes. Otros usan controladores inteligentes para colocar los datos directamente en la memoria, un concepto conocido como acceso directo a la memoria. La mayoría de los sistemas modernos combinan ambas soluciones, en su caso.

A medida que aumentaba la cantidad de periféricos potenciales, el uso de una tarjeta de expansión para cada periférico se volvió cada vez más insostenible. Esto ha llevado a la introducción de sistemas de bus diseñados específicamente para soportar múltiples periféricos. Ejemplos comunes son los puertos SATA en las computadoras modernas, que permiten conectar varios discos duros sin necesidad de una tarjeta. Sin embargo, estos sistemas de alto rendimiento suelen ser demasiado caros para implementarlos en dispositivos de gama baja, como un ratón. Esto ha llevado al desarrollo paralelo de una serie de sistemas de bus de bajo rendimiento para estas soluciones, siendo el ejemplo más común el Universal Serial Bus (USB) estandarizado. Todos estos ejemplos pueden denominarse buses periféricos, aunque esta terminología no es universal.

En los sistemas modernos, la diferencia de rendimiento entre la CPU y la memoria principal ha crecido tanto que cantidades cada vez mayores de memoria de alta velocidad se integran directamente en la CPU, lo que se conoce como caché. En dichos sistemas, las CPU se comunican mediante buses de alto rendimiento que funcionan a velocidades mucho mayores que la memoria y se comunican con la memoria mediante protocolos similares a los que se usaban únicamente para los periféricos en el pasado. Estos buses del sistema también se utilizan para comunicarse con la mayoría (o todos) los demás periféricos, a través de adaptadores, que a su vez se comunican con otros periféricos y controladores. Dichos sistemas son arquitectónicamente más similares a las multicomputadoras y se comunican a través de un bus en lugar de una red. En estos casos, los buses de expansión están completamente separados y ya no comparten ninguna arquitectura con su CPU host (y, de hecho, pueden admitir muchas CPU diferentes, como es el caso de PCI). Lo que anteriormente habría sido un bus del sistema ahora se conoce a menudo como un bus frontal.

Dados estos cambios, los términos clásicos "sistema", "expansión" y "periférico" ya no tienen las mismas connotaciones. Otros sistemas de categorización comunes se basan en la función principal del bus, conectando dispositivos interna o externamente, PCI vs. SCSI, por ejemplo. Sin embargo, muchos sistemas de autobuses modernos comunes se pueden usar para ambos; SATA y el eSATA asociado son un ejemplo de un sistema que anteriormente se describiría como interno, mientras que ciertas aplicaciones automotrices utilizan principalmente el IEEE 1394 externo de una manera más similar a un bus de sistema. Otros ejemplos, como InfiniBand e I²C, fueron diseñados desde el principio para ser utilizados tanto interna como externamente.

Autobuses internos

El bus interno, también conocido como bus de datos interno, bus de memoria, bus del sistema o bus frontal, conecta todos los componentes internos de una computadora, como la CPU y la memoria, a la placa base. Los buses de datos internos también se conocen como buses locales, porque están destinados a conectarse a dispositivos locales. Este bus suele ser bastante rápido y es independiente del resto de las operaciones de la computadora.

Autobuses externos

El bus externo, o bus de expansión, se compone de las vías electrónicas que conectan los diferentes dispositivos externos, como una impresora, etc., a la computadora.

Bus de direcciones

Un bus de direcciones es un bus que se utiliza para especificar una dirección física. Cuando un procesador o dispositivo habilitado para DMA necesita leer o escribir en una ubicación de memoria, especifica esa ubicación de memoria en el bus de direcciones (el valor que se leerá o escribirá se envía en el bus de datos). El ancho del bus de direcciones determina la cantidad de memoria que un sistema puede direccionar. Por ejemplo, un sistema con un bus de direcciones de 32 bits puede direccionar 232 (4 294 967 296) ubicaciones de memoria. Si cada ubicación de memoria contiene un byte, el espacio de memoria direccionable es de 4 GiB.

Multiplexación de direcciones

Los primeros procesadores usaban un cable para cada bit del ancho de la dirección. Por ejemplo, un bus de direcciones de 16 bits tenía 16 cables físicos que componían el bus. A medida que los buses se hacían más anchos y largos, este enfoque se volvió costoso en términos de la cantidad de pines de chips y huellas en la placa. A partir de la DRAM Mostek 4096, la multiplexación de direcciones implementada con multiplexores se volvió común. En un esquema de direcciones multiplexadas, la dirección se envía en dos partes iguales en ciclos de bus alternos. Esto reduce a la mitad el número de señales de bus de direcciones requeridas para conectarse a la memoria. Por ejemplo, se puede implementar un bus de direcciones de 32 bits usando 16 líneas y enviando la primera mitad de la dirección de memoria, seguida inmediatamente por la segunda mitad de la dirección de memoria.

Normalmente, se utilizan dos pines adicionales en el bus de control (una luz estroboscópica de dirección de fila (RAS) y una luz estroboscópica de dirección de columna (CAS)) para indicarle a la DRAM si el bus de dirección está enviando actualmente la primera mitad del dirección de memoria o la segunda mitad.

Implementación

Acceder a un byte individual con frecuencia requiere leer o escribir el ancho completo del bus (una palabra) a la vez. En estos casos, es posible que ni siquiera se implementen los bits menos significativos del bus de direcciones; en cambio, es responsabilidad del dispositivo de control aislar el byte individual requerido de la palabra completa transmitida. Este es el caso, por ejemplo, del Bus Local VESA que carece de los dos bits menos significativos, lo que limita este bus a transferencias alineadas de 32 bits.

Históricamente, también hubo algunos ejemplos de computadoras que solo podían abordar palabras: máquinas de palabras.

Bus de memoria

El bus de memoria es el bus que conecta la memoria principal al controlador de memoria en los sistemas informáticos. Originalmente, se utilizaron buses de propósito general como VMEbus y el bus S-100, pero para reducir la latencia, los buses de memoria modernos están diseñados para conectarse directamente a chips DRAM y, por lo tanto, están diseñados por organismos de estándares de chips como JEDEC. Algunos ejemplos son las diversas generaciones de SDRAM y los buses seriales punto a punto como SLDRAM y RDRAM. Una excepción es el DIMM con búfer completo que, a pesar de estar cuidadosamente diseñado para minimizar el efecto, ha sido criticado por su mayor latencia.

Detalles de implementación

Los buses pueden ser buses paralelos, que transportan palabras de datos en paralelo en múltiples cables, o buses seriales, que transportan datos en forma de serie de bits. La adición de conexiones adicionales de alimentación y control, controladores diferenciales y conexiones de datos en cada dirección generalmente significa que la mayoría de los buses seriales tienen más conductores que el mínimo de uno utilizado en 1-Wire y UNI/O. A medida que aumentan las velocidades de datos, los problemas de desviación de tiempo, consumo de energía, interferencia electromagnética y diafonía entre buses paralelos se vuelven cada vez más difíciles de eludir. Una solución parcial a este problema ha sido bombear dos veces el autobús. A menudo, un bus en serie puede funcionar a velocidades de datos generales más altas que un bus en paralelo, a pesar de tener menos conexiones eléctricas, porque un bus en serie inherentemente no tiene desviación de tiempo ni diafonía. USB, FireWire y Serial ATA son ejemplos de esto. Las conexiones multipunto no funcionan bien para los buses seriales rápidos, por lo que la mayoría de los buses seriales modernos utilizan diseños de conexión en cadena o concentrador.

Las conexiones de red como Ethernet generalmente no se consideran buses, aunque la diferencia es más conceptual que práctica. Un atributo generalmente utilizado para caracterizar un bus es que el bus proporciona energía para el hardware conectado. Esto enfatiza los orígenes de la barra de bus de la arquitectura de bus como suministro de energía conmutada o distribuida. Esto excluye, como buses, esquemas como serial RS-232, paralelo Centronics, interfaces IEEE 1284 y Ethernet, ya que estos dispositivos también necesitaban fuentes de alimentación separadas. Los dispositivos de bus serie universal pueden utilizar la alimentación suministrada por el bus, pero a menudo utilizan una fuente de alimentación independiente. Esta distinción se ejemplifica con un sistema telefónico con un módem conectado, donde la conexión RJ11 y el esquema de señalización modulada asociado no se considera un bus y es análogo a una conexión Ethernet. Un esquema de conexión de línea telefónica no se considera un bus con respecto a las señales, pero la Oficina Central utiliza buses con interruptores de barra cruzada para conexiones entre teléfonos.

Sin embargo, esta distinción—que la energía la proporciona el bus—no es el caso en muchos sistemas de aviónica, donde las conexiones de datos como ARINC 429, ARINC 629, MIL-STD-1553B (STANAG 3838) y EFABus (STANAG 3910) se conocen comúnmente como "buses de datos" o, a veces, "buses de datos". Dichos buses de datos de aviónica generalmente se caracterizan por tener varios equipos o elementos/unidades reemplazables en línea (LRI/LRU) conectados a un medio común compartido. Pueden, como ARINC 429, ser simplex, es decir, tener una sola fuente LRI/LRU o, como ARINC 629, MIL-STD-1553B y STANAG 3910, ser dúplex, permitiendo que todos los LRI/LRU conectados actúen, en diferentes tiempos (half dúplex), como transmisores y receptores de datos.

Multiplexación de bus

El bus de sistema más simple tiene líneas de datos de entrada, líneas de datos de salida y líneas de direcciones completamente separadas. Para reducir costos, la mayoría de las microcomputadoras tienen un bus de datos bidireccional, reutilizando los mismos cables para entrada y salida en diferentes momentos.

Algunos procesadores usan un cable dedicado para cada bit del bus de direcciones, el bus de datos y el bus de control. Por ejemplo, el STEbus de 64 pines se compone de 8 cables físicos dedicados al bus de datos de 8 bits, 20 cables físicos dedicados al bus de direcciones de 20 bits, 21 cables físicos dedicados al bus de control y 15 cables físicos dedicados a varios buses de potencia.

La multiplexación de bus requiere menos cables, lo que reduce los costos en muchos de los primeros microprocesadores y chips DRAM. Ya se ha mencionado un esquema común de multiplexación, la multiplexación de direcciones. Otro esquema de multiplexación reutiliza los pines del bus de direcciones como pines del bus de datos, un enfoque utilizado por PCI convencional y el 8086. Los diversos "autobuses en serie" puede verse como el límite máximo de la multiplexación, enviando cada uno de los bits de dirección y cada uno de los bits de datos, uno a la vez, a través de un solo pin (o un solo par diferencial).

Historia

Con el tiempo, varios grupos de personas trabajaron en varios estándares de bus de computadora, incluido el Comité de estándares de arquitectura de bus (BASC) de IEEE, el IEEE "Superbus" grupo de estudio, la iniciativa de microprocesadores abiertos (OMI), la iniciativa de microsistemas abiertos (OMI), la "Gang of Nine" que desarrolló EISA, etc.

Primera generación

Los primeros buses de computadora eran haces de cables que conectaban la memoria y los periféricos de la computadora. Denominados anecdóticamente el "tronco de dígitos", recibieron el nombre de buses de energía eléctrica o barras colectoras. Casi siempre, había un bus para la memoria y uno o más buses separados para los periféricos. A estos se accedía mediante instrucciones separadas, con tiempos y protocolos completamente diferentes.

Una de las primeras complicaciones fue el uso de interrupciones. Los primeros programas de computadora realizaban E/S esperando en un bucle a que el periférico estuviera listo. Esto fue una pérdida de tiempo para los programas que tenían otras tareas que hacer. Además, si el programa intentó realizar esas otras tareas, es posible que el programa tarde demasiado en verificar nuevamente, lo que provocaría la pérdida de datos. Los ingenieros dispusieron así que los periféricos interrumpieran la CPU. Las interrupciones debían priorizarse, porque la CPU solo puede ejecutar código para un periférico a la vez, y algunos dispositivos son más críticos en cuanto al tiempo que otros.

Los sistemas de gama alta introdujeron la idea de los controladores de canal, que eran esencialmente pequeñas computadoras dedicadas a manejar la entrada y la salida de un bus determinado. IBM los introdujo en el IBM 709 en 1958 y se convirtieron en una característica común de sus plataformas. Otros proveedores de alto rendimiento como Control Data Corporation implementaron diseños similares. En general, los controladores de canal harían todo lo posible para ejecutar todas las operaciones del bus internamente, moviendo datos cuando se supiera que la CPU está ocupada en otro lugar si es posible, y solo usando interrupciones cuando sea necesario. Esto redujo considerablemente la carga de la CPU y proporcionó un mejor rendimiento general del sistema.

Para proporcionar modularidad, la memoria y los buses de E/S se pueden combinar en un bus de sistema unificado. En este caso, se puede utilizar un solo sistema mecánico y eléctrico para conectar muchos de los componentes del sistema, o en algunos casos, todos ellos.

Los programas informáticos posteriores comenzaron a compartir la memoria común a varias CPU. También había que priorizar el acceso a este bus de memoria. La forma sencilla de priorizar las interrupciones o el acceso al bus fue con una cadena de margaritas. En este caso, las señales fluirán naturalmente a través del bus en orden físico o lógico, eliminando la necesidad de una programación compleja.

Minis y micros

Digital Equipment Corporation (DEC) redujo aún más el costo de las minicomputadoras producidas en masa y asignó periféricos al bus de memoria, de modo que los dispositivos de entrada y salida parecieran ser ubicaciones de memoria. Esto se implementó en el Unibus del PDP-11 alrededor de 1969.

Los primeros sistemas de bus de microcomputadoras eran esencialmente un backplane pasivo conectado directamente o a través de amplificadores de búfer a los pines de la CPU. La memoria y otros dispositivos se agregarían al bus usando la misma dirección y pines de datos que usó la propia CPU, conectados en paralelo. La comunicación estaba controlada por la CPU, que leía y escribía datos de los dispositivos como si fueran bloques de memoria, usando las mismas instrucciones, todo cronometrado por un reloj central que controlaba la velocidad de la CPU. Aún así, los dispositivos interrumpieron la CPU al señalar en pines de CPU separados.

Por ejemplo, un controlador de unidad de disco indicaría a la CPU que los nuevos datos estaban listos para leerse, momento en el cual la CPU movería los datos leyendo la "ubicación de memoria" que correspondía a la unidad de disco. Casi todas las primeras microcomputadoras se construyeron de esta manera, comenzando con el bus S-100 en el sistema informático Altair 8800.

En algunos casos, sobre todo en la PC de IBM, aunque se puede emplear una arquitectura física similar, las instrucciones para acceder a los periféricos (in y out) y memoria (mov y otros) no se han hecho uniformes en absoluto, y todavía generan distintas señales de CPU, que podrían usarse para implementar un bus de E/S separado.

Estos sistemas de bus simples tenían un serio inconveniente cuando se usaban para computadoras de propósito general. Todos los equipos del autobús debían hablar a la misma velocidad, ya que compartían un mismo reloj.

Aumentar la velocidad de la CPU se vuelve más difícil, porque la velocidad de todos los dispositivos también debe aumentar. Cuando no es práctico o económico tener todos los dispositivos tan rápidos como la CPU, la CPU debe entrar en un estado de espera o trabajar a una frecuencia de reloj más lenta temporalmente para hablar con otros dispositivos en la computadora. Si bien es aceptable en los sistemas integrados, este problema no se toleró durante mucho tiempo en las computadoras de uso general ampliables por el usuario.

Tales sistemas de bus también son difíciles de configurar cuando se construyen a partir de equipos comunes disponibles en el mercado. Por lo general, cada tarjeta de expansión agregada requiere muchos puentes para establecer direcciones de memoria, direcciones de E/S, prioridades de interrupción y números de interrupción.

Segunda generación

"Segunda generación" Los sistemas de bus como NuBus abordaron algunos de estos problemas. Por lo general, separaban la computadora en dos "mundos", la CPU y la memoria en un lado y los diversos dispositivos en el otro. Un controlador de bus aceptaba datos del lado de la CPU para trasladarlos al lado de los periféricos, lo que trasladaba la carga del protocolo de comunicaciones a la propia CPU. Esto permitió que el lado de la CPU y la memoria evolucionaran por separado del bus del dispositivo, o simplemente 'bus'. Los dispositivos en el bus podrían comunicarse entre sí sin intervención de la CPU. Esto condujo a mucho mejor "mundo real" rendimiento, pero también requería que las tarjetas fueran mucho más complejas. Estos autobuses también solían abordar los problemas de velocidad al ser "más grandes" en términos del tamaño de la ruta de datos, pasando de buses paralelos de 8 bits en la primera generación, a 16 o 32 bits en la segunda, además de agregar la configuración del software (ahora estandarizado como Plug-n-play) para suplantar o reemplace los puentes.

Sin embargo, estos nuevos sistemas compartían una cualidad con sus primos anteriores: todos los pasajeros del autobús tenían que hablar a la misma velocidad. Si bien la CPU ahora estaba aislada y podía aumentar la velocidad, las CPU y la memoria continuaron aumentando su velocidad mucho más rápido que los buses con los que hablaban. El resultado fue que las velocidades de los buses ahora eran mucho más lentas de lo que necesitaba un sistema moderno, y las máquinas se quedaron sin datos. Un ejemplo particularmente común de este problema fue que las tarjetas de video superaron rápidamente incluso a los sistemas de bus más nuevos como PCI, y las computadoras comenzaron a incluir AGP solo para controlar la tarjeta de video. En 2004, AGP fue superado nuevamente por tarjetas de video de alta gama y otros periféricos y fue reemplazado por el nuevo bus PCI Express.

Un número cada vez mayor de dispositivos externos también comenzaron a emplear sus propios sistemas de bus. Cuando se introdujeron por primera vez las unidades de disco, se agregarían a la máquina con una tarjeta conectada al bus, razón por la cual las computadoras tienen tantas ranuras en el bus. Pero durante las décadas de 1980 y 1990, se introdujeron nuevos sistemas como SCSI e IDE para satisfacer esta necesidad, dejando vacías la mayoría de las ranuras en los sistemas modernos. Hoy en día, es probable que haya alrededor de cinco buses diferentes en la máquina típica, que admitan varios dispositivos.

Tercera generación

"Tercera generación" Los autobuses han estado surgiendo en el mercado desde aproximadamente 2001, incluidos HyperTransport e InfiniBand. También tienden a ser muy flexibles en términos de sus conexiones físicas, lo que les permite usarse tanto como buses internos como para conectar diferentes máquinas entre sí. Esto puede generar problemas complejos cuando se trata de atender diferentes solicitudes, por lo que gran parte del trabajo en estos sistemas se relaciona con el diseño del software, a diferencia del hardware en sí. En general, estos buses de tercera generación tienden a parecerse más a una red que al concepto original de un bus, con una sobrecarga de protocolo más alta que los primeros sistemas, al mismo tiempo que permite que múltiples dispositivos usen el bus a la vez.

Los buses como Wishbone han sido desarrollados por el movimiento de hardware de código abierto en un intento de eliminar aún más las restricciones legales y de patentes del diseño de computadoras.

Compute Express Link (CXL) es una interconexión de estándar abierto para CPU a dispositivo y CPU a memoria de alta velocidad, diseñada para acelerar el rendimiento del centro de datos de próxima generación.

Ejemplos de buses internos de computadora

Paralelo

- Asus Media Propietario de autobús, utilizado en algunas placas madre Asus Socket 7

- Medición y control automatizados (CAMAC) para sistemas de instrumentación

- ISA ampliada o EISA

- Arquitectura estándar de la industria o ISA

- Bajo conteo de pins o LPC

- MBus

- Microcámara o MCA

- Multibus para sistemas industriales

- NuBus o IEEE 1196

- Autobús local OPTi usado en las placas madre Intel 80486 tempranas.

- PCI convencional

- Parallel ATA (también conocido como Tecnología Avanzada Attachment, ATA, PATA, IDE, EIDE, ATAPI, etc.), unidad de disco duro, unidad de disco óptico, unidad de cinta bus adjunto periférico

- bus S-100 o IEEE 696, utilizado en el Altair 8800 y microcomputadoras similares

- SBus o IEEE 1496

- Autobús SS-50

- Bus de pista, un bus CPU de lado frontal propietario desarrollado por Hewlett-Packard para su familia de microprocesadores PA-RISC

- GSC/HSC, un bus periférico patentado desarrollado por Hewlett-Packard para su familia de microprocesadores PA-RISC

- Precision Bus, un autobús propietario desarrollado por Hewlett-Packard para su uso por su familia informática HP3000

- STEbus

- STD Bus (for STD-80 [8-bit] y STD32 [16-/32-bit]), FAQ Archivado 2012-02-27 en la máquina Wayback

- Unibus, un autobús propietario desarrollado por Digital Equipment Corporation para sus ordenadores PDP-11 y VAX temprano.

- Q-Bus, un bus patentado desarrollado por Digital Equipment Corporation para su PDP y posteriormente las computadoras VAX.

- VESA Bus local o VLB o VL-bus

- VMEbus, el autobús VERSAmodule Eurocard

- PC/104

- PC/104-Plus

- PCI-104

- PCI/104-Express

- PCI/104

- Zorro II y Zorro III, utilizados en los sistemas informáticos de Amiga

Serie

- 1-Wire

- HyperTransport

- I2C

- I3C (bus)

- SLIMbus

- PCI Express o PCIe

- ATA de serie (SATA), unidad de disco duro, unidad de estado sólido, unidad de disco óptico, unidad de cinta

- Autobús de interfaz periférica serie (SPI)

- UNI/O

- SMBus

Ejemplos de buses de computadoras externas

Paralelo

- Interfaz de alto rendimiento de HIPPI

- IEEE-488 (también conocido como GPIB, Bus Interfaz General-Purpose, y HPIB, Hewlett-Packard Instrumentation Bus)

- PC Tarjeta, anteriormente conocida como PCMCIA, mucho utilizado en ordenadores portátiles y otros portátiles, pero desvaneciendo con la introducción de conexiones USB y de red integrada y módem

Serie

- Enlace de cámara

- CAN bus ("Red de área de control")

- eSATA

- ExpressCard

- Fieldbus

- Interfaz IEEE 1394 (FireWire)

- RS-232

- RS-485

- Thunderbolt

- USB

Ejemplos de buses de computadora internos/externos

- Futurebus

- InfiniBand

- PCI Express cabina externa

- QuickRing

- Scalable Coherent Interface (SCI)

- Interfaz del sistema informático pequeño (SCSI), unidad de disco duro y unidad de cinta del bus adjunto periférico

- Serial Acoplado SCSI (SAS) y otros autobuses serie SCSI

- Thunderbolt

- Yapbus, un autobús propietario desarrollado para el ordenador de imagen Pixar

Contenido relacionado

Búsqueda lineal

IRQ

Cuchillo de uso