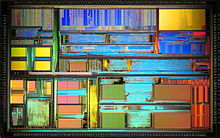

AMD K5

El K5 es el primer procesador x86 de AMD desarrollado íntegramente internamente. Introducido en marzo de 1996, su principal competencia era el microprocesador Pentium de Intel. El K5 tenía un diseño ambicioso, más cercano a un Pentium Pro que a un Pentium en cuanto a soluciones técnicas y arquitectura interna. Sin embargo, el producto final estaba más cerca del Pentium en cuanto a rendimiento, aunque más rápido reloj por reloj en comparación con el Pentium.

Detalles técnicos

El K5 se basó en una arquitectura de procesador RISC interna altamente paralela con una interfaz de decodificación x86. El K5 ofrecía una buena compatibilidad con x86 y el conjunto de pruebas desarrollado internamente resultó invaluable en proyectos posteriores. Todos los modelos tenían 4,3 millones de transistores, con cinco unidades de números enteros que podían procesar instrucciones desordenadas y una unidad de punto flotante. El buffer de destino de la rama era cuatro veces el tamaño del Pentium y el cambio de nombre de los registros ayudó a superar las dependencias de los registros. La ejecución especulativa de instrucciones del chip redujo las paradas en el oleoducto. Tenía un caché de instrucciones asociativo de cuatro vías de 16 KB y un caché de datos de 8 KB. Se probaron mecánicamente la división de coma flotante y el microcódigo de raíz cuadrada. Las instrucciones trascendentales de punto flotante se implementaron en hardware y fueron fieles a resultados matemáticos verdaderos para todos los operandos.

Rendimiento

El proyecto K5 representó una primera oportunidad para que AMD tomara el liderazgo técnico de Intel. Aunque el chip abordó los conceptos de diseño correctos, la implementación de ingeniería real tuvo sus problemas. Las bajas velocidades de reloj se debieron, en parte, a las limitaciones de AMD como software de "vanguardia" empresa de fabricación en ese momento, y en parte debido al diseño en sí, que tenía muchos niveles de lógica para la tecnología de proceso de la época, lo que dificultaba el escalado del reloj. Además, si bien el rendimiento de punto flotante del K5 se consideraba superior al del Cyrix 6x86, era más lento que el del Pentium, aunque ofrecía resultados de funciones trascendentales más confiables. Debido a que llegó tarde al mercado y no cumplió con las expectativas de rendimiento, el K5 nunca obtuvo la aceptación entre los grandes fabricantes de computadoras de la que disfrutaron el anterior Am486 y el posterior AMD K6.

Características

Modelos

Hubo dos revisiones de la arquitectura K5, llamadas internamente SSA/5 y 5k86, ambas lanzadas con la etiqueta K5. El conjunto original de "SSA/5" Las CPU tenían su unidad de predicción de rama deshabilitada y se agregaron estados de espera internos adicionales; Estos problemas se solucionaron con el "5k86", lo que resultó en un rendimiento hasta un 30% mejor reloj por reloj. El "SSA/5" la línea iba de 75 a 100 MHz; el "5k86" La línea iba de 90 a 133 MHz. Sin embargo, AMD utilizó lo que llamó calificación PR, o calificación de rendimiento, para etiquetar los chips según su equivalencia sugerida en rendimiento entero con un Pentium de esa velocidad de reloj. Así, un chip de 116 MHz de la segunda línea se comercializó como "K5 PR166". Los retrasos en la fabricación provocaron que la llegada del PR200 casi se alineara con el lanzamiento del K6. Como AMD no quería que los dos chips compitieran, el K5-PR200 llegó sólo en pequeñas cantidades.

SSA/5

- Vendido 5K86 P75 a P100, más tarde K5 PR75 a PR100

- 4.3 millones de transistores en 500 o 350 nm

- L1-Cache: 8 + 16 KB (datos + instrucciones)

- Socket 5 y Socket 7

- VCore: 3.52 V

- Autobús lateral frontal: 50 (PR75), 60 (PR90), 66 MHz (PR100)

- Primera liberación: 27 de marzo de 1996

- Reloj: 75, 90, 100 MHz

5k86

- Vendido K5 PR120 a PR166; más tarde PR200

- 4.3 millones de transistores en 350 nm

- L1-Cache: 8 + 16 KB (datos + instrucciones)

- Socket 5 y Socket 7

- VCore: 3.52 V

- bus lateral frontal: 60 (PR120/150), 66 MHz

- Primera publicación: 7 de octubre de 1996

- Reloj: 90 (PR120), 100 (PR133), 105 (PR150), 116.6 (PR166), 133 MHz (PR200)