Pentium (original)

O Pentium (também conhecido como P5, sua microarquitetura ou i586) é um microprocessador x86 de 32 bits de quinta geração que foi introduzido pela Intel em 22 de março de 1993, como o primeiro processador da marca Pentium. Era um conjunto de instruções compatível com o 80486, mas era um projeto de microarquitetura novo e muito diferente das iterações anteriores. O P5 Pentium foi a primeira microarquitetura superescalar x86 e o primeiro microprocessador superescalar do mundo a ser produzido em massa - o que significa que geralmente executa pelo menos 2 instruções por clock, principalmente por causa de um design de pipeline de inteiro duplo antes considerado impossível de ser executado. implementar em uma microarquitetura CISC. Recursos adicionais incluem uma unidade de ponto flutuante mais rápida, barramento de dados mais amplo, código separado e caches de dados e muitas outras técnicas e recursos para melhorar o desempenho e dar suporte à segurança, criptografia e multiprocessamento para estações de trabalho e servidores em comparação com os melhores do mercado anterior. implementação de processador padrão antes dele, o Intel 80486.

Considerada a quinta geração principal na linha de processadores compatíveis com 8086, sua implementação e microarquitetura foi denominada P5. Como acontece com todos os novos processadores da Intel desde o Pentium, algumas novas instruções foram adicionadas para melhorar o desempenho de tipos específicos de cargas de trabalho.

O Pentium foi o primeiro Intel x86 a incorporar suporte de hardware robusto para multiprocessamento semelhante ao dos grandes mainframes IBM. A Intel trabalhou em estreita colaboração com a IBM para definir essa capacidade e, em seguida, a Intel a projetou na microarquitetura P5. Essa nova capacidade estava ausente nas gerações x86 anteriores e nas cópias x86 dos concorrentes.

Para realizar seu maior potencial, os compiladores tiveram que ser otimizados para explorar o paralelismo de nível de instrução fornecido pelos novos pipelines duplos superescalares e os aplicativos precisavam ser recompilados. A Intel gastou esforços e recursos substanciais trabalhando com fornecedores de ferramentas de desenvolvimento e grandes fornecedores independentes de software (ISV) e empresas de sistemas operacionais (SO) para otimizar seus produtos para Pentium antes do lançamento do produto.

Em outubro de 1996, o similar Pentium MMX foi lançado, complementando a mesma microarquitetura básica com o conjunto de instruções MMX, caches maiores e algumas outras melhorias.

Os concorrentes incluíram o Motorola 68040, Motorola 68060, PowerPC 601 e as famílias SPARC, MIPS e Alpha, a maioria das quais também usou uma configuração de pipeline de instrução dupla em ordem superescalar em algum momento.

A Intel descontinuou os processadores P5 Pentium (vendidos como um produto mais barato desde o lançamento do Pentium II em 1997) no início de 2000 em favor do processador Celeron, que também substituiu a marca 80486.

Desenvolvimento

A microarquitetura do P5 foi projetada pela mesma equipe de Santa Clara que projetou o 386 e o 486. O trabalho de projeto começou em 1989; a equipe decidiu usar uma arquitetura superescalar, com cache no chip, ponto flutuante e previsão de ramificação. O projeto preliminar foi simulado pela primeira vez com sucesso em 1990, seguido pelo layout do projeto. A essa altura, a equipe tinha várias dezenas de engenheiros. O projeto foi gravado, ou transferido para silício, em abril de 1992, quando o teste beta começou. Em meados de 1992, a equipe P5 tinha 200 engenheiros. A Intel planejou inicialmente demonstrar o P5 em junho de 1992 na feira PC Expo e anunciar formalmente o processador em setembro de 1992, mas problemas de design forçaram o cancelamento da demonstração e a introdução oficial do chip foi adiada até a primavera. de 1993.

John H. Crawford, arquiteto-chefe do 386 original, cogerenciou o projeto do P5, juntamente com Donald Alpert, que gerenciou a equipe de arquitetura. Dror Avnon gerenciou o projeto da FPU. Vinod K. Dham era gerente geral do grupo P5.

O projeto de arquitetura multicore Larrabee da Intel usa um núcleo de processador derivado de um núcleo P5 (P54C), aumentado por multithreading, instruções de 64 bits e uma unidade de processamento vetorial de 16 larguras. A microarquitetura Bonnell de baixa potência da Intel empregada nos primeiros núcleos do processador Atom também usa um pipeline duplo em ordem semelhante ao P5.

A Intel usou o nome Pentium em vez de 80586, porque descobriu que os números não podem ser registrados.

Melhorias em relação ao i486

A microarquitetura P5 traz vários avanços importantes em relação à arquitetura i486 anterior.

- Desempenho:

- Arquitetura Superscalar – O Pentium tem dois datapaths (pipelines) que permitem completar duas instruções por ciclo de relógio em muitos casos. O tubo principal (U) pode lidar com qualquer instrução, enquanto o outro (V) pode lidar com as instruções simples mais comuns. Alguns proponentes reduzidos do computador (RISC) argumentaram que o conjunto de instrução x86 "complicado" provavelmente nunca seria implementado por uma microarquitetura firmemente encanada, muito menos por um projeto dual-pipeline. O 486 e o Pentium demonstraram que isso era realmente possível e viável.

- O databus externo de 64 bits duplica a quantidade de informação possível para ler ou escrever em cada acesso de memória e, portanto, permite que o Pentium carregue seu cache de código mais rápido do que o 80486; também permite acesso e armazenamento mais rápido de dados FPU de 64 bits e 80 bits.

- A separação de caches de código e dados diminui os conflitos de busca e de leitura/escrita em relação ao 486. Para reduzir o tempo de acesso e o custo de implementação, ambos são associativos de 2 vias, em vez do único cache de 4 vias do 486. Um realce relacionado no Pentium é a capacidade de ler um bloco contíguo do cache de código mesmo quando é dividido entre duas linhas de cache (pelo menos 17 bytes no pior dos casos).

- Unidade de ponto flutuante muito mais rápida. Algumas instruções mostraram uma enorme melhoria, mais notavelmente FMUL, com até 15 vezes maior produtividade do que na FPU 80486. O Pentium também é capaz de executar uma instrução FXCH ST (x) em paralelo com uma instrução FPU (aritmética ou carga/loja).

- Adições de endereço de quatro entradas permite que o Pentium reduza ainda mais a latência de cálculo de endereço em comparação com o 80486. O Pentium pode calcular modos de endereçamento completos com segmento-base + registo de base + registo dimensionado + deslocamento imediato em um único ciclo; o 486 tem apenas um adder de endereço de três entradas, e deve, portanto, dividir tais cálculos entre dois ciclos.

- O microcódigo pode empregar ambos os pipelines para permitir instruções de reprodução automática, tais como REP MOVSW executar uma iteração a cada ciclo do relógio, enquanto o 80486 precisava de três relógios por iteração (e as primeiras fichas x86 significativamente mais do que o 486). Além disso, a otimização do acesso às primeiras palavras de microcódigo durante as etapas de decodificação ajuda a fazer várias instruções frequentes executar significativamente mais rapidamente, especialmente em suas formas mais comuns e em casos típicos. Alguns exemplos são (486→Pentium, em ciclos de relógio): CALL (3→1), RET (5→2), turnos/rotatos (2-3→1).

- Um multiplicador mais rápido e totalmente baseado em hardware faz instruções como MUL e IMUL várias vezes mais rápido (e mais previsível) do que no 80486; o tempo de execução é reduzido de 13 a 42 ciclos de clock até 10-11 para operandos de 32 bits.

- Interrupção virtualizada para acelerar o modo 8086 virtual.

- Previsão do ramo

- Outras características:

- Recursos de depuração aprimorados com a introdução da porta de depuração baseada no processador (veja Processador de Pentium Depuração no Manual de Desenvolvedores, Vol 1).

- Recursos aprimorados do self-test como a verificação de paridade de cache L1 (veja Estrutura de Cache no Manual de Desenvolvedores, Vol 1).

- Novas instruções: CPUID, CMPXCHG8B, RDTSC, RDMSR, WRMSR, RSM.

- Os registros de testes TR0–TR7 e as instruções MOV para acesso a eles foram eliminadas.

- O mais tarde Pentium MMX também adicionou o conjunto de instrução MMX, um inteiro básico instrução única, múltiplos dados (SIMD) instrução definir extensão comercializada para uso em aplicações multimídia. MMX não poderia ser usado simultaneamente com as instruções de FPU x87 porque os registros foram reutilizados (para permitir interruptores de contexto rápidos). Melhorias mais importantes foram a duplicação dos tamanhos de instrução e cache de dados e algumas alterações microarquitecturas para melhor desempenho.

O Pentium foi projetado para executar mais de 100 milhões de instruções por segundo (MIPS), e o modelo de 75 MHz conseguiu atingir 126,5 MIPS em determinados benchmarks. A arquitetura Pentium normalmente oferecia pouco menos que o dobro do desempenho de um processador 486 por ciclo de clock em benchmarks comuns. As partes 80486 mais rápidas (com microarquitetura ligeiramente aprimorada e operação de 100 MHz) eram quase tão poderosas quanto os Pentiums de primeira geração, e o AMD Am5x86, que apesar do nome é na verdade uma CPU de classe 486, era aproximadamente igual ao Pentium 75 em relação desempenho ALU puro.

Errata

As primeiras versões dos Pentiums P5 de 60 a 100 MHz apresentavam um problema na unidade de ponto flutuante que resultava em resultados incorretos (mas previsíveis) de algumas operações de divisão. Essa falha, descoberta em 1994 pelo professor Thomas Nicely do Lynchburg College, na Virgínia, ficou conhecida como bug do Pentium FDIV e causou constrangimento para a Intel, que criou um programa de troca para substituir os processadores defeituosos.

Em 1997, foi descoberta outra errata que poderia permitir que um programa malicioso travasse um sistema sem nenhum privilégio especial, o "F00F bug". Todos os processadores da série P5 foram afetados e nenhuma revisão corrigida foi lançada, no entanto, os sistemas operacionais contemporâneos foram corrigidos com soluções alternativas para evitar falhas.

Núcleos e etapas

O Pentium foi o principal microprocessador da Intel para computadores pessoais em meados da década de 1990. O projeto original foi reimplantado em novos processos e novas funcionalidades foram adicionadas para manter sua competitividade e atender a mercados específicos como o de computadores portáteis. Como resultado, surgiram diversas variantes da microarquitetura P5.

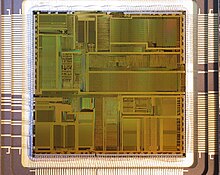

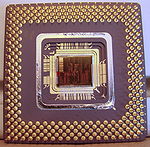

P5

O primeiro núcleo do microprocessador Pentium recebeu o codinome "P5". Seu código de produto era 80501 (80500 para os primeiros passos Q0399). Havia duas versões, especificadas para operar a 60 MHz e 66 MHz, respectivamente, usando o soquete 4. Esta primeira implementação do Pentium usava uma fonte de alimentação tradicional de 5 volts (descendente dos requisitos de compatibilidade de lógica transistor-transistor (TTL) usual). Ele continha 3,1 milhões de transistores e media 16,7 mm por 17,6 mm para uma área de 293,92 mm2. Foi fabricado em um processo bipolar de metal-óxido-semicondutor (BiCMOS) de 0,8 μm. O design de 5 volts resultou em consumo de energia relativamente alto para sua frequência operacional quando comparado aos modelos diretamente a seguir.

P54C

O P5 foi seguido pelo P54C (80502) em 1994, com versões especificadas para operar em 75, 90 ou 100 MHz usando uma fonte de alimentação de 3,3 volts. Marcando a mudança para o soquete 5, este foi o primeiro processador Pentium a operar em 3,3 volts, reduzindo o consumo de energia, mas necessitando de regulação de tensão nas placas-mãe. Assim como nos processadores 486 com clock mais alto, um multiplicador de clock interno foi empregado daqui em diante para permitir que o circuito interno funcione em uma frequência mais alta do que o endereço externo e os barramentos de dados, pois é mais complicado e incômodo aumentar a frequência externa, devido a restrições físicas. Ele também permitia o multiprocessamento bidirecional e tinha um APIC local integrado e novos recursos de gerenciamento de energia. Ele continha 3,3 milhões de transistores e media 163 mm2. Foi fabricado em um processo BiCMOS que foi descrito como 0,5 μm e 0,6 μm devido a diferentes definições.

P54CQS

O P54C foi seguido pelo P54CQS no início de 1995, que operava a 120 MHz. Foi fabricado em um processo BiCMOS de 0,35 μm e foi o primeiro microprocessador comercial a ser fabricado em um processo de 0,35 μm. Sua contagem de transistores é idêntica à do P54C e, apesar do processo mais recente, ele também tinha uma área de matriz idêntica. O chip foi conectado ao encapsulamento usando wire bonding, que só permite conexões ao longo das bordas do chip. Um chip menor exigiria um redesenho do encapsulamento, pois há um limite no comprimento dos fios e as bordas do chip estariam mais distantes das almofadas do encapsulamento. A solução foi manter o chip do mesmo tamanho, reter o pad-ring existente e apenas reduzir o tamanho do circuito lógico do Pentium para permitir que ele atinja frequências de clock mais altas.

P54CS

O P54CQS foi rapidamente seguido pelo P54CS, que operava em 133, 150, 166 e 200 MHz, e introduziu o soquete 7. Ele continha 3,3 milhões de transistores, media 90 mm2 e foi fabricado em um processo BiCMOS de 0,35 μm com quatro níveis de interconexão.

P24T

Os sistemas P24T Pentium OverDrive para 486 foram lançados em 1995, baseados em versões de 3,3 V 0,6 μm usando um clock de 63 ou 83 MHz. Como eles usavam soquete 2/3, algumas modificações tiveram que ser feitas para compensar o barramento de dados de 32 bits e o cache L2 on-board mais lento das placas-mãe 486. Eles foram, portanto, equipados com um cache L1 de 32 KB (o dobro dos processadores Pentium pré-P55C).

P55C

O P55C (ou 80503) foi desenvolvido pela Intel's Research & Centro de Desenvolvimento em Haifa, Israel. Foi vendido como Pentium com tecnologia MMX (normalmente chamado apenas de Pentium MMX); embora fosse baseado no núcleo P5, apresentava um novo conjunto de 57 "MMX" instruções destinadas a melhorar o desempenho em tarefas multimídia, como codificação e decodificação de dados de mídia digital. A linha Pentium MMX foi lançada em 22 de outubro de 1996 e lançada em janeiro de 1997.

As novas instruções funcionavam em novos tipos de dados: vetores compactados de 64 bits de oito inteiros de 8 bits, quatro inteiros de 16 bits, dois inteiros de 32 bits ou um inteiro de 64 bits. Assim, por exemplo, a instrução PADDUSB (Packed ADD Unsigned Saturated Byte) adiciona dois vetores, cada um contendo oito inteiros não assinados de 8 bits juntos, elemento a elemento; cada adição que transbordaria satura, resultando em 255, o valor máximo sem sinal que pode ser representado em um byte. Essas instruções bastante especializadas geralmente requerem codificação especial pelo programador para serem usadas.

Outras mudanças no núcleo incluem um pipeline de 6 estágios (vs. 5 no P5) com uma pilha de retorno (primeiro feito no Cyrix 6x86) e melhor paralelismo, um decodificador de instrução aprimorado, cache de dados L1 de 16 KB + cache de instrução L1 de 16 KB com associatividade de 4 vias (vs. 8KB L1 Dados/instrução com 2 vias em P5), 4 buffers de gravação que agora podem ser usados por qualquer pipeline (vs. um correspondente a cada pipeline em P5) e um preditor de ramificação aprimorado do Pentium Pro, com um buffer de 512 entradas (vs. 256 no P5).

Continha 4,5 milhões de transistores e tinha uma área de 140 mm2. Ele foi fabricado em um processo CMOS de 0,28 μm com os mesmos passos de metal do processo BiCMOS de 0,35 μm anterior, então a Intel o descreveu como "0,35 μm" por causa de sua densidade de transistor semelhante. O processo tem quatro níveis de interconexão.

Embora o P55C tenha permanecido compatível com o soquete 7, os requisitos de tensão para alimentar o chip diferem das especificações do soquete 7 padrão. A maioria das placas-mãe fabricadas para soquete 7 antes do estabelecimento do padrão P55C não são compatíveis com o trilho de voltagem dupla necessário para a operação adequada desta CPU (voltagem de núcleo de 2,8 volts, voltagem de entrada/saída (I/O) de 3,3 volts). A Intel resolveu o problema com os kits de atualização do OverDrive que apresentavam um intermediário com sua própria regulação de voltagem.

Tillamook

As CPUs de notebooks Pentium MMX usavam um módulo móvel que continha a CPU. Este módulo era uma placa de circuito impresso (PCB) com a CPU diretamente conectada a ela em um fator de forma menor. O módulo se encaixava na placa-mãe do notebook e normalmente um dissipador de calor era instalado e entrava em contato com o módulo. No entanto, com o Tillamook Mobile Pentium MMX de 0,25 μm (em homenagem a uma cidade no Oregon), o módulo também continha o chipset 430TX junto com a memória estática de acesso aleatório de 512 KB do sistema (SRAM) memória cache.

Modelos e variantes

| Nome do código | P54CTB | ||||||

|---|---|---|---|---|---|---|---|

| Código do produto | PODPMT60X150 | PODPMT66X166 | POLÍTICA DE CONCORRÊNCIA | PODPMT66X200 | |||

| Tamanho do processo (μm) | 0,35 | ||||||

| Soquete | Soquete 5/7 | ||||||

| Pacote | CPGA com dissipador de calor, ventilador e regulador de tensão | ||||||

| Velocidade do relógio (MHz) | 125 | 150 | 166 | 150 | 180 | 200 | |

| Velocidade do autocarro (MHz) | 50 | 60 | 66 | 50 | 60 | 66 | |

| Atualização para | Pentium 75 | Pentium 90 | Pentium 100 e 133 | Pentium 75 | Pentium 90, 120 e 150 | Pentium 100, 133 e 166 | |

| TDP (max. W) | 15.6 | 15.6 | 15.6 | 18. | |||

| Tensão | 3.3 | 3.3 | 3.3 | 3.3 | |||

| Nome do código | P55C | Tillamook | |||||

|---|---|---|---|---|---|---|---|

| Código do produto | FV8050366200 | FV8050366233 | FV80503CSM66166 | GC80503CSM66166 | GC80503CS166EXT | FV80503CSM66266 | GC80503CSM66266 |

| Tamanho do processo (μm) | 0,35 | 0,25 | |||||

| Velocidade do relógio (MHz) | 200 | 233 | 166 | 166 | 166 | 266 | 266 |

| Velocidade do autocarro (MHz) | 66 | 66 | 66 | 66 | 66 | 66 | 66 |

| Pacote | PPGA | PPGA | PPGA | BGA | BGA | PPGA | BGA |

| TDP (max. W) | 15.7 | 17. | 4,5 | 4.1 | 4.1 | 7.6 | 7.6 |

| Tensão | 2. | 2. | 1. | 1. | 1. | 1. | 2.0 |

Concorrentes

Depois da introdução do Pentium, concorrentes como NexGen, AMD, Cyrix e Texas Instruments anunciaram processadores compatíveis com Pentium em 1994. A revista CIO identificou o Nx586 da NexGen como o primeiro Pentium -CPU compatível, enquanto a PC Magazine descreveu o Cyrix 6x86 como o primeiro. Estes foram seguidos pelo AMD K5, que foi atrasado devido a dificuldades de design. Mais tarde, a AMD comprou a NexGen para ajudar a projetar o AMD K6, e a Cyrix foi comprada pela National Semiconductor. Processadores posteriores da AMD e da Intel mantêm a compatibilidade com o Pentium original.

Lista

- AMD K5, AMD K6

- Cyrix 6x86

- WinChip C6

- NexGen Nx586

- Rise mP6

Contenido relacionado

Computador Atanasoff-Berry

Detecção e correção de erros

Código Baudot

Arquivo de computador

Sistema operacional de disco