PDP-8

O PDP-8 é um minicomputador de 12 bits produzido pela Digital Equipment Corporation (DEC). Foi o primeiro minicomputador de sucesso comercial, com mais de 50.000 unidades vendidas durante a vida útil do modelo. Seu projeto básico segue o pioneiro LINC, mas possui um conjunto de instruções menor, que é uma versão expandida do conjunto de instruções PDP-5. Máquinas similares da DEC são o PDP-12, que é uma versão modernizada dos conceitos PDP-8 e LINC, e o sistema controlador industrial PDP-14.

Visão geral

O modelo PDP-8 mais antigo, informalmente conhecido como "Straight-8", foi lançado em 22 de março de 1965 ao preço de $ 18.500 (equivalente a cerca de $ 170.000 em 2022). Ele usava a lógica diodo-transistor empacotada em cartões flip-chip em uma máquina do tamanho de uma pequena geladeira doméstica. Foi o primeiro computador a ser vendido por menos de $ 20.000, tornando-se o computador mais vendido da história na época. O Straight-8 foi suplantado em 1966 pelo PDP-8/S, que estava disponível em modelos de mesa e de montagem em rack. O uso de uma unidade lógica aritmética serial (ALU) de um bit permitiu que o PDP-8/S fosse menor e mais barato, embora mais lento que o PDP-8 original. Um 8/S básico foi vendido por menos de US$ 10.000, a primeira máquina a atingir esse marco.

Sistemas posteriores (o PDP-8/I e /L, o PDP-8/E, /F e /M e o PDP-8/A) retornaram a uma implementação mais rápida e totalmente paralela, mas usam muito menos dispendiosa lógica transistor-transistor (TTL) lógica MSI. A maioria dos PDP-8 sobreviventes são desta época. O PDP-8/E é comum e bem visto porque muitos tipos de dispositivos de E/S estavam disponíveis para ele. Os últimos modelos PDP-8 comerciais lançados em 1979 são chamados de "CMOS-8s", baseados em microprocessadores CMOS. Eles não tinham preços competitivos e a oferta falhou. A Intersil vendeu os circuitos integrados comercialmente até 1982 como a família Intersil 6100. Em virtude de sua tecnologia CMOS, eles tinham baixos requisitos de energia e eram usados em alguns sistemas militares embarcados.

O engenheiro-chefe que projetou a versão inicial do PDP-8 foi Edson de Castro, que mais tarde fundou a Data General.

Significado arquitetônico

O PDP-8 combina baixo custo, simplicidade, capacidade de expansão e engenharia cuidadosa para agregar valor. O maior significado histórico foi que o baixo custo e o alto volume do PDP-8 tornaram um computador disponível para muitos novos clientes para muitos novos usos. Seu significado contínuo é como um exemplo histórico de design de computador com engenharia de valor.

A baixa complexidade trouxe outros custos. Tornou a programação incômoda, como pode ser visto nos exemplos deste artigo e na discussão de "páginas" e "campos". Grande parte do código de uma pessoa executou a mecânica necessária, em vez de definir o algoritmo. Por exemplo, subtrair um número envolve calcular seu complemento de dois e adicioná-lo; escrever um salto condicional envolve escrever um salto condicional em torno do salto, o salto codificando a condição negativa para a desejada. Alguns projetos de programação ambiciosos falharam em caber na memória ou desenvolveram defeitos de design que não puderam ser resolvidos. Por exemplo, conforme observado abaixo, a recursão inadvertida de uma sub-rotina produz defeitos que são difíceis de rastrear para a sub-rotina em questão.

Conforme os avanços do design reduziram os custos de lógica e memória, o tempo do programador tornou-se relativamente mais importante. Os projetos de computador subsequentes enfatizaram a facilidade de programação, normalmente usando conjuntos de instruções maiores e mais intuitivos.

Eventualmente, a maior parte do código de máquina foi gerada por compiladores e geradores de relatórios. O computador com conjunto de instruções reduzido retornou ao círculo completo para a ênfase do PDP-8 em um conjunto de instruções simples e alcançando várias ações em um único ciclo de instrução, a fim de maximizar a velocidade de execução, embora os computadores mais novos tenham palavras de instrução muito mais longas..

Descrição

O PDP-8 usou ideias de vários predecessores de 12 bits, como o LINC projetado por W.A. Clark e C.E. Molnar, que foram inspirados pelo minicomputador CDC 160 de Seymour Cray.

O PDP-8 usa 12 bits para seu tamanho de palavra e aritmética (em inteiros sem sinal de 0 a 4095 ou inteiros com sinal de -2048 a +2047). No entanto, o software pode fazer aritmética de precisão múltipla. Um interpretador estava disponível para operações de ponto flutuante, por exemplo, que usa uma representação de ponto flutuante de 36 bits com um significando de duas palavras (24 bits) (mantissa) e um expoente de uma palavra. Sujeito a limitações de velocidade e memória, o PDP-8 pode realizar cálculos semelhantes aos computadores eletrônicos contemporâneos mais caros, como o IBM 1130 e vários modelos do IBM System/360, sendo mais fácil de interagir com dispositivos externos.

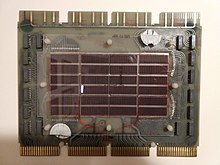

O espaço de endereço de memória também é de 12 bits, então a configuração básica do PDP-8 tem uma memória principal de 4.096 (212) palavras de doze bits, ou 6 kB no moderno termos. Uma unidade de expansão de memória opcional pode alternar bancos de memórias usando uma instrução IOT. A memória é uma memória de núcleo magnético com um tempo de ciclo de 1,5 microssegundos (0,667 MHz), de modo que uma instrução típica de referência de memória de dois ciclos (Buscar, Executar) é executada a uma velocidade de 0,333 MIPS. O Pocket Reference Card de 1974 para o PDP-8/E fornece um tempo de instrução básico de 1,2 microssegundos ou 2,6 microssegundos para instruções que fazem referência à memória.

O PDP-8 foi projetado em parte para lidar com telecomunicações e texto contemporâneos. Os códigos de caracteres de seis bits estavam em uso generalizado na época, e as palavras de doze bits do PDP-8 podem armazenar com eficiência dois desses caracteres. Além disso, um código de teleimpressora de seis bits chamado de telecomposição ou código TTS estava em uso generalizado pelos serviços de notícias, e um dos primeiros aplicativos para o PDP-8 era a composição usando esse código.

As instruções PDP-8 têm um opcode de 3 bits, portanto, há apenas oito instruções. O montador fornece mais instruções mnemônicas para um programador, traduzindo I/O e instruções do modo de operação para combinações de códigos operacionais e campos de instrução. Ele também possui apenas três registradores visíveis ao programador: um acumulador de 12 bits (AC), um contador de programa (PC) e um sinalizador de transporte chamado "registrador de link" (EU).

Para entrada e saída, o PDP-8 possui uma única interrupção compartilhada por todos os dispositivos, um barramento de E/S acessado por instruções de E/S e um canal de acesso direto à memória (DMA). O barramento de E/S programado normalmente opera em periféricos de baixa a média velocidade, como impressoras, teletipos, furadores de fita de papel e leitores, enquanto o DMA é usado para telas de tubo de raios catódicos com caneta óptica, conversores analógico-digitais, conversores digitais -para conversores analógicos, unidades de fita e unidades de disco.

Para economizar dinheiro, o projeto usa memória principal barata para muitos propósitos que são atendidos por registradores flip-flop mais caros em outros computadores, como contadores auxiliares e ligação de sub-rotina.

Modelos básicos usam software para fazer multiplicação e divisão. Para uma matemática mais rápida, o Extended Arithmetic Element (EAE) fornece instruções de multiplicação e divisão com um registrador adicional, o registrador Multiplicador/Quociente (MQ). O EAE era uma opção no PDP-8 original, no 8/I e no 8/E, mas é parte integrante do microprocessador Intersil 6100.

O PDP-8 é otimizado para simplicidade de design. Em comparação com máquinas mais complexas, recursos desnecessários foram removidos e a lógica é compartilhada quando possível. As instruções usam incremento automático, limpeza automática e acesso indireto para aumentar a velocidade do software, reduzir o uso de memória e substituir registradores caros por memória barata.

A eletrônica de uma CPU PDP-8 básica tem apenas quatro registradores de 12 bits: o acumulador, o contador de programa, o registrador de buffer de memória e o registrador de endereço de memória. Para economizar dinheiro, eles serviram a vários propósitos em diferentes pontos do ciclo operacional. Por exemplo, o registrador de buffer de memória fornece operandos aritméticos, faz parte do registrador de instrução e armazena dados para reescrever a memória principal. (Isso restaura os dados principais destruídos pela leitura.)

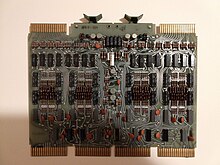

Devido à sua simplicidade, os primeiros modelos PDP-8 eram mais baratos do que a maioria dos outros computadores disponíveis comercialmente. No entanto, eles usaram métodos de produção caros, frequentemente usados para protótipos. Eles usaram milhares de módulos lógicos padronizados muito pequenos, com conectores de ouro, integrados por um backplane caro e complexo com fios enrolados em um grande gabinete.

No modelo 8/S posterior, introduzido em agosto de 1966, duas tensões lógicas diferentes aumentaram o fan-out da lógica diodo-transistor barata. O 8/S também reduziu o número de portas lógicas usando um caminho de dados serial de bit único para fazer aritmética. A CPU do PDP-8/S tem apenas cerca de 519 portas lógicas. Em comparação, pequenos microcontroladores (a partir de 2008) geralmente têm 15.000 ou mais. As reduções na eletrônica permitiram uma caixa muito menor, do tamanho de uma caixa de pão. O 8/S foi projetado por Saul Dinman.

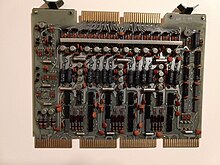

O PDP-8/E, ainda mais recente, é um computador maior e mais capaz, mas reprojetado para melhor valor. Emprega lógica transistor-transistor mais rápida, em circuitos integrados. A memória principal foi redesenhada. Ele permite a expansão com menos gastos porque usa o OMNIBUS no lugar do backplane revestido com fio em modelos anteriores. (Um relato pessoal do desenvolvimento do PDP-8/E pode ser lido no Wiki de História da Engenharia e Tecnologia.)

Versões do PDP-8

O número total de vendas da família PDP-8 foi estimado em mais de 300.000 máquinas. Foram fabricados os seguintes modelos:

| Modelo | Descrição | Ano | Preço | Quantidade produzida | Peso |

|---|---|---|---|---|---|

| PDP-8 | Componentes semi-discretos. Usaram ICs híbridos. DTL. | 1965 | 18 mil dólares. | 1450 | 250 libras (113 kg) |

| LINC-8 | Pode executar o código LINC ou PDP-8 | 1966 | $38,500 | 142 | |

| PDP-8/S | Versão serial de baixo custo do PDP-8 | 1966 | $10.000 | 1024 | 84 libras (38 kg) |

| PDP-8/I | Primeiro PDP-8 feito de TTL padrão ICs | 1968 | $12,800 | 3698 | 250 libras (110 kg) |

| PDP-8/L | Contraparte de baixo custo para o PDP-8/I | 1968 | $8,500 | 3902 | 80 libras (36 kg) |

| PDP-12 | Um PDP-8/I com suporte para instruções LINC (substituído o LINC-8) | 1969 | $27,900 | 755 | |

| PDP-8/E | Menos, placas maiores para melhorar o preço e a eficiência | 1970 | $6,500 | 90 libras (41 kg) (típico) | |

| PDP-8/F | Contraparte de baixo custo para o PDP-8/E | 1972 | 57 libras (26 kg) (típico) | ||

| PDP-8/M | Um PDP-8/F OEM com painel frontal alterado | 1972 | $5.000 | 57 libras (26 kg) (típico) | |

| PDP-8/A | LSI lógica permitiu que a CPU se encaixasse em uma única placa | 1974 | $1,835 | ||

| Intersil 6100 | Microprocessador compatível com PDP-8 (usado no VT78) | 1975 | |||

| Harris 6120 | Microprocessador compatível com PDP-8 (usado nos processadores de texto DECmate) | 1976 |

Implementações modernas

O PDP-8 é facilmente emulado, pois seu conjunto de instruções é muito mais simples do que as arquiteturas modernas. Entusiastas criaram PDP-8s inteiros usando dispositivos FPGA individuais.

Várias simulações de software de um PDP-8 estão disponíveis na Internet, bem como reimplementações de hardware de código aberto. O melhor deles executa corretamente os sistemas operacionais e o software de diagnóstico da DEC. As simulações de software geralmente simulam PDP-8s de modelo recente com todos os periféricos possíveis. Mesmo estes usam apenas uma pequena fração da capacidade de um computador pessoal moderno.

Uma das primeiras versões comerciais de uma máquina virtual PDP-8/S rodava em um Kaypro 386 (um computador baseado em 80386) e era escrita na linguagem de computador C (antes da finalização do padrão ANSI-C) e montador por David Beecher de Denver, Colorado. Substituiu um computador PDP-8/S com defeito que operava a máquina de manuseio de combustível no Reator #85, a Estação de Geração Elétrica movida a Combustível Nuclear de Platteville, Colorado, Ft. St. Vrain. Ele foi revisado pela Rockwell International e funcionou perfeitamente por 2,5 anos durante a operação da Máquina de Manuseio de Combustível enquanto era usado para remover o combustível do núcleo do reator e desativar a usina. Incluía um carregador de fita de papel simulado e um painel frontal.

Entrada/saída

Os sistemas de I/O passaram por grandes mudanças durante a era PDP-8. Os primeiros modelos PDP-8 usam uma interface de painel frontal, um leitor de fita de papel e uma impressora de teletipo com um perfurador de fita de papel opcional. Com o tempo, sistemas de E/S como fita magnética, RS-232 e terminais burros de loop de corrente, leitores de cartões perfurados e discos de cabeçote fixo foram adicionados. No final da era PDP-8, os disquetes e as unidades de disco de cartucho com cabeça móvel eram dispositivos de E/S populares. Entusiastas modernos criaram adaptadores de disco rígido IDE estilo PC padrão para computadores PDP-8 reais e simulados.

Vários tipos de E/S são suportados:

- In-backplane dedicado slots para controladores I/O

- Um ônibus I/O "negativo" (usando sinalização de tensão negativa)

- Um ônibus "Positivo" I/O (a mesma arquitetura usando sinalização TTL)

- O Omnibus (um backplane de slots de ônibus do sistema não dedicado) introduzido no PDP-8/E. (Os detalhes são descritos no artigo IEEE referenciado listado abaixo.)

Uma forma simplificada e barata de DMA chamada "quebra de dados de três ciclos" é suportado; isso requer a assistência do processador. A "quebra de dados" O método move parte da lógica comum necessária para implementar E/S DMA de cada dispositivo de E/S para uma cópia comum da lógica dentro do processador. "Quebra de dados" coloca o processador encarregado de manter o endereço DMA e os registradores de contagem de palavras. Em três ciclos de memória sucessivos, o processador atualiza a contagem de palavras, atualiza o endereço de transferência e armazena ou recupera a palavra de dados de E/S real.

A quebra de dados de um ciclo efetivamente triplica a taxa de transferência DMA porque apenas os dados de destino precisam ser transferidos de e para a memória principal. No entanto, os dispositivos de E/S precisam de mais lógica eletrônica para gerenciar sua própria contagem de palavras e transferir registradores de endereço. Na época em que o PDP-8/E foi introduzido, a lógica eletrônica havia se tornado menos dispendiosa e a "quebra de dados de um ciclo" tornou-se mais popular.

Instalações de programação

Os primeiros sistemas PDP-8 eram enviados sem nenhum software pré-instalado; cada vez que o PDP-8 era ligado, o usuário inseria manualmente as instruções usando um banco de 12 chaves de alternância. Normalmente, essas instruções eram um carregador de inicialização para ler um programa do leitor de fita de papel. O desenvolvimento do programa poderia então prosseguir, usando entrada e saída de fita de papel.

Versões em fita de papel de várias linguagens de programação tornaram-se disponíveis, incluindo o interpretador FOCAL da DEC e um compilador e tempo de execução 4K FORTRAN.

No final da era PDP-8, sistemas operacionais como OS/8 e COS-310 permitiram um editor de modo de linha tradicional e um sistema de desenvolvimento de compilador de linha de comando usando linguagens como linguagem de montagem PAL-III, FORTRAN, BASIC e DIBOL.

Sistemas operacionais em tempo real (RTOS) razoavelmente modernos e avançados e sistemas multiusuário multitarefa preventiva estavam disponíveis: um sistema em tempo real (RTS-8) estava disponível, assim como sistemas comerciais multiusuário (COS-300 e COS-310) e um sistema de processamento de texto de usuário único dedicado (WPS-8).

Também estava disponível um sistema de compartilhamento de tempo, TSS-8. O TSS-8 permite que vários usuários façam login no sistema por meio de terminais de 110 baud e editem, compilem e depurem programas. As linguagens incluem uma versão especial do BASIC, um subconjunto FORTRAN semelhante ao FORTRAN-1 (sem sub-rotinas ou funções escritas pelo usuário), um subconjunto ALGOL, FOCAL e um montador chamado PAL-D.

Uma boa quantidade de software doado por usuários para o PDP-8 estava disponível na DECUS, a Sociedade de Usuários da Digital Equipment Corporation, e muitas vezes vinha com listas e documentação completas de origem.

Conjunto de instruções

Os três bits de ordem superior da palavra de instrução de 12 bits (rotulados como bits de 0 a 2) são o código de operação. Para as seis operações que se referem à memória, os bits 5 a 11 fornecem um endereço de 7 bits. O bit 4, se definido, diz para completar o endereço usando os 5 bits de ordem superior do registrador do contador de programa (PC), o que significa que o local endereçado estava dentro das mesmas 128 palavras da instrução. Se o bit 4 estiver limpo, zeros são usados, então o local endereçado está dentro das primeiras 128 palavras da memória. O bit 3 especifica a indireção; se definido, o endereço obtido conforme descrito até agora aponta para um valor de 12 bits na memória que fornece o endereço efetivo real para a instrução; isso permite que os operandos estejam em qualquer lugar na memória à custa de uma palavra adicional. A instrução JMP não opera em uma palavra de memória, exceto se a indireção for especificada, mas possui os mesmos campos de bit.

| 0 | 2 | 3 | 4 | 5 | 11 | ||||||

| Operação | Eu... | Z. | Desligado | ||||||||

- Páginas de memória

Esse uso da palavra de instrução divide a memória de 4.096 palavras em páginas de 128 palavras; o bit 4 da instrução seleciona a página atual ou a página 0 (endereços 0000–0177 em octal). A memória na página 0 é precária, pois as variáveis colocadas aqui podem ser endereçadas diretamente de qualquer página. (Além disso, o endereço 0000 é onde qualquer rotina de serviço de interrupção deve começar, e os endereços 0010–0017 têm a propriedade especial de auto-incremento precedendo qualquer referência indireta através deles.)

O montador padrão coloca valores constantes para aritmética na página atual. Da mesma forma, saltos entre páginas e chamadas de sub-rotina usam um endereço indireto na página atual.

Era importante escrever rotinas para caber em páginas de 128 palavras ou organizar rotinas para minimizar as transições de página, pois referências e saltos fora da página atual exigem uma palavra extra. Conseqüentemente, muito tempo foi gasto habilmente conservando uma ou várias palavras. Os programadores colocaram o código deliberadamente no final de uma página para obter uma transição livre para a próxima página à medida que o PC foi incrementado.

Instruções básicas

- 000 – E – E a memória operando com AC.

- 001 – TAD – O complemento de dois ADd a memória operando para (A) 12 bits valor assinado (AC) w. carreg em L).

- 010 – ISZ – Incremento do operando de memória e Skip próxima instrução se o resultado for Zero.

- 011 – DCA – Depositar AC na memória operando e Clear AC.

- 100 – JMS – JuMp para Subrotina (retornar endereço de retorno em primeira palavra de subrotina!).

- 101 – JMP – JuMP.

- 110 – IOT – Transferência de Entrada / Saída (veja abaixo).

- 111 – OPR – OPeRations microcodificados (veja abaixo).

Instruções IOT (transferência de entrada-saída)

O processador PDP-8 definiu poucas das instruções IOT, mas simplesmente forneceu uma estrutura. A maioria das instruções IOT foi definida pelos dispositivos de E/S individuais.

| 0 | 2 | 3 | 8 | 9 | 11 | ||||||

| 6 | Dispositivo | Função | |||||||||

- Dispositivo

Os bits 3 a 8 de uma instrução IOT selecionam um dispositivo de E/S. Alguns desses endereços de dispositivos são padronizados por convenção:

- 00 é tratada pelo processador e não enviado para qualquer dispositivo I/O (veja abaixo).

- 01 é geralmente o leitor de fita de papel de alta velocidade.

- 02 é o soco de fita de papel de alta velocidade.

- 03 é o teclado do console (e qualquer leitor de fita de papel de baixa velocidade associado).

- 04 é a impressora de console (e qualquer soco de fita de papel de baixa velocidade associado).

As instruções para o dispositivo 0 afetam o processador como um todo. Por exemplo, ION (6001) ativa o processamento de interrupção e IOFF (6002) o desativa.

- Função

Os bits 9 a 11 de uma instrução IOT selecionam a(s) função(ões) que o dispositivo executa. Dispositivos simples (como o leitor e perfurador de fita de papel e o teclado e a impressora do console) usam os bits de maneiras padrão:

- O Bit 11 faz com que o processador ignore a próxima instrução se o dispositivo I/O estiver pronto.

- Um pouco de 10 limpa AC.

- O Bit 9 move uma palavra entre AC e o dispositivo, inicia outra transferência de E/S e limpa a bandeira "pronta".

Essas operações ocorrem em uma ordem bem definida que fornece resultados úteis se mais de um bit for definido.

Dispositivos mais complicados, como unidades de disco, usam esses 3 bits em modos específicos de dispositivo. Normalmente, um dispositivo decodifica os 3 bits para fornecer 8 códigos de função possíveis.

OPR (OPeRate)

Muitas operações são realizadas usando OPR, incluindo a maioria das condicionais. OPR não endereça um local de memória; a execução condicional é obtida ignorando condicionalmente uma instrução, que normalmente é um JMP.

A instrução OPR foi "microcodificada." Isso não significava o que a palavra significa hoje (que um programa de nível inferior buscava e interpretava a instrução OPR), mas significava que cada bit da palavra de instrução especifica uma determinada ação e o programador poderia realizar várias ações em um único ciclo de instrução. configurando vários bits. Em uso, um programador pode escrever vários mnemônicos de instrução lado a lado, e o montador os combina com OR para criar a palavra de instrução real. Muitos dispositivos de E/S suportam "microcodificados" Instruções IOT.

As ações microcodificadas ocorrem em uma sequência bem definida projetada para maximizar a utilidade de muitas combinações.

As instruções OPR vêm em Grupos. Os bits 3, 8 e 11 identificam o Grupo de uma instrução OPR, portanto é impossível combinar as ações microcodificadas de diferentes grupos.

Grupo 1

00 01 02 03 04 05 07 08 09 10 11 O que se passa? | 1| 1| 1| 0| | | | | | | | | | | | | | | 1| 1| 1| 1| | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | |__|___________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________ |CLA CMA RAR BSW CLL CML RAL IAC Ordem de execução 1 1 2 4 4 4 3

- 7200 – CLA – Acumulador claro

- 7100 – CLL – Limpar o L Bit

- 7040 – CMA – Um acumulador complementar

- 7020 – CML – Complemento L Bit

- 7001 – IAC – Incremento

- 7010 – RAR – Rotate Certo.

- 7004 – RAL – Rotate Esquerda

- 7012 – RTR – Rotate Duas vezes.

- 7006 – RTL – Rotate Duas vezes esquerda

- 7002 – BSW – Byte Swap 6-bit "bytes" (PDP 8/e e acima)

Na maioria dos casos, as operações são sequenciadas para que possam ser combinadas da maneira mais útil. Por exemplo, combinar CLA (CLear Accumulator), CLL (CLear Link) e IAC (Increment ACcumulator) primeiro limpa o AC e o Link, depois incrementa o acumulador, deixando-o definido como 1. Adicionando RAL à mixagem (então CLA CLL IAC RAL) faz com que o acumulador seja limpo, incrementado e depois girado para a esquerda, deixando-o definido como 2. Dessa forma, pequenas constantes inteiras foram colocadas no acumulador com uma única instrução.

A combinação CMA IAC, que o montador permite abreviar como CIA, produz o inverso aritmético de AC: a negação de complemento de dois. Como não há instrução de subtração, apenas a adição de complemento de dois (TAD), calculando a diferença de dois operandos, requer primeiro a negação do subtraendo.

Uma instrução OPR do Grupo 1 que não possui nenhum dos bits microprogramados definidos não executa nenhuma ação. O programador pode escrever NOP (No Operation) para montar tal instrução.

Grupo 2 ou Grupo

00 01 02 03 04 05 07 08 09 10 11 O que se passa? | 1| 1| 1| 1| | | | | | | | | | | 1| 1| 1| 1| 1| | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | 1| 1| | 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| |__|___________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________ |CLA SZA OSR SMA SNL HLT 2 1 1 1 3 3 3 2 1 1 1 1 1 3 3 3 2 2 1 1 1 1 1 1 1 3 3 3 3 3 2 2 1 1 1 1 1 3 3 3 3 2 2 2 1 1 1 1 1 1 3 3 3 3 3 3 2 3 2 2 1 1 1 1 1 1 3 3 3 3 3 3 3 2 2 1 1 1 1 1 1 3 3 3 3 3 2 3 2 3 2 3 2 3 2 1 1 1 1 1 1 1 1 1 1 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 2 3 2 3 3 3 2 3 2 3 2 3 2 3 2 3 2 3 2 3 2 3 2 3 3 2 3 3 2 3 2 3 2 3 2 3 2 3 2 3 2 3 2 3 2 3 2 3 2 3 2 3 2 3 3 3 2 3 3 3 3 3 3 2 3 2 3 2 3 2 3 3 3 3 3 2 3 2 3 2 3 2 3 3 2 3 3 3 3 3 3 3 2 3 2 3 2 3 2 3 2 3 2 3 2 3 3 2 3 3 3 3 2 3 2 3 2 3 2 3 2 3 2 3 2 3 2 3 3 3 2

- 7600 – CLA – Clear AC

- 7500 – SMA – Pular em AC < 0 (ou grupo)

- 7440 – SZA – Pular em AC = 0 (ou grupo)

- 7420 – SNL – Pular em L ≠ 0 (ou grupo)

- 7404 - OSR - logicamente 'ou' front-panel switches com AC

- 7402 – HLT – Halt

Quando o bit 8 estiver limpo, um salto será executado se qualquer uma das condições especificadas for verdadeira. Por exemplo, "SMA SZA", opcode 7540, pula se AC ≤ 0.

Uma instrução OPR do Grupo 2 que não possui nenhum dos bits microprogramados definidos é outra instrução No-Op.

Grupo 2 e Grupo

00 01 02 03 04 05 07 08 09 10 11 O que se passa? | 1| 1| 1| 1| | | | | | | | | 1| 1| 1| 1| 1| | | | | | | | | | | | | | | | | | | | | | | 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | |__|___________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________ |CLA SNA OSR SPA SZL HLT 2 1 1 1 1 3 2 2 2 2 1 1 1 1 1 1 3 2 2 2 2 2 2 2 1 1 1 1 1 1 3 2 2 2 2 2 2 2 2 1 1 1 1 1 3 2 2 2 2 2 2 2 2 2 1 1 1 1 3 2 2 2 2 2 2 2 2 2 2 1 1 1 1 3 2 2 2 2 2 2 2 2 2 1 1 1 1 1 3 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 1 1 1 1 1 2 2 2 2 2 2 2 2 2 1 1 1 1 1 1 1 1 1 1 1 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 1 1 1 1 1 1 1 1 1 1 1 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 1 1 1 1 1 1 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2

- 7410 – SKP – Pular incondicionalmente

- 7610 – CLA – Clear AC

- 7510 – SPA – Pular em AC ≥ 0 (e grupo)

- 7450 – SNA – Pular em AC ≠ 0 (e grupo)

- 7430 – SZL – Pular em L = 0 (e grupo)

Quando o bit 8 é definido, o grupo 2, ou condição de salto é invertido, através das leis de De Morgan: o salto não é executado se qualquer condição do grupo 2, ou for verdadeiro, significando que todas as condições de ignorar especificadas devem ser verdadeiras. Por exemplo, "SPA SNA", opcode 7550, pula se AC > 0. Se nenhum dos bits 5–7 estiver definido, o salto é incondicional.

Grupo 3

As combinações de bits não utilizados de OPR são definidas como um terceiro grupo de ações microprogramadas que afetam principalmente o registro MQ (Multiplicador/Quociente). As instruções do registro MQ e do elemento aritmético estendido (EAE) são opcionais e só existem quando a opção EAE foi adquirida.

00 01 02 03 04 05 07 08 09 10 11 O que se passa? | 1| 1| 1| 1| 1| | | | | | | 1| 1| 1| 1| 1| 1| 1| 1| 1| | | | | | | | | | | | | | | | | | | | | | | | | 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| 1| |__|___________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________ |CLA SCA _ _/ | MQA MQL CODE 1* 2 2 2 3

- 7601 – CLA – Clear AC

- 7501 – MQA – Quociente Multiplicador com AC (lógica ou MQ em AC)

- 7441 – SCA – Carga do contador passo em AC

- 7421 – MQL – Carga Quociente Multiplier (Transferir AC para MQ, AC claro)

- 7621 – CAM – CLA + MQL limpa tanto AC quanto MQ.

Normalmente, CLA e MQA foram combinados para transferir MQ para AC. Outra combinação útil é MQA e MQL, para trocar os dois registradores.

Três bits especificaram uma instrução de multiplicação/divisão a ser executada:

- 7401 – Nenhuma operação

- 7403 – SCL – Carga de Contador de Passo (a palavra imediata segue, PDP-8/I e para cima)

- 7405 – MUITO – Multiplicar

- 7407 – DVI – Divide

- 7411 – NMI – Normalize

- 7413 – SHL – Shift esquerda (palavra imediata segue)

- 7415 – ASR – Mudança aritmética direita

- 7417 – LSR – Mudança lógica direita

Controle de memória

Uma palavra de 12 bits pode ter 4.096 valores diferentes, e esse é o número máximo de palavras que o PDP-8 original pode endereçar indiretamente por meio de um ponteiro de palavra. 4.096 palavras de 12 bits representam 6.144 bytes na terminologia moderna, ou 6 kB. À medida que os programas se tornaram mais complexos e o preço da memória caiu, tornou-se desejável expandir esse limite.

Para manter a compatibilidade com programas pré-existentes, um novo hardware fora do projeto original adicionou bits de alta ordem aos endereços efetivos gerados pelo programa. O Memory Extension Controller expande a memória endereçável por um fator de 8, para um total de 32.768 palavras. Essa expansão foi considerada suficiente porque, com a memória central custando cerca de 50 centavos por palavra, 32K de memória total seria igual ao custo da CPU.

Cada 4K de memória é chamado de campo. O controlador de extensão de memória contém dois registradores de três bits: o DF (campo de dados) e o IF (campo de instrução). Esses registradores especificam um campo para cada referência de memória da UCP, permitindo um total de 15 bits de endereço. O registrador IF especifica o campo para buscas de instruções e referências diretas à memória; o registrador DF especifica o campo para acesso indireto aos dados. Um programa em execução em um campo pode referenciar dados no mesmo campo por endereçamento direto e referenciar dados em outro campo por endereçamento indireto.

Um conjunto de instruções de E/S na faixa de 6200 a 6277 é manipulado pelo controlador de extensão de memória e dá acesso aos registradores DF e IF. A instrução 62X1 (CDF, Alterar campo de dados) define o campo de dados como X. Da mesma forma, 62X2 (CIF) define o campo de instrução e 62X3 define ambos. Programas pré-existentes nunca executariam CIF ou CDF; os registradores DF e IF apontariam para o mesmo campo, um único campo ao qual esses programas estavam limitados. O efeito da instrução CIF foi adiado para coincidir com a próxima instrução JMP ou JMS, para que a execução do CIF não causasse um salto.

Era mais complicado para programas de campos múltiplos lidar com os limites de campo e os registradores DF e IF do que seria se eles pudessem simplesmente gerar endereços de 15 bits, mas o design forneceu compatibilidade com versões anteriores e é consistente com os 12 arquitetura de bits usada em todo o PDP-8. Compare o Intel 8086 posterior, cujos endereços de memória de 16 bits são expandidos para 20 bits combinando-os com o conteúdo de um registrador de segmento especificado ou implícito.

O esquema de memória estendida permite que os programas existentes manipulem memória aumentada com alterações mínimas. Por exemplo, 4K FOCAL normalmente tinha cerca de 3K de código com apenas 1K sobrando para o programa e dados do usuário. Com alguns patches, o FOCAL poderia usar um segundo campo 4K para programa e dados do usuário. Além disso, campos 4K adicionais podem ser alocados para usuários separados, transformando o 4K FOCAL em um sistema de compartilhamento de tempo multiusuário.

- Virtualização

No PDP-8/E e modelos posteriores, o Memory Extension Controller foi aprimorado para permitir a virtualização da máquina. Um programa escrito para usar todos os recursos de um PDP-8 pode coexistir com outros programas desse tipo no mesmo PDP-8 sob o controle de um gerenciador de máquina virtual. O gerente pode fazer com que todas as instruções de E/S (incluindo aquelas que operam no controlador de extensão de memória) causem uma interrupção (uma interrupção tratada pelo gerente). Dessa forma, o gerenciador pode mapear referências de memória, mapear dados ou campos de instrução e redirecionar E/S para diferentes dispositivos. Cada programa original tem acesso completo a uma "máquina virtual" fornecido pelo gerente.

Novas instruções de E/S para o controlador de extensão de memória recuperam o valor atual dos campos de dados e instruções, permitindo que o software salve e restaure a maior parte do estado da máquina através de uma armadilha. No entanto, um programa não pode detectar se a CPU está no processo de adiar o efeito de uma instrução CIF (se executou uma CIF e ainda não executou a instrução de salto correspondente). O gerente deve incluir um emulador PDP-8 completo (não é difícil para uma máquina de 8 instruções). Sempre que uma instrução CIF intercepta o gerente, ela deve emular as instruções até o próximo salto. Felizmente, como um salto geralmente é a próxima instrução após o CIF, essa emulação não torna os programas muito lentos, mas é uma grande solução alternativa para uma deficiência de design aparentemente pequena.

Na época do PDP-8/A, os preços da memória haviam caído o suficiente para que uma memória superior a 32K fosse desejável. O 8/A adicionou um novo conjunto de instruções para lidar com mais de oito campos de memória. O número do campo agora pode ser colocado no AC, em vez de codificado na instrução. No entanto, nessa época, o PDP-8 estava em declínio, então muito pouco software padrão foi modificado para usar esses novos recursos.

Exemplos

Os exemplos a seguir mostram o código em linguagem de montagem PDP-8 como se poderia escrever para o montador PAL-III.

Comparando dois números

O trecho de código a seguir mostra o que é necessário apenas para comparar dois números:

/Compare números em memória no OPD1 e OPD2 CLA CLL /Must começar com 0 em AC e link TAD OPD1 /Load primeiro operando em AC (adicionando-o a 0); link ainda é claro CIA /Complement, então incremento AC, negando-o TAD OPD2 /AC agora tem OPD2-OPD1; se OPD2≥OPD1, soma transborda e link é definido SZL /Skip se o link é claro JMP OP2GT /Jump em algum lugar no caso de OPD2≥OPD1; /Outra maneira, cair para o código abaixo.

Como mostrado, grande parte do texto de um programa PDP-8 típico não se concentra no algoritmo pretendido pelo autor, mas na mecânica de baixo nível. Um problema adicional de legibilidade é que em saltos condicionais como o mostrado acima, a instrução condicional (que pula o JMP) destaca o oposto da condição de interesse.

Saída de string

Este programa completo em linguagem assembly PDP-8 gera "Hello, world!" para o teleimpressor.

*10 / Definir origem de montagem atual para endereço 10, STPTR, STRNG-1 / Um registro de auto-increment (um de oito em 10-17) * 200 / Definir origem de montagem atual para área de texto do programa HELLO, CLA CLL / Clear AC e Link novamente (necessário quando voltamos de tls) TAD I Z STPTR / Obter o próximo personagem, indireto através do endereço PRE-auto-increment da página zero SNA / Skip if non-zero (not end of string) HLT / Else parar em zero (fim de cadeia) TLS / Saída do personagem na AC para o teleprinter TSF / Pular se teleprinter pronto para o personagem JMP.-1 / Else saltar para trás e tentar novamente JMP HELLO / Voltar para o próximo personagem STRNG, 310 / H 345 / e 354 / l 354 / l 357 / o 254 /, 240 / (espaço) 367 / w 357 / o 362 / r 354 / l 344 / d 241 / ! 0 / Fim da string $HELLO / TERMINATOR DE DEFAULT

Sub-rotinas

O processador PDP-8 não implementa uma pilha na qual armazenar registradores ou outro contexto quando uma sub-rotina é chamada ou ocorre uma interrupção. (Uma pilha pode ser implementada em software, conforme demonstrado na próxima seção.) Em vez disso, a instrução JMS simplesmente armazena o PC atualizado (apontando além do JMS, para o endereço de retorno) no endereço efetivo e pula para o endereço efetivo mais um. A sub-rotina retornou ao chamador usando uma instrução JMP indireta que endereça a primeira palavra da sub-rotina.

Por exemplo, aqui está "Hello, World!" reescrito para usar uma sub-rotina. Quando a instrução JMS salta para a sub-rotina, ela modifica o 0 codificado na localização OUT1:

*10 / Definir origem de montagem atual para endereço 10, STPTR, STRNG-1 / Um registro de auto-increment (um de oito em 10-17) * 200 / Definir origem de montagem (endereço de carga) LOOP, TAD I STPTR / Pre-increment mem localização 10, buscar indireta para obter o próximo personagem da nossa mensagem SNA / Skip on non-zero AC HLT / Else parar no final da mensagem JMS OUT1 / Escreva um personagem JMP LOOP / E loop de volta para mais OUT1, 0 / Será substituído pelo PC atualizado do chamador TSF / Pular se a impressora estiver pronta JMP.-1 / Aguarde a bandeira TLS / Enviar o personagem no AC CLA CLL / Clear AC e Link para o próximo passe JMP I OUT1 / Voltar ao chamador STRNG, "H / Uma mensagem bem conhecida "E" "I / NOTA: "I / "o / Strings in PAL-8 e PAL-III foram "sixbit" ", / Para usar ASCII, nós soletrá-lo, personagem por personagem " "w / "O quê?" "r / "I / "D / "! 015 / 012 / 0 / Marque o fim da nossa cadeia de caracteres nulos (.ASCIZ ainda não tinha sido inventado!)

O fato de a instrução JMS usar a palavra logo antes do código da sub-rotina para depositar o endereço de retorno evita a reentrada e a recursão sem trabalho adicional por parte do programador. Também torna difícil usar ROM com o PDP-8 porque o armazenamento de endereço de retorno de leitura/gravação é misturado com armazenamento de código somente leitura no espaço de endereço. Os programas destinados a serem colocados em ROMs abordam esse problema de várias maneiras:

- Eles se copiam para ler a memória antes da execução, ou

- Eles são colocados em cartões ROM especiais que fornecem algumas palavras de leitura / gravação de memória, acessado indiretamente através do uso de um décimo terceiro sinal em cada palavra ROM.

- Eles evitam o uso de subrotinas; ou usam código como o seguinte, em vez da instrução JMS, para colocar o endereço de retorno na memória de leitura-escrita:

JUMPL, DCA TEMP / Depositar o acumulador em algum local temporário TAD JUMPL+3 / Carregar o endereço de retorno para o acumulador: codificado rígido JMP SUBRO / Ir para a subrotina, e tê-lo alça pulando de volta (para JUMPL+3)

O uso da instrução JMS dificulta a depuração. Se um programador comete o erro de chamar uma sub-rotina, diretamente ou por uma sub-rotina intermediária, então o endereço de retorno da chamada externa é destruído pelo endereço de retorno da chamada subseqüente, levando a um loop infinito. Se um módulo for codificado com um endereço incorreto ou obsoleto para uma sub-rotina, ele não apenas deixará de executar toda a sequência do código da sub-rotina, como poderá modificar uma palavra do código da sub-rotina, depositando um endereço de retorno que o processador pode interpretar como uma instrução durante uma chamada correta subseqüente para a sub-rotina. Ambos os tipos de erro podem se tornar evidentes durante a execução do código que foi escrito corretamente.

Pilha de software

Embora o PDP-8 não tenha uma pilha de hardware, as pilhas podem ser implementadas em software. Aqui estão exemplos de sub-rotinas PUSH e POP, simplificadas para omitir problemas como teste de estouro e estouro de pilha:

*100 /fazer rotinas acessíveis para o próximo exemplo PuSH, 0 DCA DATA CLA CMA / -1 TAD SP DCA SP DADOS TAD DCA I SP JMP I PUSH / Retorno POP, 0 CLARO TAD I SP ISZ SP JMP POP DATA, 0 SP, 0

E aqui está "Hello World" com esta "pilha" implementado, e "OUT" sub-rotina:

200 MAIN, CLA CLL /Defina o ponteiro da mensagem TAD (MESSG /Ao início da mensagem (literal) DCA SP LOOP, JMS POP SNA /Pare a execução se zero HLT JMS OUT /Outro modo, saída de um personagem JMP LOOP MESSG, "H " "I" "I" " " " " " " "I" " "! 015 012 0 OUT, 0 / Será substituído pelo PC atualizado do chamador TSF / Pular se a impressora estiver pronta JMP.-1 / Aguarde a bandeira TLS / Enviar o personagem no AC CLA CLL / Clear AC e Link para o próximo passe JMP I OUT / Voltar ao chamador

Lista encadeada

Outra sub-rotina possível para o PDP-8 é uma lista encadeada.

GETN, 0 / Obtém o número apontado e move o ponteiro CLA CLL / acumulador de Clear TAD I PTR / Obtém o número apontado DCA TEMP /Salvar o valor atual ISZ PTR / ponteiro de incrustação TAD I PTR / Obter o próximo endereço DCA PTR /Put no ponteiro JMP I GETN /retorno PTR, 0 TEMP, 0

Interrupções

Existe uma única linha de interrupção no barramento de E/S do PDP-8. O processador lida com qualquer interrupção desativando outras interrupções e executando um JMS para a localização 0000. Como é difícil escrever sub-rotinas reentrantes, é difícil aninhar interrupções e isso geralmente não é feito; cada interrupção é executada até a conclusão e reativa as interrupções antes de executar a instrução JMP I 0 que retorna da interrupção.

Como há apenas uma única linha de interrupção no barramento de E/S, a ocorrência de uma interrupção não informa ao processador a origem da interrupção. Em vez disso, a rotina do serviço de interrupção precisa pesquisar cada dispositivo de E/S ativo em série para ver se ele é a origem. O código que faz isso é chamado de cadeia de saltos porque consiste em uma série de comandos PDP-8 "testar e pular se sinalizador definido" instruções de E/S. (Não era incomum que uma cadeia de salto chegasse ao seu fim sem encontrar qualquer dispositivo que precisasse de serviço.) A prioridade de interrupção relativa dos dispositivos de E/S é determinada por sua posição no salto cadeia: Se vários dispositivos interromperem, o dispositivo testado anteriormente na cadeia de salto será atendido primeiro.

Livros

Um livro de engenharia popular na década de 1980, The Art of Digital Design de David Winkel e Franklin Prosser, contém um exemplo de problema abrangendo vários capítulos nos quais os autores demonstram o processo de projetar um computador que é compatível com o PDP-8/I. A função de cada componente é explicada. Embora não seja um projeto de produção, pois usa componentes SSI e MSI mais modernos e estado sólido em vez de memória principal, o exercício fornece uma descrição detalhada da operação do computador.

Clones não licenciados

A URSS produziu os minicomputadores Saratov-1 e Saratov-2, que clonaram o PDP-8 e o PDP-8/E, respectivamente.

Contenido relacionado

Karl Dönitz

Códice

Bretwalda