Matriz de portas programável em campo

Uma matriz de portas programável em campo (FPGA) é um circuito integrado projetado para ser configurado por um cliente ou designer após a fabricação - daí o termo campo -programável. A configuração do FPGA geralmente é especificada usando uma linguagem de descrição de hardware (HDL), semelhante à usada para um circuito integrado específico de aplicativo (ASIC). Diagramas de circuitos eram usados anteriormente para especificar a configuração, mas isso é cada vez mais raro devido ao advento de ferramentas de automação de projeto eletrônico.

Os FPGAs contêm uma matriz de blocos lógicos programáveis e uma hierarquia de interconexões reconfiguráveis, permitindo que os blocos sejam conectados. Os blocos lógicos podem ser configurados para executar funções combinacionais complexas ou atuar como portas lógicas simples, como AND e XOR. Na maioria dos FPGAs, os blocos lógicos também incluem elementos de memória, que podem ser flip-flops simples ou blocos de memória mais completos. Muitos FPGAs podem ser reprogramados para implementar diferentes funções lógicas, permitindo uma computação reconfigurável flexível como realizada em software de computador.

Os FPGAs têm um papel notável no desenvolvimento de sistemas embarcados devido à sua capacidade de iniciar o desenvolvimento do software do sistema simultaneamente com o hardware, permitir simulações de desempenho do sistema em uma fase muito inicial do desenvolvimento e permitir vários testes de sistema e iterações de projeto antes de finalizar o sistema arquitetura.

História

A indústria de FPGA surgiu da memória programável somente leitura (PROM) e dos dispositivos lógicos programáveis (PLDs). PROMs e PLDs tinham a opção de serem programados em lotes em uma fábrica ou no campo (programável em campo).

A Altera foi fundada em 1983 e entregou o primeiro dispositivo lógico reprogramável da indústria em 1984 - o EP300 - que apresentava uma janela de quartzo na embalagem que permitia aos usuários acender uma lâmpada ultravioleta na matriz para apagar o Células EPROM que continham a configuração do dispositivo.

A Xilinx produziu o primeiro array de portas programáveis em campo comercialmente viável em 1985 - o XC2064. O XC2064 tinha portas programáveis e interconexões programáveis entre portas, o início de uma nova tecnologia e mercado. O XC2064 tinha 64 blocos lógicos configuráveis (CLBs), com duas tabelas de pesquisa de três entradas (LUTs).

Em 1987, o Naval Surface Warfare Center financiou um experimento proposto por Steve Casselman para desenvolver um computador que implementaria 600.000 portões reprogramáveis. Casselman foi bem-sucedido e uma patente relacionada ao sistema foi emitida em 1992.

A Altera e a Xilinx continuaram incontestadas e cresceram rapidamente de 1985 até meados da década de 1990, quando os concorrentes surgiram, corroendo uma parcela significativa de sua participação no mercado. Em 1993, a Actel (agora Microsemi) atendia cerca de 18% do mercado.

A década de 1990 foi um período de rápido crescimento para FPGAs, tanto na sofisticação do circuito quanto no volume de produção. No início dos anos 90, os FPGAs eram usados principalmente em telecomunicações e redes. No final da década, os FPGAs encontraram seu caminho para aplicações de consumo, automotivas e industriais.

Em 2013, Altera (31 por cento), Actel (10 por cento) e Xilinx (36 por cento) juntas representavam aproximadamente 77 por cento do mercado de FPGA.

Empresas como a Microsoft começaram a usar FPGAs para acelerar sistemas computacionalmente intensivos de alto desempenho (como os data centers que operam seu mecanismo de pesquisa Bing), devido à vantagem de desempenho por watt que os FPGAs oferecem. A Microsoft começou a usar FPGAs para acelerar o Bing em 2014 e, em 2018, começou a implantar FPGAs em outras cargas de trabalho de data center para sua plataforma de computação em nuvem Azure.

Crescimento

Os cronogramas a seguir indicam o progresso em diferentes aspectos do projeto de FPGA.

Portões

- 1987: 9.000 portões, Xilinx

- 1992: 600.000, Departamento de Guerra de Superfície Naval

- Início dos anos 2000: milhões

- 2013: 50 milhões, Xilinx

Tamanho do mercado

- 1985: Primeira FPGA comercial: Xilinx XC2064

- 1987: $14 milhões

- C.1993385 milhões de dólares

- 2005: $1.9 bilhões

- 2010 estima: $2.75 bilhões

- 2013: $5.4 bilhões

- Estimativa de 2020: 9,8 bilhões de dólares

O design começa

Um design start é um novo design personalizado para implementação em um FPGA.

- 2005: 80.000

- 2008: 90.000

Design

Os FPGAs contemporâneos possuem amplas portas lógicas e blocos de RAM para implementar computações digitais complexas. Os FPGAs podem ser usados para implementar qualquer função lógica que um ASIC possa executar. A capacidade de atualizar a funcionalidade após o envio, a reconfiguração parcial de uma parte do projeto e os baixos custos de engenharia não recorrentes relativos a um projeto ASIC (apesar do custo unitário geralmente mais alto) oferecem vantagens para muitas aplicações.

Como os projetos de FPGA empregam taxas de E/S muito rápidas e barramentos de dados bidirecionais, torna-se um desafio verificar o tempo correto de dados válidos dentro do tempo de configuração e tempo de espera. O planejamento de chão ajuda a alocação de recursos dentro dos FPGAs para atender a essas restrições de tempo.

Alguns FPGAs possuem recursos analógicos além das funções digitais. O recurso analógico mais comum é uma taxa de variação programável em cada pino de saída, permitindo que o engenheiro defina taxas baixas em pinos levemente carregados que, de outra forma, tocariam ou se acoplariam inaceitavelmente, e definir taxas mais altas em canais de alta velocidade altamente carregados que, de outra forma, funcionariam muito lentamente. Também são comuns os circuitos do driver do oscilador de cristal de quartzo, os osciladores de resistência-capacitância no chip e loops de travamento de fase com osciladores controlados por tensão incorporados usados para geração e gerenciamento de relógio, bem como para relógios de transmissão de serializador-desserializador de alta velocidade (SERDES). e recuperação do relógio do receptor. Bastante comuns são comparadores diferenciais em pinos de entrada projetados para serem conectados a canais de sinalização diferencial. Alguns FPGAs de sinal misto possuem conversores periféricos analógico-digital (ADCs) e conversores digital-analógico (DACs) integrados com blocos de condicionamento de sinal analógico, permitindo que eles operem como um sistema em um chip (SoC). Esses dispositivos obscurecem a linha entre um FPGA, que transporta uns e zeros digitais em sua estrutura de interconexão programável interna, e um array analógico programável em campo (FPAA), que transporta valores analógicos em sua estrutura de interconexão programável interna.

Blocos lógicos

A arquitetura FPGA mais comum consiste em uma matriz de blocos lógicos chamados de blocos lógicos configuráveis (CLBs) ou blocos lógicos de matrizes (LABs), dependendo do fornecedor, blocos de E/S e canais de roteamento. Geralmente, todos os canais de roteamento têm a mesma largura (número de sinais). Múltiplos pads de E/S podem caber na altura de uma linha ou na largura de uma coluna na matriz.

"Um circuito de aplicação deve ser mapeado em um FPGA com recursos adequados. Embora o número de blocos lógicos e E/S necessários seja facilmente determinado a partir do projeto, o número de canais de roteamento necessários pode variar consideravelmente mesmo entre projetos com a mesma quantidade de lógica. Por exemplo, um comutador crossbar requer muito mais roteamento do que um array sistólico com a mesma contagem de portas. Como os canais de roteamento não utilizados aumentam o custo (e diminuem o desempenho) do FPGA sem oferecer nenhum benefício, os fabricantes de FPGA tentam fornecer apenas canais suficientes para que a maioria dos projetos que se encaixam em termos de tabelas de pesquisa (LUTs) e E/S possam ser roteado. Isso é determinado por estimativas como as derivadas da regra de Rent ou por experimentos com designs existentes."

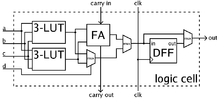

Em geral, um bloco lógico consiste em algumas células lógicas (chamadas ALM, LE, fatia etc.). Uma célula típica consiste em uma LUT de 4 entradas, um somador completo (FA) e um flip-flop tipo D. Eles podem ser divididos em duas LUTs de 3 entradas. No modo normal, eles são combinados em uma LUT de 4 entradas por meio do primeiro multiplexador (mux). No modo aritmético, suas saídas são enviadas para o somador. A seleção do modo é programada no segundo mux. A saída pode ser síncrona ou assíncrona, dependendo da programação do terceiro mux. Na prática, todo ou partes do somador são armazenados como funções nas LUTs para economizar espaço.

Blocos rígidos

As famílias FPGA modernas expandem os recursos acima para incluir funcionalidade de nível superior fixada em silício. Ter essas funções comuns embutidas no circuito reduz a área necessária e dá a essas funções maior velocidade em comparação com construí-las a partir de primitivas lógicas. Exemplos disso incluem multiplicadores, blocos DSP genéricos, processadores embutidos, lógica de E/S de alta velocidade e memórias embutidas.

Os FPGAs de ponta podem conter transceptores multigigabit de alta velocidade e núcleos IP rígidos, como núcleos de processador, unidades de controle de acesso ao meio Ethernet, controladores PCI/PCI Express e controladores de memória externos. Esses núcleos existem ao lado da malha programável, mas são construídos com transistores em vez de LUTs para que tenham desempenho de nível ASIC e consumo de energia sem consumir uma quantidade significativa de recursos de malha, deixando mais malha livre para a lógica específica do aplicativo. Os transceptores multigigabit também contêm circuitos analógicos de entrada e saída de alto desempenho, juntamente com serializadores e desserializadores de alta velocidade, componentes que não podem ser construídos a partir de LUTs. A funcionalidade da camada física de nível superior (PHY), como a codificação de linha, pode ou não ser implementada juntamente com os serializadores e desserializadores na lógica rígida, dependendo do FPGA.

Núcleo flexível

Uma abordagem alternativa para usar processadores hard-macro é fazer uso de núcleos IP de processador soft que são implementados dentro da lógica FPGA. Nios II, MicroBlaze e Mico32 são exemplos de processadores softcore populares. Muitos FPGAs modernos são programados em "tempo de execução", o que levou à ideia de computação reconfigurável ou sistemas reconfiguráveis - CPUs que se reconfiguram para se adequar à tarefa em questão. Além disso, novas arquiteturas não FPGA estão começando a surgir. Os microprocessadores configuráveis por software, como o Stretch S5000, adotam uma abordagem híbrida, fornecendo uma variedade de núcleos de processador e núcleos programáveis semelhantes a FPGA no mesmo chip.

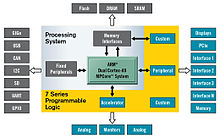

Integração

Em 2012, a abordagem arquitetônica de granulação grossa deu um passo adiante ao combinar os blocos lógicos e interconexões de FPGAs tradicionais com microprocessadores embutidos e periféricos relacionados para formar um "sistema em um chip programável" completo. Este trabalho espelha a arquitetura criada por Ron Perloff e Hanan Potash do Burroughs Advanced Systems Group em 1982, que combinou uma arquitetura de CPU reconfigurável em um único chip chamado SB24. Exemplos de tais tecnologias híbridas podem ser encontrados no Xilinx Zynq-7000 totalmente SoC programável, que inclui um processador ARM Cortex-A9 MPCore dual-core de 1,0 GHz incorporado na malha lógica do FPGA ou no Altera Arria V FPGA, que inclui um ARM Cortex-A9 MPCore dual-core de 800 MHz. O Atmel FPSLIC é outro desses dispositivos, que usa um processador AVR em combinação com a arquitetura de lógica programável da Atmel. Os dispositivos Microsemi SmartFusion incorporam um núcleo de processador ARM Cortex-M3 rígido (com até 512 kB de flash e 64 kB de RAM) e periféricos analógicos, como conversores analógico-digital multicanal e conversores digital-analógico para sua estrutura FPGA baseada em memória flash.

Regulação

A maioria dos circuitos construídos dentro de um FPGA são circuitos síncronos que requerem um sinal de clock. Os FPGAs contêm redes de roteamento globais e regionais dedicadas para clock e redefinição, normalmente como uma encarnação de uma árvore H, para que possam ser entregues com inclinação mínima. Além disso, os FPGAs geralmente contêm componentes analógicos de loop travado por fase e/ou loop travado por atraso para sintetizar novas frequências de clock, bem como atenuar o jitter. Projetos complexos podem usar vários relógios com diferentes relações de frequência e fase, cada um formando domínios de relógio separados. Esses sinais de clock podem ser gerados localmente por um oscilador ou podem ser recuperados de um fluxo de dados seriais de alta velocidade. Deve-se ter cuidado ao construir circuitos de cruzamento de domínio de relógio para evitar metaestabilidade. Os FPGAs geralmente contêm blocos de RAMs que são capazes de funcionar como RAMs de porta dupla com diferentes clocks, auxiliando na construção de FIFOs de construção e buffers de porta dupla que conectam diferentes domínios de clock.

Arquiteturas 3D

Para reduzir o tamanho e o consumo de energia dos FPGAs, fornecedores como Tabula e Xilinx introduziram arquiteturas 3D ou empilhadas. Após a introdução de seus FPGAs da série 7 de 28 nm, a Xilinx disse que várias das peças de maior densidade nessas linhas de produtos FPGA serão construídas usando várias matrizes em um pacote, empregando tecnologia desenvolvida para construção 3D e montagens empilhadas.

A abordagem da Xilinx empilha várias (três ou quatro) matrizes FPGA ativas lado a lado em um interpositor de silício - uma única peça de silício que transporta interconexão passiva. A construção multi-die também permite que diferentes partes do FPGA sejam criadas com diferentes tecnologias de processo, pois os requisitos do processo são diferentes entre a própria estrutura do FPGA e os transceptores seriais de 28 Gbit/s de altíssima velocidade. Um FPGA construído dessa maneira é chamado de FPGA heterogêneo.

A abordagem heterogênea da Altera envolve o uso de um único molde monolítico de FPGA e a conexão de outros moldes/tecnologias ao FPGA usando a tecnologia EMIB (multi_die interconnect bridge) integrada da Intel.

Programação

Para definir o comportamento do FPGA, o usuário fornece um projeto em uma linguagem de descrição de hardware (HDL) ou como um projeto esquemático. A forma HDL é mais adequada para trabalhar com grandes estruturas porque é possível especificar o comportamento funcional de alto nível em vez de desenhar cada peça à mão. No entanto, a entrada esquemática pode permitir uma visualização mais fácil de um projeto e seus módulos componentes.

Usando uma ferramenta de automação de design eletrônico, uma netlist mapeada por tecnologia é gerada. A netlist pode então ser ajustada à arquitetura real do FPGA usando um processo chamado place-and-route, geralmente executado pelo software place-and-route proprietário da empresa FPGA. O usuário validará os resultados do mapa, local e rota por meio de análise de tempo, simulação e outras metodologias de verificação e validação. Uma vez concluído o processo de design e validação, o arquivo binário gerado, geralmente usando o software proprietário do fornecedor do FPGA, é usado para (re)configurar o FPGA. Este arquivo é transferido para o FPGA/CPLD através de uma interface serial (JTAG) ou para um dispositivo de memória externo como uma EEPROM.

Os HDLs mais comuns são VHDL e Verilog, bem como extensões como SystemVerilog. No entanto, na tentativa de reduzir a complexidade do design em HDLs, que foram comparadas ao equivalente a linguagens assembly, há movimentos para aumentar o nível de abstração por meio da introdução de linguagens alternativas. Instrumentos Nacionais' A linguagem de programação gráfica LabVIEW (às vezes chamada de "G") possui um módulo adicional FPGA disponível para direcionar e programar o hardware FPGA. A Verilog foi criada para simplificar o processo tornando o HDL mais robusto e flexível. Verilog é atualmente o mais popular. Verilog cria um nível de abstração para ocultar os detalhes de sua implementação. O Verilog tem uma sintaxe semelhante à do C, ao contrário do VHDL.

Para simplificar o projeto de sistemas complexos em FPGAs, existem bibliotecas de funções e circuitos complexos predefinidos que foram testados e otimizados para acelerar o processo de projeto. Esses circuitos predefinidos são comumente chamados de núcleos de propriedade intelectual (IP) e estão disponíveis em fornecedores de FPGA e fornecedores de IP terceirizados. Eles raramente são gratuitos e normalmente lançados sob licenças proprietárias. Outros circuitos predefinidos estão disponíveis em comunidades de desenvolvedores, como OpenCores (normalmente lançados sob licenças gratuitas e de código aberto, como GPL, BSD ou licença semelhante) e outras fontes. Tais projetos são conhecidos como "hardware de código aberto."

Em um fluxo de design típico, um desenvolvedor de aplicativo FPGA simulará o design em vários estágios ao longo do processo de design. Inicialmente a descrição RTL em VHDL ou Verilog é simulada criando bancadas de teste para simular o sistema e observar os resultados. Então, após o mecanismo de síntese ter mapeado o design para uma netlist, a netlist é traduzida para uma descrição de nível de porta onde a simulação é repetida para confirmar que a síntese ocorreu sem erros. Finalmente, o projeto é apresentado no FPGA no qual os atrasos de propagação de ponto podem ser adicionados e a simulação é executada novamente com esses valores anotados novamente na netlist.

Mais recentemente, OpenCL (Open Computing Language) está sendo usado por programadores para aproveitar o desempenho e as eficiências de energia que os FPGAs fornecem. O OpenCL permite que os programadores desenvolvam código na linguagem de programação C e direcionem funções FPGA como kernels OpenCL usando construções OpenCL. Para mais informações, consulte síntese de alto nível e C para HDL.

A maioria dos FPGAs dependem de uma abordagem baseada em SRAM para serem programados. Esses FPGAs são programáveis e reprogramáveis no sistema, mas requerem dispositivos de inicialização externos. Por exemplo, dispositivos de memória flash ou EEPROM podem frequentemente carregar conteúdo na SRAM interna que controla o roteamento e a lógica. A abordagem SRAM é baseada em CMOS.

Alternativas mais raras para a abordagem SRAM incluem:

- Fusível: programável de uma vez. Bipolar. Obsoleto.

- Antifuso: programável de uma vez. CMOS. Exemplos: famílias Actel SX e Axcelerator; família Quicklogic Eclipse II.

- PROM: tecnologia de memória somente leitura programável. Uma vez programável por causa da embalagem de plástico. Obsoleto.

- EPROM: tecnologia de memória somente leitura programável apagável. Uma vez programável, mas com janela, pode ser apagado com luz ultravioleta (UV). CMOS.

- EEPROM: eletricamente apagável tecnologia de memória somente leitura programável. Pode ser apagado, mesmo em pacotes de plástico. Alguns, mas nem todos os dispositivos EEPROM podem ser programados no sistema. CMOS.

- Flash: tecnologia EPROM da era flash. Pode ser apagado, mesmo em pacotes de plástico. Alguns, mas nem todos os dispositivos flash podem ser programados no sistema. Normalmente, uma célula flash é menor do que uma célula equivalente EEPROM e é, portanto, menos caro para a fabricação. CMOS. Exemplo: Actel ProASIC family.

Fabricantes

Em 2016, os rivais de longa data da indústria Xilinx (agora parte da AMD) e Altera (agora uma subsidiária da Intel) eram os líderes de mercado de FPGA. Naquela época, eles controlavam quase 90% do mercado.

Tanto a Xilinx (agora AMD) quanto a Altera (agora Intel) fornecem software proprietário de automação de projeto eletrônico para Windows e Linux (ISE/Vivado e Quartus), que permite aos engenheiros projetar, analisar, simular e sintetizar (compilar) seus projetos.

Em março de 2010, a Tabula anunciou sua tecnologia FPGA que usa lógica multiplexada no tempo e interconexão que reivindica economia potencial de custos para aplicativos de alta densidade. Em 24 de março de 2015, Tabula fechou oficialmente.

Em 1º de junho de 2015, a Intel anunciou que adquiriria a Altera por aproximadamente US$ 16,7 bilhões e concluiu a aquisição em 30 de dezembro de 2015.

Em 27 de outubro de 2020, a AMD anunciou que adquiriria a Xilinx e concluiu a aquisição avaliada em cerca de US$ 50 bilhões em fevereiro de 2022.

Outros fabricantes incluem:

- Achronix, fabricando FPGAS baseado em SRAM com velocidade de tecido de 1,5 GHz

- Altium, fornece sistema-on-FPGA hardware-software ambiente de design.

- Efinix oferece FPGAs de pequeno a médio porte. Eles combinam lógica e interconexão de roteamento em uma célula XLR configurável.

- Semicondutores GOWIN, fabricação de pequenos e médios SRAM e FPGAs baseados em Flash. Eles também oferecem substitutos compatíveis para alguns produtos Xilinx, Altera e Lattice.

- Semicondutor Lattice, que fabrica FPGAs de baixa potência baseada em SRAM com configuração integrada flash, instantâneo e reconfiguração ao vivo

- SiliconBlue Technologies, que fornece FPGAs extremamente de baixa potência baseada em SRAM com memória de configuração não volátil integrada opcional; adquirida pela Lattice em 2011

- Microchip:

- Microsemi (anteriormente Actel), produzindo FPGAs antifusos, baseados em flash; adquiridos pela Microchip em 2018

- Atmel, uma segunda fonte de alguns dispositivos compatíveis com Altera; também FPSLIC mencionado acima; adquirido pela Microchip em 2016

- QuickLogic, que fabrica Ultra Low Power Sensor Hubs, extremamente baixa potência, baixa densidade SRAM-based FPGAs, com pontes de exibição MIPI & RGB entradas, MIPI, RGB e LVDS saídas

Aplicativos

Um FPGA pode ser usado para resolver qualquer problema que seja computável. Isso é trivialmente comprovado pelo fato de que FPGAs podem ser usados para implementar um microprocessador flexível, como o Xilinx MicroBlaze ou o Altera Nios II. Sua vantagem reside no fato de serem significativamente mais rápidos para algumas aplicações devido à sua natureza paralela e otimização em termos do número de portas usadas para determinados processos.

Os FPGAs originalmente começaram como concorrentes dos CPLDs para implementar lógica de cola para placas de circuito impresso. À medida que seu tamanho, capacidade e velocidade aumentaram, os FPGAs assumiram funções adicionais a ponto de alguns serem agora comercializados como sistemas completos em chips (SoCs). Particularmente com a introdução de multiplicadores dedicados em arquiteturas FPGA no final dos anos 1990, aplicações que tradicionalmente eram a única reserva de hardware de processador de sinal digital (DSPs) começaram a incorporar FPGAs.

A evolução dos FPGAs tem motivado o aumento da utilização destes dispositivos, cuja arquitetura permite o desenvolvimento de soluções de hardware otimizadas para tarefas complexas, como segmentação de imagens 3D MRI, 3D discreta wavelet transform, reconstrução de imagens tomográficas, ou PET/ Sistemas de ressonância magnética. As soluções desenvolvidas podem executar tarefas de computação intensiva com processamento paralelo, são reprogramáveis dinamicamente e têm um baixo custo, ao mesmo tempo em que atendem aos rígidos requisitos de tempo real associados à imagem médica.

Outra tendência no uso de FPGAs é a aceleração de hardware, onde pode-se usar o FPGA para acelerar certas partes de um algoritmo e compartilhar parte da computação entre o FPGA e um processador genérico. O mecanismo de pesquisa Bing é conhecido por adotar a aceleração FPGA para seu algoritmo de pesquisa em 2014. A partir de 2018, os FPGAs estão tendo um uso crescente como aceleradores de IA, incluindo o chamado "Project Catapult" e para acelerar redes neurais artificiais para aplicações de aprendizado de máquina.

Tradicionalmente, os FPGAs têm sido reservados para aplicações verticais específicas onde o volume de produção é pequeno. Para esses aplicativos de baixo volume, o prêmio que as empresas pagam em custo de hardware por unidade de um chip programável é mais acessível do que os recursos de desenvolvimento gastos na criação de um ASIC. A partir de 2017, novas dinâmicas de custo e desempenho ampliaram o leque de aplicações viáveis.

A empresa Gigabyte Technology criou um cartão i-RAM que usava um Xilinx FPGA, embora um chip personalizado fosse mais barato se feito em grandes quantidades. O FPGA foi escolhido para trazê-lo rapidamente ao mercado e a execução inicial era de apenas 1.000 unidades, tornando um FPGA a melhor escolha. Este dispositivo permite que as pessoas usem a RAM do computador como um disco rígido.

Outros usos para FPGAs incluem:

- Espaço (ou seja, com endurecimento por radiação)

- Módulos de segurança do hardware

Segurança

Os FPGAs têm vantagens e desvantagens em relação aos ASICs ou microprocessadores seguros, no que diz respeito à segurança do hardware. FPGAs' a flexibilidade reduz o risco de modificações maliciosas durante a fabricação. Anteriormente, para muitos FPGAs, o fluxo de bits do projeto era exposto enquanto o FPGA o carregava da memória externa (normalmente a cada inicialização). Todos os principais fornecedores de FPGA agora oferecem um espectro de soluções de segurança para designers, como criptografia e autenticação de fluxo de bits. Por exemplo, Altera e Xilinx oferecem criptografia AES (até 256 bits) para bitstreams armazenados em uma memória flash externa.

Os FPGAs que armazenam sua configuração internamente em memória flash não volátil, como os dispositivos programáveis Microsemi's ProAsic 3 ou Lattice's XP2, não expõem o fluxo de bits e não precisam de criptografia. Além disso, a memória flash para uma tabela de pesquisa fornece proteção contra eventos únicos para aplicações espaciais. Os clientes que desejam uma maior garantia de resistência à adulteração podem usar FPGAs antifuse de gravação única de fornecedores como a Microsemi.

Com seus Stratix 10 FPGAs e SoCs, a Altera introduziu um Secure Device Manager e funções físicas não clonáveis para fornecer altos níveis de proteção contra ataques físicos.

Em 2012, os pesquisadores Sergei Skorobogatov e Christopher Woods demonstraram que alguns FPGAs podem ser vulneráveis a intenções hostis. Eles descobriram que uma vulnerabilidade crítica de backdoor foi fabricada em silício como parte do Actel/Microsemi ProAsic 3, tornando-o vulnerável em muitos níveis, como reprogramação de criptografia e chaves de acesso, acesso a bitstream não criptografado, modificação de recursos de silício de baixo nível e extração de dados de configuração.

Em 2020, uma vulnerabilidade crítica (chamada "Starbleed") foi descoberta em todos os FPGAs da série 7 da Xilinx que tornavam a criptografia de fluxo de bits inútil. Não há solução alternativa. Xilinx não produziu uma revisão de hardware. Dispositivos ultraescala e posteriores, já existentes no mercado na época, não foram afetados.

Tecnologias semelhantes

Historicamente, os FPGAs têm sido mais lentos, menos eficientes em termos de energia e geralmente alcançam menos funcionalidade do que suas contrapartes ASIC fixas. Um estudo de 2006 mostrou que os projetos implementados em FPGAs precisam em média de 40 vezes mais área, consomem 12 vezes mais potência dinâmica e rodam a um terço da velocidade das implementações ASIC correspondentes. Mais recentemente, FPGAs como o Xilinx Virtex-7 ou o Altera Stratix 5 passaram a rivalizar com as soluções ASIC e ASSP correspondentes ("Parte padrão específica do aplicativo", como um chip de interface USB autônomo), fornecendo significativamente uso de energia reduzido, maior velocidade, menor custo de materiais, espaço mínimo de implementação e maiores possibilidades de reconfiguração 'on-the-fly'. Um projeto que incluía de 6 a 10 ASICs agora pode ser obtido usando apenas um FPGA. As vantagens dos FPGAs incluem a capacidade de reprogramar quando já implantado (ou seja, "no campo") para corrigir bugs e geralmente incluem menor tempo de lançamento no mercado e custos de engenharia não recorrentes mais baixos. Os fornecedores também podem seguir um caminho intermediário por meio da prototipagem de FPGA: desenvolvendo seu protótipo de hardware em FPGAs, mas fabricando sua versão final como um ASIC para que não possa mais ser modificado após o projeto ser confirmado. Este também é frequentemente o caso com novos designs de processadores. Alguns FPGAs têm a capacidade de reconfiguração parcial que permite que uma parte do dispositivo seja reprogramada enquanto outras partes continuam em execução.

As principais diferenças entre dispositivos lógicos programáveis complexos (CPLDs) e FPGAs são arquitetônicas. Um CPLD tem uma estrutura comparativamente restritiva que consiste em uma ou mais matrizes lógicas de soma de produtos programáveis alimentando um número relativamente pequeno de registradores com clock. Como resultado, os CPLDs são menos flexíveis, mas têm a vantagem de atrasos de tempo mais previsíveis e uma relação lógica-para-interconexão mais alta. As arquiteturas FPGA, por outro lado, são dominadas pela interconexão. Isso os torna muito mais flexíveis (em termos da variedade de designs que são práticos para implementação neles), mas também muito mais complexos de projetar ou, pelo menos, exigem um software de automação de design eletrônico (EDA) mais complexo. Na prática, a distinção entre FPGAs e CPLDs geralmente é de tamanho, pois os FPGAs geralmente são muito maiores em termos de recursos do que os CPLDs. Normalmente, apenas FPGAs contêm funções incorporadas mais complexas, como somadores, multiplicadores, memória e serializador/desserializador. Outra distinção comum é que os CPLDs contêm memória flash incorporada para armazenar sua configuração, enquanto os FPGAs geralmente requerem memória externa não volátil (mas nem sempre). Quando um projeto requer ativação instantânea simples (a lógica já está configurada na inicialização), os CPLDs geralmente são preferidos. Para a maioria das outras aplicações, os FPGAs são geralmente preferidos. Às vezes, CPLDs e FPGAs são usados em um único projeto de sistema. Nesses projetos, os CPLDs geralmente executam funções lógicas de cola e são responsáveis pela "inicialização" o FPGA, bem como controlar a reinicialização e a sequência de inicialização da placa de circuito completa. Portanto, dependendo da aplicação, pode ser sensato usar FPGAs e CPLDs em um único projeto.

Contenido relacionado

MU

Ciclone (linguagem de programação)

Lynx (linguagem de programação)

Kevin Warwick

Computador Atanasoff-Berry