DDR SDRAM

Double Data Rate Synchronous Dynamic Random-Access Memory (DDR SDRAM) é uma classe de memória síncrona de acesso aleatório dinâmico (SDRAM) de taxa de dados dupla (DDR) circuitos integrados usados em computadores. DDR SDRAM, também chamado retroativamente de DDR1 SDRAM, foi substituído por DDR2 SDRAM, DDR3 SDRAM, DDR4 SDRAM e DDR5 SDRAM. Nenhum de seus sucessores é compatível com DDR1 SDRAM, o que significa que os módulos de memória DDR2, DDR3, DDR4 e DDR5 não funcionarão em placas-mãe equipadas com DDR1 e vice-versa.

Em comparação com a SDRAM de taxa de dados única (SDR), a interface DDR SDRAM possibilita taxas de transferência mais altas por meio de um controle mais estrito do tempo dos dados elétricos e sinais de relógio. As implementações geralmente precisam usar esquemas como loops de bloqueio de fase e autocalibração para alcançar a precisão de tempo necessária. A interface usa bombeamento duplo (transferência de dados nas bordas ascendente e descendente do sinal de clock) para dobrar a largura de banda do barramento de dados sem um aumento correspondente na frequência do clock. Uma vantagem de manter a frequência do clock baixa é que isso reduz os requisitos de integridade do sinal na placa de circuito que conecta a memória ao controlador. O nome "taxa de dados dupla" refere-se ao fato de que um DDR SDRAM com uma certa frequência de clock atinge quase o dobro da largura de banda de um SDR SDRAM rodando na mesma frequência de clock, devido a esse bombeamento duplo.

Com dados sendo transferidos 64 bits por vez, DDR SDRAM fornece uma taxa de transferência (em bytes/s) de (taxa de clock do barramento de memória) × 2 (para taxa dupla) × 64 (número de bits transferidos) / 8 (número de bits/byte). Assim, com uma frequência de barramento de 100 MHz, DDR SDRAM oferece uma taxa de transferência máxima de 1600 MB/s.

História

No final da década de 1980, a IBM construiu DRAMs usando um recurso de clock de borda dupla e apresentou seus resultados na Convenção Internacional de Circuitos de Estado Sólido em 1990.

A Samsung demonstrou o primeiro protótipo de memória DDR em 1997 e lançou o primeiro chip DDR SDRAM comercial (64 Mbit) em junho de 1998, seguido logo depois pela Hyundai Electronics (agora SK Hynix) no mesmo ano. O desenvolvimento do DDR começou em 1996, antes de sua especificação ser finalizada pelo JEDEC em junho de 2000 (JESD79). JEDEC estabeleceu padrões para taxas de dados de DDR SDRAM, divididos em duas partes. A primeira especificação é para chips de memória e a segunda é para módulos de memória. A primeira placa-mãe de PC de varejo usando DDR SDRAM foi lançada em agosto de 2000.

Especificação

Módulos

Para aumentar a capacidade de memória e largura de banda, os chips são combinados em um módulo. Por exemplo, o barramento de dados de 64 bits para DIMM requer oito chips de 8 bits, endereçados em paralelo. Múltiplos chips com linhas de endereço comuns são chamados de classificação de memória. O termo foi introduzido para evitar confusão com linhas e bancos internos do chip. Um módulo de memória pode ter mais de uma classificação. O termo lados também seria confuso porque sugere incorretamente o posicionamento físico dos chips no módulo. Todos os ranks estão conectados ao mesmo barramento de memória (endereço + dados). O sinal de seleção de chip é usado para emitir comandos para classificação específica.

Adicionar módulos ao barramento de memória único cria carga elétrica adicional em seus drivers. Para mitigar a queda na taxa de sinalização do barramento resultante e superar o gargalo de memória, novos chipsets empregam a arquitetura multicanal.

| Nome | Chip | Ônibus | Tempos | Tensão (V) | ||||||

|---|---|---|---|---|---|---|---|---|---|---|

| Padrão | Tipo | Módulo | Taxa de relógio (MHz) | Tempo de ciclo (ns) | Taxa de relógio (MHz) | Taxa de transferência (MT/s) | Largura de banda (MB/s) | CL-TRCD- TRP | Latência CAS (ns) | |

| DDR-200 | PC-1600 | 100. | 10. | 100. | 200 | 1600 | 2-2-2-2 | 20. | 2.5±0,2 | |

| DDR-266 | PC-2100 | 133+1?3 | 7.5 | 133+1?3 | 266.67 | 2133+1?3 | 2.5-3-3 | 18.75 | ||

| DDR-333 | PC-2700 | 166+2?3 | 6 | 166+2?3 | 333+1?3 | 2666+2?3 | 2.5-3-3 | 15 | ||

| DDR-400 | A | PC-3200 | 200 | 5 | 200 | 400 | 3200 | 2.5-3-3 | 12,5 | 2.6±0,0 |

| B | 3-3-3-3 | 15 | ||||||||

| C | 3-4-4-4 | 15 | ||||||||

Nota: Todos os listados acima são especificados por JEDEC como JESD79F. Todas as taxas de dados de RAM entre ou acima dessas especificações listadas não são padronizadas pelo JEDEC – geralmente são simplesmente otimizações do fabricante usando tolerância mais rígida ou chips com sobretensão. Os tamanhos dos pacotes nos quais o DDR SDRAM é fabricado também são padronizados pela JEDEC.

Não há diferença arquitetônica entre os módulos DDR SDRAM. Em vez disso, os módulos são projetados para rodar em diferentes frequências de clock: por exemplo, um módulo PC-1600 é projetado para rodar em 100 MHz, e um PC-2100 é projetado para rodar em 133 MHz. A velocidade de clock de um módulo designa a taxa de dados na qual é garantido o desempenho, portanto, é garantido que ele será executado em menor (underclocking) e possivelmente poderá ser executado em maior (overclocking) do que aquelas para as quais foi feito.

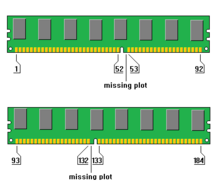

Módulos SDRAM DDR para computadores de mesa, módulos de memória em linha duplos (DIMMs), têm 184 pinos (em oposição a 168 pinos em SDRAM ou 240 pinos em DDR2 SDRAM) e podem ser diferenciados de SDRAM DIMMs pelo número de entalhes (DDR SDRAM tem um, SDRAM tem dois). DDR SDRAM para notebooks, SO-DIMMs, tem 200 pinos, que é o mesmo número de pinos que DDR2 SO-DIMMs. Essas duas especificações são entalhadas de maneira muito semelhante e deve-se tomar cuidado durante a inserção se não houver certeza de uma correspondência correta. A maioria dos DDR SDRAM opera a uma voltagem de 2,5 V, em comparação com 3,3 V para SDRAM. Isso pode reduzir significativamente o consumo de energia. Chips e módulos com padrão DDR-400/PC-3200 possuem tensão nominal de 2,6 V.

O Padrão JEDEC No. 21–C define três possíveis tensões de operação para DDR de 184 pinos, conforme identificado pela posição do entalhe da chave em relação à sua linha central. A página 4.5.10-7 define 2,5 V (esquerda), 1,8 V (centro), TBD (direita), enquanto a página 4.20.5–40 indica 3,3 V para a posição do entalhe direito. A orientação do módulo para determinar a posição do entalhe da chave é com 52 posições de contato à esquerda e 40 posições de contato à direita.

Aumentar levemente a tensão de operação pode aumentar a velocidade máxima, ao custo de maior dissipação de energia e aquecimento, e com risco de mau funcionamento ou danos.

- Capacidade

- Número de dispositivos DRAM

- O número de fichas é um múltiplo de 8 para módulos não-ECC e um múltiplo de 9 para módulos ECC. Chips podem ocupar um lado (único lado) ou ambos os lados (dupla face) do módulo. O número máximo de fichas por módulo DDR é 36 (9×4) para ECC e 32 (8x4) para não ECC.

- ECC vs não ECC

- Módulos que têm código de correção de erros são rotulados como ECC. Módulos sem código de correção de erros são rotulados não ECC.

- Tempos

- Latência CAS (CL), tempo do ciclo do relógio (tCK), tempo de ciclo de linha (t)RC), tempo de ciclo de linha de atualização (t)RFC), tempo ativo da linha (t)RAS).

- Buffering

- Registado (ou tampão) vs não modificado.

- Embalagem

- Normalmente DIMM ou SO-DIMM.

- Consumo de energia

- Um teste com DDR e DDR2 RAM em 2005 descobriu que o consumo médio de energia parecia ser da ordem de 1-3 W por módulo 512 MB; isso aumenta com a taxa de clock e quando em uso em vez de ocioso. Um fabricante produziu calculadoras para estimar o poder usado por vários tipos de RAM.

As características do módulo e do chip estão inerentemente ligadas.

A capacidade total do módulo é um produto da capacidade de um chip e do número de chips. Os módulos ECC o multiplicam por 8⁄9 porque eles usam 1 bit por byte (8 bits) para correção de erros. Um módulo de qualquer tamanho específico pode, portanto, ser montado a partir de 32 chips pequenos (36 para memória ECC) ou 16(18) ou 8(9) maiores.

A largura do barramento de memória DDR por canal é de 64 bits (72 para memória ECC). A largura total de bits do módulo é um produto de bits por chip e número de chips. Também é igual ao número de fileiras (linhas) multiplicado pela largura do barramento de memória DDR. Consequentemente, um módulo com maior número de chips ou que utilize chips ×8 em vez de ×4 terá mais ranks.

| Tamanho do módulo (GB) | Número de fichas | Tamanho do chip (Mbit) | Organização de chips | Número de fileiras |

|---|---|---|---|---|

| 1 | 36 | 256. | 64M × 4 | 2 |

| 1 | 18. | 512 | 64M × 8 | 2 |

| 1 | 18. | 512 | 128M × 4 | 1 |

Este exemplo compara diferentes módulos de memória de servidor do mundo real com um tamanho comum de 1 GB. Definitivamente, deve-se ter cuidado ao comprar módulos de memória de 1 GB, porque todas essas variações podem ser vendidas em uma posição de preço sem informar se são ×4 ou ×8, de classificação única ou dupla.

Há uma crença comum de que o número de fileiras de módulos é igual ao número de lados. Como os dados acima mostram, isso não é verdade. Também é possível encontrar módulos de 2 lados/1 fileira. Pode-se até pensar em um módulo de memória de 1 lado/2 fileiras com 16 (18) chips em um único lado × 8 cada, mas é improvável que tal módulo tenha sido produzido.

Características do chip

- Densidade de DRAM

- O tamanho do chip é medido em megabits. A maioria das placas-mãe reconhece apenas 1 GB de módulos se eles contêm 64M × 8 fichas (baixa densidade). Se 128M × 4 (alta densidade) 1 GB módulos são usados, eles provavelmente não funcionarão. O padrão JEDEC permite 128M × 4 apenas para módulos registrados projetados especificamente para servidores, mas alguns fabricantes genéricos não cumprem.

- Organização

- A notação como 64M × 4 significa que a matriz de memória tem 64 milhões (o produto de bancos x linhas x colunas) Locais de armazenamento de 4 bits. Há × 4. e × Chips DDR. O × chips permitem o uso de recursos avançados de correção de erros como Chipkill, limpeza de memória e SDDC Intel em ambientes de servidor, enquanto o × 8 e × chips são um pouco menos caros. x8 chips são usados principalmente em desktops / notebooks, mas estão fazendo entrada no mercado do servidor. Existem normalmente 4 bancos e apenas uma linha pode ser ativa em cada banco.

Especificação SDRAM de taxa de dados dupla (DDR)

Da cédula JCB-99-70 e modificada por várias outras cédulas do Conselho, formuladas sob o conhecimento do Comitê JC-42.3 sobre DRAM Parametrics.

Registro de revisão padrão nº 79:

- Lançamento 1, Junho 2000

- Lançamento 2, Maio 2002

- Lançamento C, março de 2003 – JEDEC Standard No. 79C.

"Este padrão abrangente define todos os aspectos necessários de SDRAMs DDR de 64Mb a 1Gb com interfaces de dados X4/X8/X16, incluindo recursos, funcionalidade, parametria CA e CC, pacotes e atribuições de pinos. Este escopo será subsequentemente expandido para se aplicar formalmente a dispositivos x32 e também a dispositivos de maior densidade."

Organização

PC3200 é DDR SDRAM projetado para operar a 200 MHz usando chips DDR-400 com uma largura de banda de 3.200 MB/s. Como a memória do PC3200 transfere dados nas bordas de clock ascendente e descendente, sua taxa de clock efetiva é de 400 MHz.

Os módulos PC3200 não ECC de 1 GB geralmente são feitos com 16 chips de 512 Mbit, 8 de cada lado (512 Mbits × 16 chips) / (8 bits (por byte)) = 1.024 MB. Os chips individuais que compõem um módulo de memória de 1 GB geralmente são organizados como 226 palavras de 8 bits, comumente expressas como 64M×8. A memória fabricada dessa maneira é RAM de baixa densidade e geralmente é compatível com qualquer placa-mãe que especifique a memória PC3200 DDR-400.

Gerações

DDR (DDR1) foi substituído por DDR2 SDRAM, que teve modificações para maior frequência de clock e novamente dobrou a taxa de transferência, mas opera com o mesmo princípio do DDR. Competindo com DDR2 estava Rambus XDR DRAM. DDR2 dominou devido a fatores de custo e suporte. DDR2 por sua vez foi substituído por SDRAM DDR3, que oferecia maior desempenho para maiores velocidades de barramento e novos recursos. O DDR3 foi substituído pelo DDR4 SDRAM, que foi produzido pela primeira vez em 2011 e cujos padrões ainda estavam em fluxo (2012) com mudanças arquitetônicas significativas.

A profundidade do buffer de pré-busca do DDR é de 2 (bits), enquanto o DDR2 usa 4. Embora as taxas de clock efetivas do DDR2 sejam maiores que as do DDR, o desempenho geral não foi maior nas primeiras implementações, principalmente devido ao alto latências dos primeiros módulos DDR2. O DDR2 começou a ser efetivo no final de 2004, com a disponibilização de módulos com latências menores.

Os fabricantes de memória declararam que era impraticável produzir em massa memória DDR1 com taxas de transferência efetivas superiores a 400 MHz (ou seja, 400 MT/s e 200 MHz de clock externo) devido a limitações internas de velocidade. O DDR2 começa onde o DDR1 termina, utilizando taxas de clock interno semelhantes ao DDR1, mas está disponível em taxas de transferência efetivas de 400 MHz e superiores. Os avanços do DDR3 ampliaram a capacidade de preservar as taxas de clock interno, ao mesmo tempo em que forneciam taxas de transferência efetivas mais altas, dobrando novamente a profundidade de pré-busca.

O DDR4 SDRAM é uma memória dinâmica de acesso aleatório de alta velocidade configurada internamente como 16 bancos, 4 grupos de bancos com 4 bancos para cada grupo de bancos para ×4/×8 e 8 bancos, 2 grupos de bancos com 4 bancos para cada grupo de banco para ×16 DRAM. O SDRAM DDR4 usa uma arquitetura de pré-busca de 8n para obter uma operação de alta velocidade. A arquitetura de pré-busca 8n é combinada com uma interface projetada para transferir duas palavras de dados por ciclo de clock nos pinos de E/S. Uma única operação de leitura ou gravação para o SDRAM DDR4 consiste em uma única transferência de dados de 4 relógios de 8n bits no núcleo DRAM interno e 8 n bits correspondentes -transferências de dados de meio ciclo de clock nos pinos de E/S.

A RDRAM era uma alternativa particularmente cara à DDR SDRAM, e a maioria dos fabricantes abandonou o suporte de seus chipsets. Os preços da memória DDR1 aumentaram substancialmente desde o segundo trimestre de 2008, enquanto os preços da DDR2 diminuíram. Em janeiro de 2009, 1 GB DDR1 era 2 a 3 vezes mais caro que 1 GB DDR2.

| Nome | Lançamento ano | Chip | Ônibus | Tensão (V) | Pins | |||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Gente | Padrão | Taxa de relógio (MHz) | Tempo de ciclo (ns) | Pre-fetch | Taxa de relógio (MHz) | Taxa de transferência (MT/s) | Largura de banda (MB/s) | DIMM | SO-DIMM | Micro-DIMM | ||

| DDR | DDR-200 | 1998 | 100. | 10. | 2 | 100. | 200 | 1600 | 2.5. | 184 | 200 | 172 |

| DDR-266 | 133 | 7.5 | 133 | 266 | 2133+1?3 | |||||||

| DDR-333 | 166+2?3 | 6 | 166+2?3 | 333 | 2666+2?3 | |||||||

| DDR-400 | 200 | 5 | 200 | 400 | 3200 | 2. | ||||||

| DDR2 | DDR2-400 | 2003 | 100. | 10. | 4 | 200 | 400 | 3200 | 1. | 240 | 200 | 214 |

| DDR2-533 | 133+1?3 | 7.5 | 266+2?3 | 533+1?3 | 4266+2?3 | |||||||

| DDR2-667 | 166+2?3 | 6 | 333+1?3 | 666+2?3 | 53+1?3 | |||||||

| DDR2-800 | 200 | 5 | 400 | 800 | 6400 | |||||||

| DDR2-1066 | 266+2?3 | 3.75 | 533+1?3 | 1066+2?3 | 8533+1?3 | |||||||

| DDR3 | DDR3-800 | 2007 | 100. | 10. | 8 | 400 | 800 | 6400 | 1.5/1.35 | 240 | 204 | 214 |

| DDR3-1066 | 133+1?3 | 7.5 | 533+1?3 | 1066+2?3 | 8533+1?3 | |||||||

| DDR3-1333 | 166+2?3 | 6 | 666+2?3 | 1333+1?3 | 10600+2?3 | |||||||

| DDR3-1600 | 200 | 5 | 800 | 1600 | 12800 | |||||||

| DDR3-1866 | 233+1?3 | 4.29 | 933+1?3 | 1866+2?3 | 14933+1?3 | |||||||

| DDR3-2133 | 266+2?3 | 3.75 | 1066+2?3 | 2133+1?3 | 17066+2?3 | |||||||

| DDR4 | DDR4-1600 | 2014 | 200 | 5 | 8 | 800 | 1600 | 12800 | 1.2/1.05 | 288 | 260 | - Não. |

| DDR4-1866 | 233+1?3 | 4.29 | 933+1?3 | 1866+2?3 | 14933+1?3 | |||||||

| DDR4-2133 | 266+2?3 | 3.75 | 1066+2?3 | 2133+1?3 | 17066+2?3 | |||||||

| DDR4-2400 | 300 | 3+1?3 | 1200 | 24:00 | 19200 | |||||||

| DDR4-2666 | 333+1?3 | 3 | 1333+1?3 | 2666+2?3 | 21333+1?3 | |||||||

| DDR4-2933 | 366+2?3 | 2.73 | 1466+2?3 | 2933+1?3 | 23466+2?3 | |||||||

| DDR4-3200 | 400 | 2.5. | 1600 | 3200 | 25600 | |||||||

| DDR5 | DDR5-3200 | 2020 | 200 | 5 | 16. | 1600 | 3200 | 25600 | 1.1.1. | 288 | 262 | |

| DDR5-3600 | 225 | 4.44 | 1800 | 3600 | 28800 | |||||||

| DDR5-4000 | 250 | 4 | 2000 | 4000 | 3-2000 | |||||||

| DDR5-4800 | 300 | 3+1?3 | 24:00 | 4800 | 38400 | |||||||

| DDR5-5000 | 312+1?2 | 3.2. | 2500 | 5000. | 40000 | |||||||

| DDR5-5120 | 320 | 3+1?8 | 2560 | 5120 | 40960 | |||||||

| DDR5-5333 | 333+1?3 | 3 | 2666+2?3 | 53+1?3 | 4266+2?3 | |||||||

| DDR5-5600 | 350 | 2.86 | 2800 | 5600 | 44800 | |||||||

| DDR5-6400 | 400 | 2.5. | 3200 | 6400 | 51200 | |||||||

| DDR5-7200 | 450 | 2.2.2. | 3600 | 7200 | 57600 | |||||||

DDR móvel

MDDR é um acrônimo que algumas empresas usam para Mobile DDR SDRAM, um tipo de memória usada em alguns dispositivos eletrônicos portáteis, como telefones celulares, handhelds e reprodutores de áudio digital. Por meio de técnicas que incluem fornecimento de tensão reduzida e opções avançadas de atualização, o Mobile DDR pode alcançar maior eficiência de energia.

Contenido relacionado

Processamento de sinal de áudio

DARPA

Dhrystone